# 令和4年度重要技術管理体制強化事業 (半導体製造後工程及び実装工程に係る 重要技術動向調査)報告書

株式会社野村総合研究所 コンサルティング事業本部 グローバル製造業コンサルティング部

2023年2月28日

# 目次 (1/2)

| ■ 本報告書の目的・内容・検討対象範囲                            | P.3  |

|------------------------------------------------|------|

| ■ 本報告書の調査方法・期間等                                | P.5  |

| ■ 概要                                           | P.7  |

| ■ 第1章:半導体業界構造の概観とキープレイヤ                        | P.1  |

| 1-1. 業界構造俯瞰                                    | P.13 |

| 1-2. 半導体業界のキープレイヤ                              | P.15 |

| ■ 第2章:後工程プロセスの現状及び将来動向                         | P.1  |

| 2-1. 後工程プロセスの現状及び関連市場動向                        | P.19 |

| 2-2. 後工程先端プロセスの現状                              | P.22 |

| 1) 先端パッケージ基板                                   | P.23 |

| 2) 先端企業動向                                      | P.25 |

| 3) 先端プロセス                                      | P.30 |

| 2-3. 後工程プロセスの将来動向                              | P.40 |

| 1) 将来技術動向                                      | P.4  |

| 2) 技術開発動向                                      | P.54 |

| 3) 先進事例                                        | P.58 |

| <ul><li>基地局/データセンター用ハイエンドデバイス (スイッチ)</li></ul> | P.59 |

| <ul><li>シリコンフォトニクス</li></ul>                   | P.60 |

| • 量子デバイス                                       | P.61 |

| <ul><li>パワーデバイスにおける熱マネージメント</li></ul>          | P.62 |

# 目次 (2/2)

| ■ 第3章:後工程材料・装置の現状及び将来動向       | P.64  |

|-------------------------------|-------|

| 3-1. 後工程材料・装置の現状及び関連市場動向      | P.64  |

| 1) 半導体後工程・パッケージ主要材料           | P.65  |

| 2) パッケージ基板材料                  | P.67  |

| 3) 半導体後工程関連装置                 | P.69  |

| 4) 競争状况                       | P.71  |

| 3-2. 後工程材料・装置の現状              | P.74  |

| 1) 半導体後工程・パッケージ主要材料           | P. 74 |

| 2) パッケージ基板材料                  | P. 82 |

| 3) 半導体後工程製造装置                 | P. 84 |

| 3-3.後工程材料・装置の将来動向             | P.89  |

| 1) 半導体後工程・パッケージ主要材料           | P.90  |

| 2) パッケージ基板材料                  | P.93  |

| 3) 半導体後工程製造装置                 | P.96  |

| ■ 第4章:日本の産業競争力評価及び競争力強化のための示唆 | P.103 |

| 4-1. 半導体後工程における重要技術と競争力ポジション  | P.104 |

| 4-2. 産業競争力強化のための要点・示唆         | P.107 |

# 本報告書の目的・内容・検討対象範囲

## ■ 事業名

● 令和4年度重要技術管理体制強化事業(半導体製造後工程及び実装工程に係る重要技術動向調査)

#### ■ 事業目的

- 近年、安全保障分野のすそ野は経済・技術分野に急速に拡大。また、感染症の世界的拡大による、サプライチェーンの特定国への依存による 脆弱性がもたらすリスクが浮き彫りになるなど、経済安全保障の重要性がこれまで以上に高まっている。

- 半導体の性能向上に対し、前工程における微細化技術等の向上は不可欠であるが、昨今では、CPUやメモリ、画像処理GPU、通信モデム等の機能をひとつのチップとするSoC(System on Chip)や複数チップをまとめてパッケージするSiP(System in Package)等の後工程以降での技術による性能向上も重要視されている。本調査では、主に半導体製造における後工程及び実装工程に係る主要な内外の技術開発動向等を把握することによって、我が国の産業競争力の維持を図るために役立つ基礎資料を得ることを目的として実施するものである。

#### ■ 事業内容

- ①主に後工程及び実装工程に係る重要技術等の動向調査

- ②上記①で抽出した重要技術について、コアな要素技術等に係る動向調査

- ③上記①②の調査を通じた本分野における我が国の産業競争力等の評価

- ④上記より得られた産業競争力上の示唆

# ■ 対象範囲

● 本報告書でのカバー範囲は、パッケージ基板・再配線層形成及びパッケージ基板への実装工程を含む、半導体組立工程全般の技術領域であり、 パッケージ製造後のプリント基板等への実装工程は、対象としない。そのため、本報告書タイトルにある「後工程及び実装工程」を本報告書内では、 後工程としてシンプルに記述するものとする。

#### 対象範囲 デバイス PWB基板 前工程 後工程・チップレット実装工程 設計 実装工程 組立工程 (パッケージ実装) モール ディング 酸化•拡散 露光 エッチング 成膜 CMP グラインディング 〉ダイシング ボンディング マウンタ リフロー パッケージ基板・配線層形成 検査 露光 エッチング めっき 配線形成 テスト Copyright (C) Nomura Research Institute, Ltd. All rights reserved.

# 本報告書の目的・内容・検討対象範囲

# ■調査対象

## 後工程プロセスの動向調査

調査対象工程 11工程 パッケージ基板 SAPプロセス パッケージ基板 MSAPプロセス シリコンブリッジプロセス 3Dスタッキングプロセス 微細再配線層付FO-WLPプロセス チップオンウェハSoCプロセス シリコンブリッジSoCプロセス シリコンフォトニクス 量子デバイス パワーデバイス イメージセンサ

# コア要素技術としての装置・材料の市場動向

1) 半導体後工程・パッケージ主要材料 13品目 バックグラインドテープ ダイシングテープ ダイボンディングフィルム 半導体封止材 モールド・アンダーフィル 一次実装用アンダーフィル リードフレーム用条材 ボンディングワイヤ はんだボール ソルダーペースト シンタリングペースト(加圧) シンタリングペースト(非加圧)

2) 半導体パッケージ基板関連材料 8品目

低誘電対応ガラスクロス

層間絶縁フィルム ソルダーレジストフィルム 再配線材料 バッファーコート 低誘電対応ガラスクロス ガラス基材銅張積層板 (パッケージ用) ドライフィルムレジスト 銅めっき

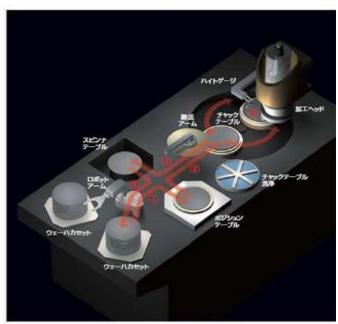

3) 半導体後工程製造装置 8品目 ダイシング装置 ダイ/ チップボンディング装置 オートモールドプレス

ステッパ

バックグラインダ装置 ワイヤボンディング装置 バンプ形成装置 レーザー加工機

## コア要素技術としての装置・材料の技術動向

現状 調査対象 16 品目 バックグラインドテープ ダイシングテープ ダイボンディングフィルム 半導体封止材 OFNリードフレーム モールド・アンダーフィル 一次実装用アンダーフィル ボンディングワイヤ めっき パッケージ基板用銅張積層板 ソルダーレジスト パッケージ基板用露光装置 レーザー加工機 ボンディング装置 バックグラインダ装置 モールディング装置

将来 調査対象 8品目

Thermal Interface Material アンダーフィル 層間絶縁フィルム 再配線材料 パッケージ基板用露光装置 ハイブリッドボンディング装置 CMP装置 ダイシング装置

#### ■ 前提条件

● 為替レート:本報告書で、現地通貨より日本円に関する際に は、以下の平均為替レートを使用。 なお、出所基で円換算・ドル換算したものについては、出所に 従う。

#### 為替レート

|            | 2020 | 2021         | 2022 | 2030 |  |

|------------|------|--------------|------|------|--|

| 円/US\$     | 107円 | 110円         | 129円 | 130円 |  |

| ユーロ/US\$   | -    | 0.85ユーロ      |      | -    |  |

| 中国元/US\$   | -    | 6.45中国元 -    |      | -    |  |

| 韓国ウォン/US\$ | -    | 1,144韓国ウォン - |      | -    |  |

| 台湾\$/US\$  | -    | 27.95台湾\$ -  |      | -    |  |

# 報告書の調査方法・期間等

#### ■ 調査項目

- ①主に後工程及び実装工程に係る重要技術等の動向調査

- ②上記①で抽出した重要技術について、コアな要素技術等に係る 動向調查

- ③上記①②の調査を通じた本分野における我が国の産業競争力等 の評価

- ④上記より得られた産業競争力上の示唆

#### ■ 調査期間

● 2022年12月-2023年2月

#### ■ 調査担当者

- 岸本 降正(プロジェクトリーダ)

- 中條 義希 (メンバー)

- 書間 敏慎 (アドバイザー)

- 隆之(プロジェクトマネージャ) 中川

#### ■ 調査方法

#### ● 第1章の調査方法

- 入手可能な業界団体等の統計より市場規模を把握

- WSTS (World Semiconductor Trade Statistics)

- SEMI (Semiconductor Equipment and Materials International) プレスリリース

- 各社業績については、商用データベースでの一次 スクリーニングの後、各社開示情報及びHPでの開示 情報を基に業績を把握。

#### ● 第2章、第3章の調査方法

- 対象技術については、NRIリスティング候補について 経済産業省と相談の上、対象技術を選定。

- 各プロセスについては、有力企業のHP、学会での発表 資料等並びに、2022年JEITA実装ロードマップなどを 参考にプロセスの概要を記述。

- プロセスについては、デバイスメーカ、装置、材料メーカ等 のヒアリング。

- レポート記載内容について、JEITAロードマップ委員会より 内容の確認。

- 市場予測については、富士経済グループ、グローバル ネット等の調査レポートを基に定量評価し、同調査会社 等で不足するものについてはNRIがトレンド予測。

- 日本のシェアは、富士経済グループ、グローバルネット等 の調査レポートで日本に本社を置く企業のシェアを合算 し、日本企業のシェアとした。

### ● 第4章:日本の産業競争力評価及び競争力強化のための 示唆

上記、1-3章の調査の過程で得られた知見をベースに 取りまとめ。

# 本報告書で使用している略称

| 略称                               | 正式名称                                        |  |  |

|----------------------------------|---------------------------------------------|--|--|

| BGA                              | Ball Grid Array                             |  |  |

| CCL                              | Copper Clad Laminate                        |  |  |

| CIS                              | Complementary Metal Oxide                   |  |  |

| CIS                              | Semiconductor Image Sensor                  |  |  |

| CMP                              | Chemical Mechanical Polishing               |  |  |

| COF                              | Chip on Film                                |  |  |

| CoWoS                            | Chip on Wafer on Substrate                  |  |  |

| CSP                              | Chip Size Package                           |  |  |

| СТЕ                              | Coefficient of Thermal Expansion<br>(熱膨張係数) |  |  |

| DBG                              | Dicing Before Grinding                      |  |  |

| Df                               | Dissipation Factor (誘電正接)                   |  |  |

| Dk                               | Dielektrizitäts Konstante (誘電率)             |  |  |

| DP                               | Dry Polishing                               |  |  |

| EUV                              | Extreme Ultra Violet                        |  |  |

| eWLB embedded Wafer Level Ball g |                                             |  |  |

| FBGA                             | Fine pitch Ball Grid Array                  |  |  |

| FC                               | Flip Chip                                   |  |  |

| FET                              | Field Effect Transistor                     |  |  |

| FI-WLP                           | Fan In Wafer Level Package                  |  |  |

| FO-WLP                           | Fan Out Wafer Level Package                 |  |  |

| GAA                              | Gate All Around z                           |  |  |

| НВМ                              | High Bandwidth Memory                       |  |  |

| HPC                              | High Performance Computing                  |  |  |

| IGBT                             | Insultated Gate Bipolar Transistor          |  |  |

| 略称   | 正式名称                           |  |

|------|--------------------------------|--|

| InFO | Integrated Fan Out             |  |

| IPD  | Integrated Passive Device      |  |

| L/S  | Line/Space                     |  |

| MOS  | Metal Oxide Semiconductor      |  |

| MSAP | Modified Semi Additive Process |  |

| NGL  | Next Generation Lithography    |  |

| PLP  | Panel Level Package            |  |

| PoP  | Package on Package             |  |

| QFN  | Quad Flat No-leads Package     |  |

| QFP  | Quad Flat Package              |  |

| RDL  | Re Distribution Layer          |  |

| RF   | Radio Frequency                |  |

| SAP  | Semi Additive Process          |  |

| SoC  | System on Chip                 |  |

| TIM  | Thermal Interface Material     |  |

| TSV  | Through-Silicon Via            |  |

| TIV  | Through InFO Via               |  |

| UBM  | Under Bump Metallurgy          |  |

| OSAT | Outsourced Semiconductor       |  |

|      | Assembly and Test              |  |

| WLAN | Wireless Local Area Network    |  |

| WLP  | Wafer Level Package            |  |

| 企業名略称                                          | 正式名称                                             |  |

|------------------------------------------------|--------------------------------------------------|--|

| AMAT                                           | Applied Materials, Inc.                          |  |

| AMD                                            | Advanced Micro Devices                           |  |

| Amkor                                          | Amkor Technology, Inc.                           |  |

| ASE                                            | Advanced Semiconductor                           |  |

| ASE                                            | Engineering                                      |  |

| ASMPT                                          | ASMPT Ltd                                        |  |

| Cisco                                          | Cisco Systems                                    |  |

| DNP                                            | 大日本印刷株式会社                                        |  |

| Infineon                                       | Infineon Technologies                            |  |

| JCET Jiangsu Changjiang Electronics Technology |                                                  |  |

| KLA                                            | KLA Corporation                                  |  |

| Lam                                            | Lam Research Corporation                         |  |

| Micron                                         | Micron Technology                                |  |

| NXP                                            | NXP Semiconductors NV                            |  |

| SEMCO                                          | Samsung Electro-Mechanics                        |  |

| SMIC                                           | Semiconductor Manufacturing                      |  |

|                                                | International Corporation                        |  |

| TEL                                            | 東京エレクトロン株式会社                                     |  |

| TI                                             | Texas Instruments Inc                            |  |

| TSMC                                           | Taiwan Semiconductor                             |  |

| 151116                                         | Manufacturing Company                            |  |

| UMC                                            | United Microelectronics                          |  |

|                                                | Company                                          |  |

| Unimicron                                      | Unimicron Technology                             |  |

| VIS                                            | Vanguard International Semiconductor Corporation |  |

| SPIL                                           | Siliconware Precision Industries                 |  |

| 芝メカ                                            | 芝浦メカトロニクス株式会社                                    |  |

| ウシオ                                            | ウシオ電機株式会社                                        |  |

# 概要

第1章 半導体業界構造の概観とキープレイヤ

第2章 後工程プロセスの現状及び将来動向

第3章 後工程材料・装置の現状及び将来動向

第4章 日本の産業競争力評価及び競争力強化のための視点

# 第1章 半導体業界構造の概観とキープレイヤ

# 成長する半導体市場

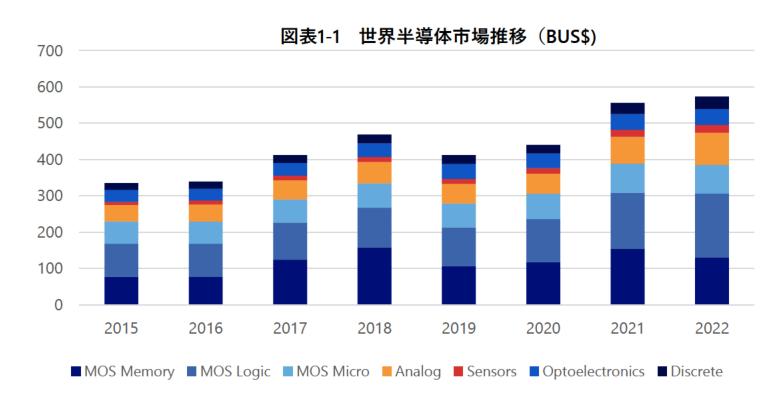

● 半導体市場は、シクリカルに変動しつつも高成長を遂げてきた市場であり、2015年以降、景気変動で変動しつつも年平均 7.9%で成長し続けている。2021年には対前年比26%成長し555.9BUS\$に成長、2022年の下期には在宅特需が一巡し、 世界的インフレ、中国のロックダウンやロシアのウクライナ侵攻の長期化などの影響で個人向け電子機器の消費が落ち込み、 減速基調にあるものの、573.5BUS\$とプラス成長。

## 半導体産業構造俯瞰

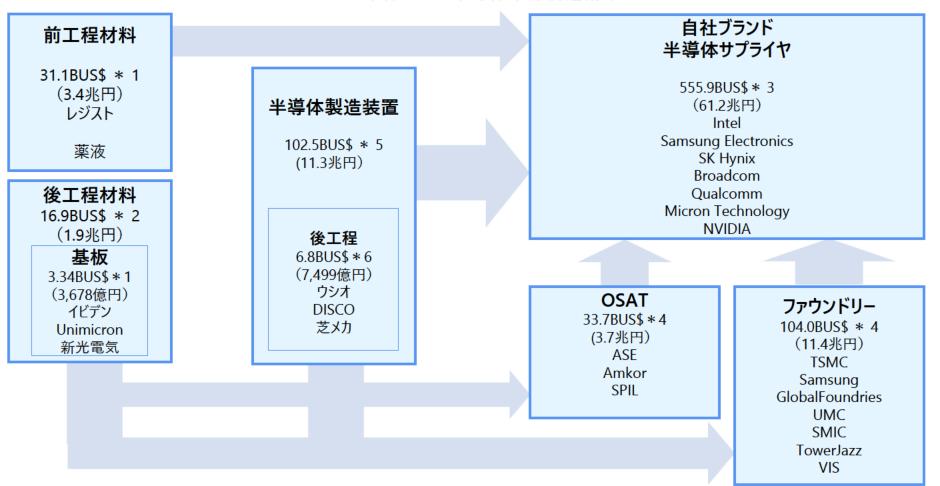

● 半導体産業は自社ブランド半導体サプライヤを中心とし、それを支えるファウンドリーやOSATが一部製造工程を請け負い最 終製品を製造している。また、最終製品の製造のために、半導体材料メーカ・パッケージ基板メーカ及び製造装置メーカが材 料・製造装置を半導体サプライヤ並びにファウンドリーやOSATに提供している。

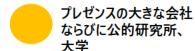

# 半導体のキープレイヤ

- 半導体産業は、様々な産業に分化しており、それぞれの領域にキープレイヤがいる。

- 自社ブランドで半導体を提供する半導体企業は、市場成長に連動し、好業績を続けており、2021年平均利益率は、 22.8%と高い利益を収めている。上位10社の内、7社はIntelをはじめとする米国系企業であり、半数はファブレスメーカ となっている。日本は、目盛りをリードするキオクシアに次いで、ソニー、ルネサスの順となっている。

- 製造を担うファウンドリーでは、台湾のTSMCが市場を圧倒しており、規模・収益性ともに業界をリードしている。

- 半導体の後工程を担うOSATでは、台湾ASEが2番手の米国Amkorの2倍近いパフォーマンスを上げている。

- 製造装置では、AMAT、ASML、Lam Research、東京エレクトロン(TEL)の4社が10BUS\$を超える売上で好業績を 続けている他、技術革新を捉え工程に特化した企業が存在する。

- 材料では、素材・化学のコングロマリットともいうべき巨大企業の一部門が半導体材料をサポートしていることが多い。 なかでも、日本企業の存在感が高い。

- 半導体後工程における重要部材であるパッケージ基板は、日本のイビデン、新光電気の存在感が目立っており、 ついで台湾などアジア勢が市場で目立った存在となっている。

# 第2章 後工程プロセスの現状及び将来動向

## 後工程プロセス技術の現状及び関連市場動向

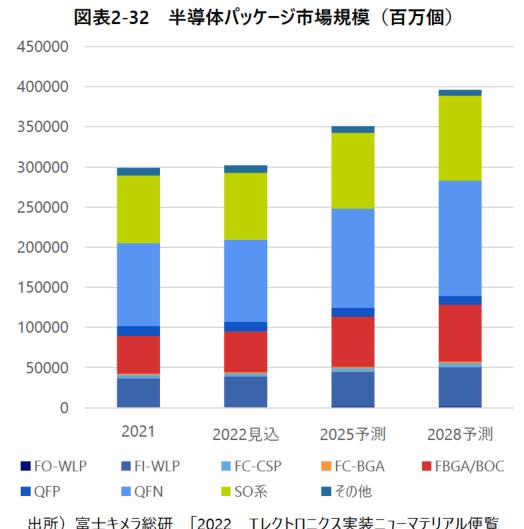

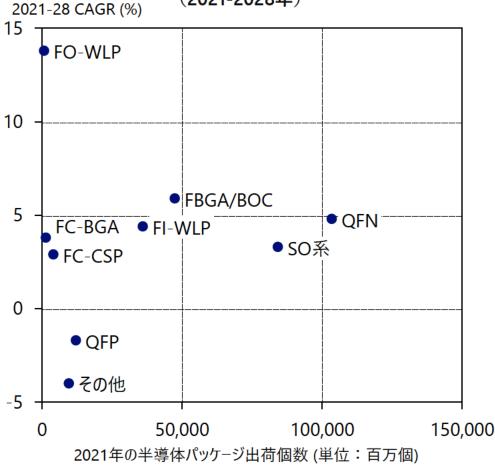

- パッケージは、リードフレームベースのデバイスが大半を占めるも、高集積の先端パッケージでは、サブストレートを使用したFBGA、 FC-BGAに加えて、Fan Out WLP (FO-WLP)のパッケージが急成長している。

- このFO-WLPに代表される2.XDプロセスが急成長しており、新たな高集積化技術の可能性が広がっている。

- ビルドアップ基板などを使用するFC-BGAでは、日本国内2社で4割のシェアを持ち、技術的にも世界をリードしている。

## 後工程先端プロセスの現状

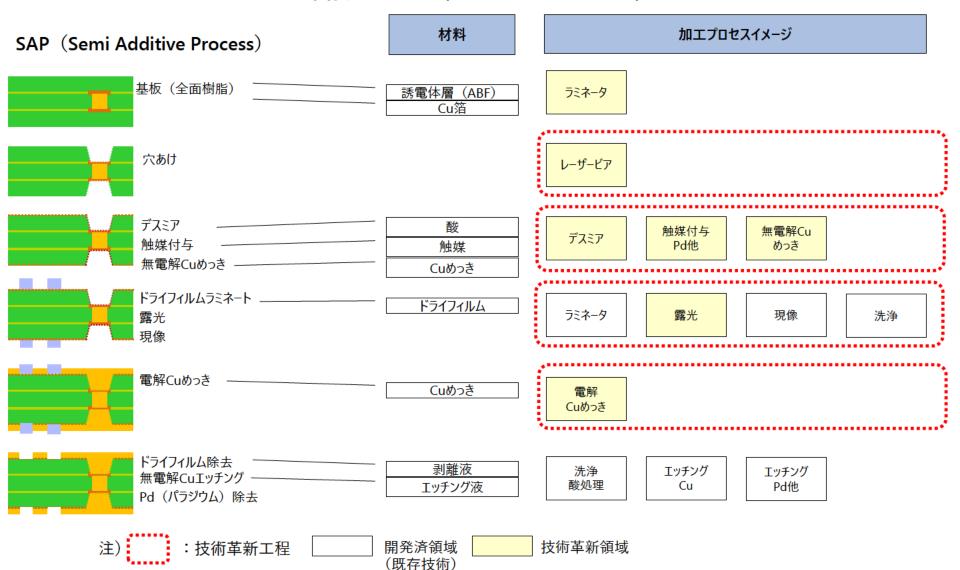

- パッケージ基板は、SAP (Semi Additive Process)、MSAP (Modified Semi Additive Process) などのプロセスが使用 されており、微細な基板では、SAPが多く使用されるようになっている。

- ファウンドリー大手のTSMC、MPU大手のIntelなどは、このパッケージ基板を応用し、2.XDプロセスの高集積デバイスの実用化 を進めている。

## 後工程先端プロセスの将来動向

- AI・マルチクラウドの発展により、ビッグデータ社会の成長が予想される。この実現に向けて計算スピードが速く、高集積の 半導体が求められている。

- 半導体市場は、シクリカルながら高成長を続け、2030年には、800BUS\$ (104兆円) 市場となる見込み。

- 一方、ビッグデータの計算処理には大量エネルギー消費することが課題となる。このため、機能を高度化・効率化しつつ、 エネルギー消費を最小限に抑える半導体の高集積化技術が必要不可欠となっている。

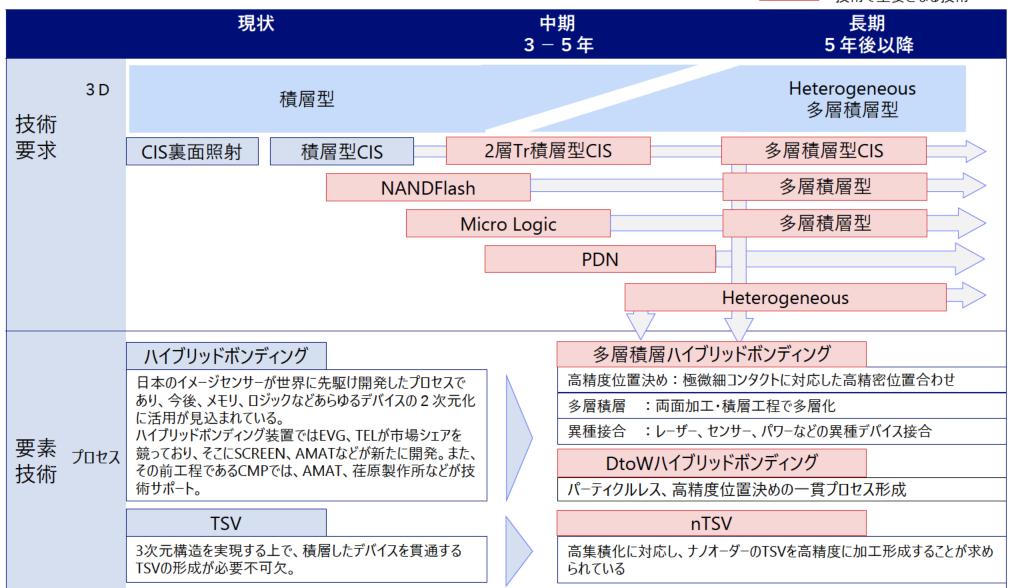

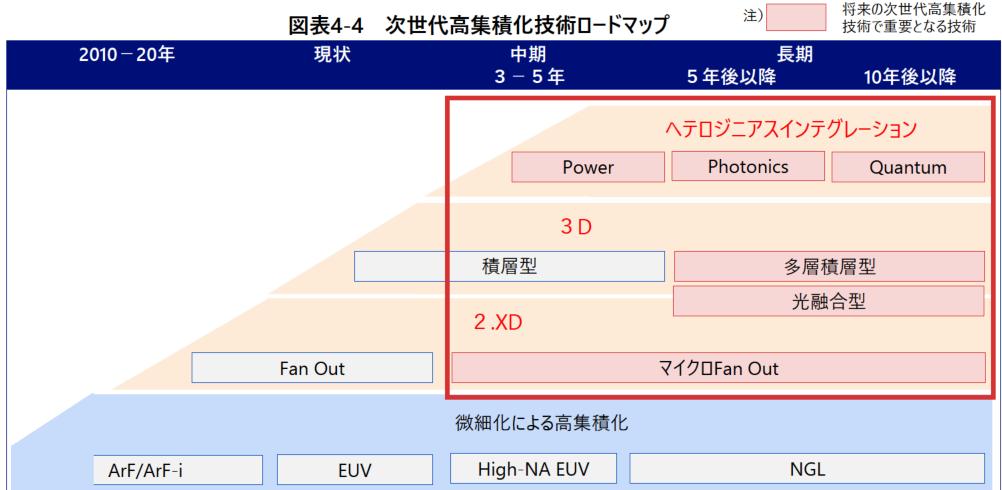

- 将来の高集積化技術は、2次元の微細化だけでなく、2.XDのさらなる発展に加え、3D、ヘテロジニアスインテグレーションの 技術開発が注目されている。

- 3Dデバイス構造では、2次元上に展開していたデバイスを機能別に3次元かつ多層で接合することで、立体的な高集積化を 実現する。

- ヘテロジニアスインテグレーションは、レーザーやセンサー、パワーデバイスなどこれまで一体化されてこなかった異種デバイスを 高集積化し、新たな機能を実現しようとしている。

- これら将来技術に、世界の半導体有力企業・研究機関が次世代高集積化技術に注目しており、開発競争が激化している。

# 第3章 後工程材料・装置の現状及び将来動向

#### 後工程材料・装置の現状及び関連市場動向

● 日本は、半導体後工程で使用される基板、装置、材料の世界市場で高いシェアを確保しており、次世代高集積化の コア要素技術を担っている。そこで、本調査では、後工程・パッケージ主要材料、パッケージ基板関連材料、装置に分類して 分析を進めている。

#### 後工程材料・装置の現状

- 近年の後工程材料・装置市場の動向をみると、パッケージ基板材料は20%以上、製造装置は30%以上の成長と高成長 を遂げている。

- この高成長分野である材料・装置において、日本は、過半を占める高いシェアを有するものが多く、高い競争力を有している。

- 特に、先端のパッケージ基板で重要な層間絶縁フィルム、再配線材料、半導体デバイスを個片化し、組み立てていく工程で 必要なバックグラインダ装置、ダイシング装置、後工程用ステッパなどでは、日本が圧倒的なシェアを有しており、現在の量産 だけでなく、今後の開発においても重要な役割を担っている。

## 後工程材料・装置の将来動向

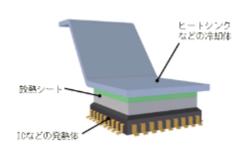

- 半導体後工程・パッケージ主要材料では、半導体の高機能・高集積化を進めるに従って1チップの消費電力が数百Wを超え るものも登場しており、高性能化とともに課題となる熱マネージメントに必要なTIM(Thermal Interface Material)が重要 となっている。

- 後工程・パッケージ基板関連材料では、ハイエンドの2.XD Fan Outプロセスの鍵となる層間絶縁フィルムや再配線材料などが 重要となる。

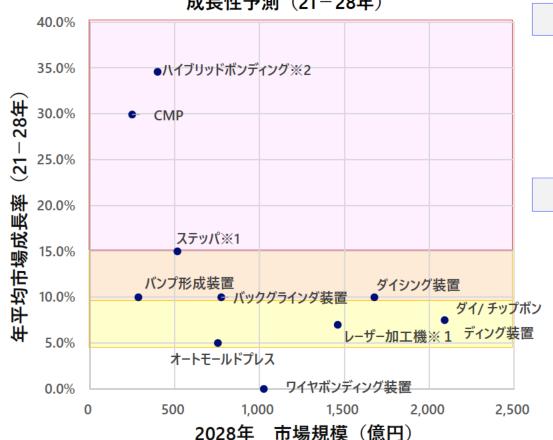

- 装置としては、2.XD向けに露光やバンプ形成、ボンディングなど全般的に技術革新が求められる他、3D、ヘテロジニアスイン テグレーション向けに、新たにハイブリッドボンディング装置、その前工程でCMP等が使用されるようになり、新たな市場が拡大 する。

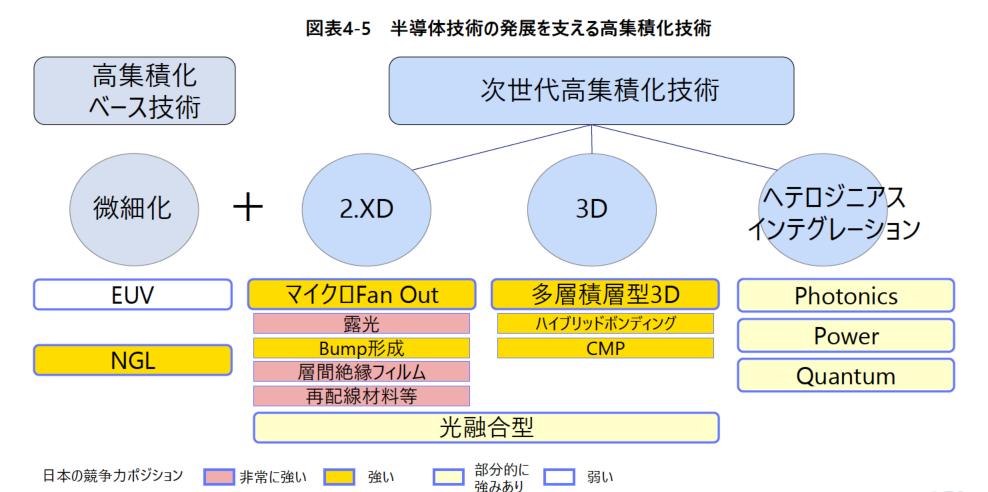

#### 日本の産業競争力評価及び競争力強化のための視点 第4章

- 半導体後工程における重要技術と競争カポジション

- 次世代半導体高集積化に必要な後工程技術における日本の産業競争力は極めて高い。

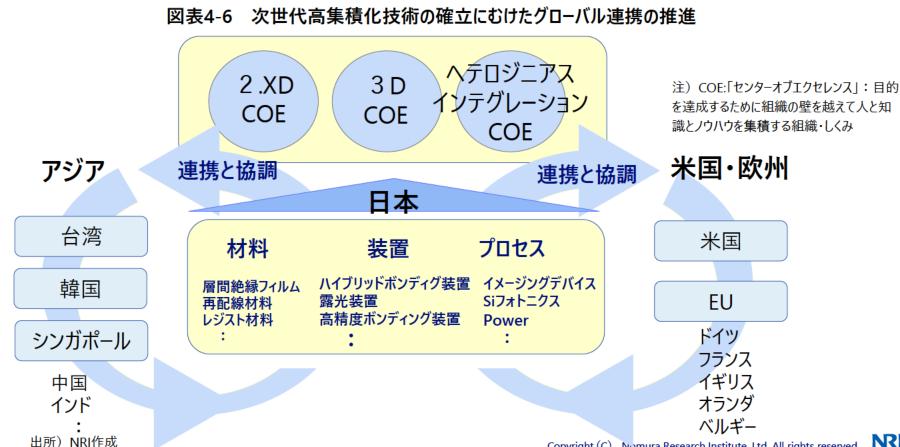

- 次世代高集積化技術である「2.XD」、「3D」、「ヘテロジニアスインテグレーション」の3大領域技術における将来課題技術の 開発が重要。

- 日本は、次世代高集積化技術における重要な材料、装置技術等のコア技術において有力なシェアポジションを確保している。

- 2.XDのコア技術であるパッケージ基板及びその材料の層間絶縁フィルムや再配線材料 など

- 3Dのコア技術であるハイブリッドボンディング装置、CMP など

- ヘテロジニアスインテグレーションの対象であるレーザーやセンサー、パワーなどやデバイスや接合技術 など

- 産業競争力強化のための要点・示唆

- ビッグデータ社会の発展に必要なデバイスの高速化と高集積化を実現するため、日本は、これら半導体の材料・装置等に おける強みを活かし、「次世代高集積化プロセス技術」に昇華させてゆく責務を担っている。

- 半導体産業は、日本に閉じる産業ではなく、米国、欧州、台湾などと連携し、個々の分野で強みを発揮しつつ、成長を 実現してきた。現在ある日本の強みを生かし、さらに革新を重ね、諸外国の企業や研究機関との連携と協調を推し進める ことで、社会と産業の発展に寄与することが望まれていると考える。

# 第1章:半導体業界構造の概観とキープレイヤ

- 1-1.業界構造俯瞰

- 1-2. 半導体業界のキープレイヤ

# 業界構造俯瞰:半導体デバイス市場

- 半導体市場は、米中摩擦・コロナショック等の影響で一時的な減速もあったが、2020年には拡大基調に転じた。 世界市場は、2020年451BUS\$、2021年には対前年26%で成長し、555.9BUS\$の規模に拡大している。

- 製品別には、Analog、MOS Memory、MOS Logicが21年に年率30%を超えて成長し、市場をリード。21年における市場構成比 は、MOS Logic 27.9%、MOS Memory 27.7%、MOS Micro 14.4%で大きなウエイトを占めている。

- 2022年の下期には在宅特需が一巡し、世界的インフレ、中国のロックダウンやロシアのウクライナ侵攻長期化などの複合的な要因の 影響で個人向け電子機器の消費が落ち込み、減速基調にあるものの、573.5BUS\$とプラス成長。

# 業界構造俯瞰:自社ブランド半導体サプライヤ並びに関連企業との関係

■ 半導体産業は自社ブランド半導体サプライヤを中心とし、それを支えるファウンドリーやOSATが一部製造工程を請け負い最終製品を 製造している。また、最終製品の製造のために、半導体材料メーカ・パッケージ基板メーカ及び製造装置メーカが材料・製造装置を 半導体サプライヤ並びにファウンドリーやOSATに提供している。

## 図表1-2 半導体業界構造俯瞰

<sup>\*1:</sup>富士経済「2022年 半導体材料市場の現状と将来展望(2022年度)| 2021年実績合計 \*2:富士経済「2022年 半導体材料市場の現状と将来展望(2022年度)|

富士キメラ総研「2022及び2021 エレクトロニクス実装ニューマテリアル便覧(2022・2021年度)」を基にNRI算出 \*3:WSTS 「世界半導体市場統計 (2021年) |

<sup>\*4:</sup>各社業績より推計 、\*5:SEMI 「世界半導体製造装置市場調査(2021年)」

<sup>\*6:</sup>実績値は、GNC「世界半導体製造装置・試験/検査装置市場年鑑2022 (2022年度) 」及び富士キメラ総研「2021 エレクトロニクス 実装ニューマテリアル便覧(2021年度)」を基にNRI算出 Copyright (C) Nomura Research Institute, Ltd. All rights reserved. 14

# |-2. 半導体業界のキープレイヤ

# (1) 半導体製造装置市場と主要企業:企業動向

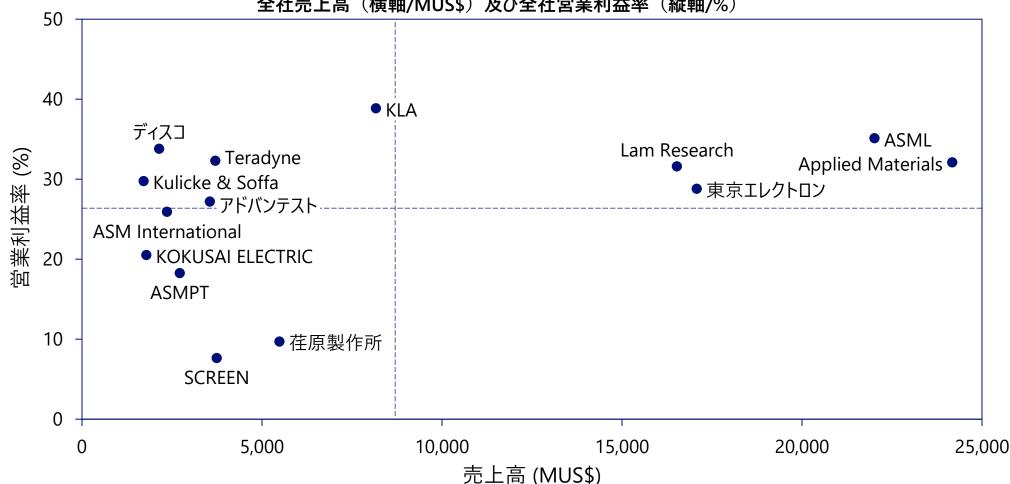

- 半導体製造装置はAMAT、ASML、LAM、東京エレクトロン(TEL)の4社が10BUS\$を超える売上で好業績を続けている。

- 10BUS\$を下回る企業の中では、検査装置のKLA、後工程装置のディスコ、Kulicke & Soffa、テスターのTeradyne、アドバンテスト が平均の営業利益26.5%を上回る利益を上げている。

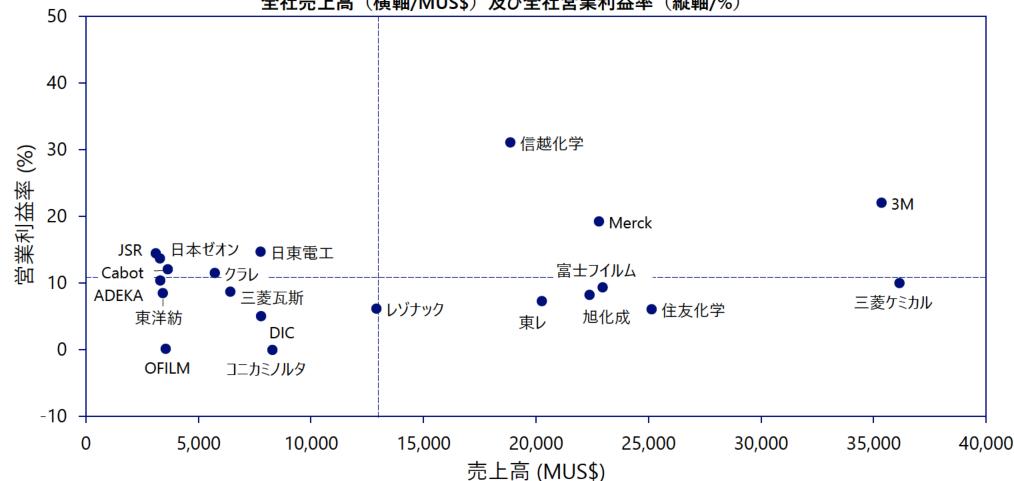

図表1-3 2021年度の半導体製造装置企業業績 全社売上高(横軸/MUS\$)及び全社営業利益率(縦軸/%)

# 1-2. 半導体業界のキープレイヤ (2) 半導体材料市場と主要企業:企業動向

- 総合化学メーカなどの一部門として、半導体・電子材料分野へ参入している企業が多い。

- 信越化学(シリコンウェハ/フォトレジスト)や住友化学・富士フイルム(半導体洗浄液)など、日本素材・化学メーカの存在感がある。

図表1-4 2021年度の半導体材料メーカ業績 全社売上高(横軸/MUS\$)及び全社営業利益率(縦軸/%)

# 1-2. 半導体業界のキープレイヤ (3) パッケージ基板市場と主要企業:企業動向

■ パッケージ基板分野は、日本のイビデン、新光電気工業、台湾のUnimicron、Nan Yanya、Kinsus、韓国のSEMCO(Samsung グループ)でシェアを争っている。市場構造としては、ハイエンドを日系2社で70-80%のシェアを確保しており、ミドルエンド以降で 台湾企業がシェアを確保している状況。

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 2-3. 後工程プロセスの将来動向

# 2-1. 後工程プロセス技術の現状及び関連市場動向

1) 半導体パッケージ市場動向

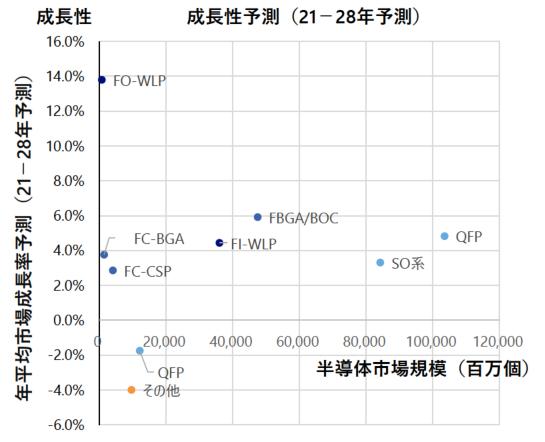

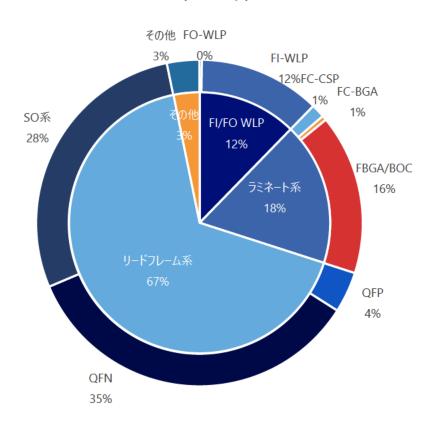

パッケージは、リードフレームベースのデバイスが大半を占めるも、高集積の先端パッケージでは、 サブストレートを使用したFBGA、FC-BGAに加えて、FO-WLPのパッケージが急成長している。

図表2-1 半導体パッケージ2021年市場規模(百万個)と

出所) 富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧 (2022年度)」を基にNRI作成

半導体パッケージ市場構成比 (2021年)

出所) 富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧 (2022年度)」を基にNRI作成

# 2-1. 後工程プロセス技術の現状及び関連市場動向

- 1) 半導体パッケージ市場動向

- ① Fan Out WLP (FO-WLP) 市場

<シェアポジション>

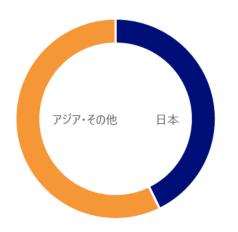

- FO-WLP市場トップシェアは、台湾のC社であり、5割強を確保し、 圧倒的に優位なポジションにある。2位のD社と合わせて、台湾2社で 市場の8割強を占有する。

- 世界に先駆けて、2006年にドイツのB社がFO-WLPの量産プロセスを確 立し、eWLB (embedded Wafer Level Ball grid array)として市場に 展開。

- 米国のA社、韓国F社、中国のE社などが市場に参入。

図表2-3 FO-WLP世界市場 (2021年) 186万枚

#### 出所) 富士キメラ総研 「2022 エレクトロニクス 実装ニューマテリアル便覧 (2022年度) 」を基にNRI作成

### FO-WLP市場のシェアポジション

|     | 10-11日初のフェアルフラコン                                                                                                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 米国  | A社:ハイエンドRF WLANコンボチップからFPGA、パワーマネジメントなど幅広く展開しており、台湾、韓国、中国のファウンドリーに隣接して生産体制を整えている。                                                                                                          |

| 欧州  | B社:2006年にはじめてFO-WLP技術を開発し、eWLB<br>(embedded Wafer Level Ball grid array)技術とし<br>て確立し、当業界をリード。A社、D社など他社にライセン<br>スを供与。                                                                       |

|     | 台湾  ■ C社:ファンドリ世界最大手企業であり、FO-WLP市場の5割を掌握。InFOが大手スマートフォンメーカのアプリケーションプロセッサーに採用される他、シリコンインターポーザベースのCoWoSは、サーバー、AI、グラフィックス向けに供給している。  ■ D社:通信系ファウンドリー向けにシェア確保。自社ソリューションとしてeWLB、M Seriesをラインナップ。 |

| アジア | 中国  ● E社:パッケージングからテストまでを請け負う中国最大企業。子会社にディスクリート系の半導体を製造するE2社を持つ。                                                                                                                            |

|     | 韓国  ● F社:半導体パッケージから液晶向けの材料を手掛ける企業。WLPのみならず、FO-PLPの量産ラインを確立。                                                                                                                                |

| その他 | ● 日本、その他                                                                                                                                                                                   |

# 2-1. 後工程プロセス技術の現状及び関連市場動向

- 1) 半導体パッケージ市場動向

- ②FC-BGA基板市場

<シェアポジション>

- 日本のA社が、市場トップシェアを確保し、国内2位のB社とで市場の 4割を確保し、優位なポジションを確保している。

- 一方で、世界市場 2 位の台湾のC社他、D社、E社とボリュームゾーンの 量産品で存在感を示す台湾企業が、市場の3分の1を占めるように なっている。

- 韓国では、Samsungグループなど韓国の需要を背景にF社が着実に シェアを確保している。

図表2-4 FC-BGA基板市場 (2021年) 7,728億円

#### FC-BGA基板市場のシェアポジション

| 日本      | A社:世界市場の3割弱を掌握し、世界トップシェア。<br>国内大垣に2工場、フィリピンに1工場を持ち、先端の<br>基板を開発・生産。ハイエンド基板を提供可能なクリー<br>ン度の工場投資を行い、さらなるシェア拡大を模索。           |

|---------|---------------------------------------------------------------------------------------------------------------------------|

|         | B社:国内第2位。技術力の高い企業として評価され、<br>Intel/AMD向けのプロセッサに基板を提供。                                                                     |

| アジア・その他 | 台湾  ■ C社:世界第2位の企業。Intel/AMD等プロセッサメーカ向けのミドルエンドのボリュームゾーンの製品に強みを持っている。  ■ D社:台湾の材料メーカのPCB基板子会社。  ■ E社:BGA基板を得意とするパッケージ基板メーカ。 |

|         | 韓国  ● F社:AMD、Apple、Intelなどパソコン用 C PUに実績が多く。近年、ハイエンドにも力を入れる。                                                               |

出所) 市場規模:富士キメラ総研 「2022 エレクトロニクス 実装ニューマテリアル便覧(2022年度) |を基にNRI作成

地域別シェア:同資料を基にNRI算出

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 1) 先端パッケージ基板

- 2) 先端企業動向

- 3) 先端プロセス

- 2-3. 後工程プロセスの将来動向

# 2-2. 後工程先端プロセスの現状 1)先端パッケージ基板 パッケージ基板 SAPプロセス

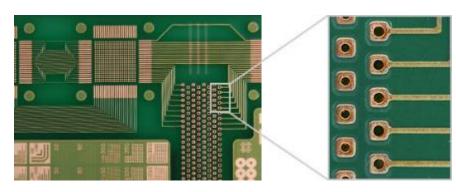

図表2-5 SAP(Semi Additive Process)プロセスイメージ

# 2-2. 後工程先端プロセスの現状 1)先端パッケージ基板 パッケージ基板 MSAPプロセス

図表2-6 MSAP(Modified Semi Additive Process)プロセスイメージ

| MSAP (N | Modified Semi Additive Process)               | 材料               | 加工プロセスイメージ            |

|---------|-----------------------------------------------|------------------|-----------------------|

|         | 基板(超薄銅箔付)———————————————————————————————————— | Cu箔<br>誘電体層(ABF) | 銅箔<br>張り合わせ           |

|         | 穴あけ                                           |                  | レーザービア                |

|         | デスミア<br>触媒付与<br>無電解Cuめっき                      | 触媒               | デスミア 触媒付与 無電解Cu めっき   |

|         | ドライフィルムラミネート<br>露光<br>現像                      | Cuめっき<br>ドライフィルム | ラミネータ 露光 現像 洗浄        |

|         | 電解Cuめっき ————————————————————————————————————  | Cuめっき            | Cuめっき                 |

|         | ドライフィルム除去<br>シード層エッチング                        | 剥離液<br>エッチング液    | 洗浄<br>酸処理 エッチング<br>Pd |

|         | 注):技術革新工程                                     | 開発済領域 (既存技術)     | 技術革新領域                |

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 1) 先端パッケージ基板

- 2) 先端企業動向

- 3) 先端プロセス

- 2-3. 後工程プロセスの将来動向

# 2-2. 後工程先端プロセスの現状 2) 先端企業動向 Intelの先端プロセス (前工程)

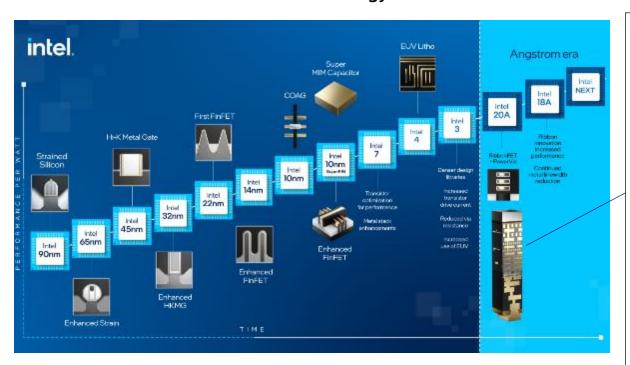

- Intel社は、3nmNodeの次のプロセスとして、20Aの開発をすすめている。この世代からデバイス構造は、大きく変わり、トランジスタ 並びに電源等の配線構造を3次元化している。

- トランジスタは、GAA (Gate All Around) 構造でゲート上にリボン状のフィンを多段階に重ねた構造を持っている。

- 電源の配線は、信号の配線層の裏側から取る構造にし、配線層が垂直方向に長い構造となっている。これにより、電源と信号線 の干渉を抑え、高集積化を可能にしている。

# 図表2-7 Intel Process Technology Innovations (2022)

#### Power Via

- 配線層と電源層を分離し、 高速通信をする配線層とその 回路に電気を供給する 電源回路を分離することで、 3次元の集積度を向上する。

- 電源と信号の配線を分離する ことで、多電源供給が可能に なる。ノイズを押えることにも 貢献する。

# 2-2. 後工程先端プロセスの現状 2)先端企業動向 Intelの先端パッケージ技術 (後工程)

## Intelの先端パッケージ

- EMIB(Embedded Multi-Die Interconnect Bridge):ビルドアップ基板にSi配線基板を埋め込み集積化

- デュアルレチクルサイズデバイスで、モノリシック設計とほぼ同じパフォーマンスを実現。

- 次世代EMIBは現行の55μmのバンプピッチから45μm、そして40μmに集積化予定。

- 同技術を契機にシリコンブリッジを用いた次世代パッケージの開発が進展し、TSMC、IBMも採用を進めている。

- Foveros:TSVで異なるチップを集積化

- 36μmのバンプピッチで、複数のテクノロジーノードにまたがるチップレットを同時に実装することで、5~125Wの熱設計範囲で 使用できる。Meteor Lakeに適用。

- Foveros Direct: 2024年に、ハイブリッドボンディングを量産導入予定。 この世代には、I/O Padサイズがφ0.5μm/1μm pitch、Bump世代は、10μm以下になる。

図表2-8 Intelの先端パッケージイノベーション

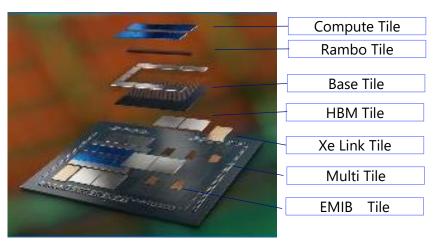

# 2-2. 後工程先端プロセスの現状 2)先端企業動向 Sapphire Rapidsにおいてエンベディッドからモジュラーアークテクチャにシフトし、大規模3D パッケージ技術により大規模SoC Ponte Vecchioを開発

- Intel社は、単一デバイスに集積する構造から多数のタイル状 のデバイスをSapphire Rapidsからモジュラー構造で集積する 形にシフトした。本SoCのアーキテクチャでは、低レイテンシー ながら、高いクロスセクションバンド幅データ伝送が可能な システム構成となっている。

- Sapphire Rapidsは、HBM (High Bandwidth Memory) を使用し、メモリ容量とバンド幅を確保している。

図表2-9 Sapphire Rapidsでの **モジュラーアーキテクチャへのシフト**

出所)Intelホームページ https://medium.com/intel-tech/sapphire-rapids-sets-a-newstandard-for-data-center-architectures-6bc103d97adf

- Intelは、2020年にHPC(High Performance Computing) 向けチップとして開発。Ponte Vecchioでは、1チップに5つの 世代の露光技術を使用し、47個のDieを集積し、トータル 1,000億以上のトランジスタ集積を実現している。

- シリコンブリッジチップを埋め込んだパッケージ基板上に、複数の タイル状のDieを実装。高速処理を行うComputeタイルは、 シリコンで形成されたTSV配線層である基板上に実装し、 Die間の高速通信が可能な3次元大規模SoCを実現。 Die to DieのBump最小ピッチは、36µmでBase Dieサイズは 650mm<sup>2</sup>の巨大な基板に高集積を実現している。

#### 図表2-10 Ponte Vecchio

出所)Intelホームページ

https://www.intel.com/content/www/us/en/corporate/usa-chipmaking/news-andresources/emib-packaging-technology-and-pontevecchio.html?wapkw=Ponte%20Vecchio%20HPC

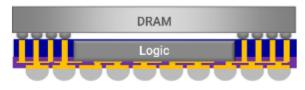

# 2-2. 後工程先端プロセスの現状 2)先端企業動向 TSMCのファンアウト (FO-WLP)プロセス技術

- 半導体プロセスをリードするTSMCは、3D Fabricationにおいても市場をリードしている。

- その技術は、大きく2つの技術に分かれる。チップとチップの間を有機の再配線層で接合させるInFO(Integrated Fan Out)とシリコンウェハプロセスを利用して製造したインターポーザ上に、複数のチップを集積させるCoWoS (Chip-on-Wafer-on-Substrate)を実用化している。

- InFO (Integrated Fan Out)

- シリコンダイの入出力パッドからパッケージの入出力端子へ と入出力信号を再配置。高密度な再配線層(RDL:Re-Distribution Layer)は、薄膜プロセスで形成。

#### 図表2-11 InFO PoP

出所)TSMC https://www.tsmc.com/japanese/node/131

- CoWoS(Chip-on-Wafer-on-Substrate) :

- 樹脂でできたパッケージ基板の上に、シリコンウェハプロセスで製造したインターポーザを配置し、その上に複数のシリコンダイを実装し、2.5Dパッケージを実現。

- AIIンジンやサーバー用エンジン、ハイエンドFPGAなど数多くの 実用事例あり。

図表2-12 CoWoS-L

出所) TSMC HP

https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/cowos.htm

# 図表2-13 CoWoS-R

出所) TSMCホームページ

https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/cowos.htm

Copyright (C) Nomura Research Institute, Ltd. All rights reserved.

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 1) 先端パッケージ基板

- 2) 先端企業動向

- 3) 先端プロセス

- 2-3. 後工程プロセスの将来動向

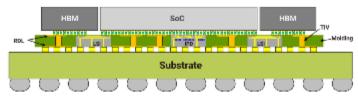

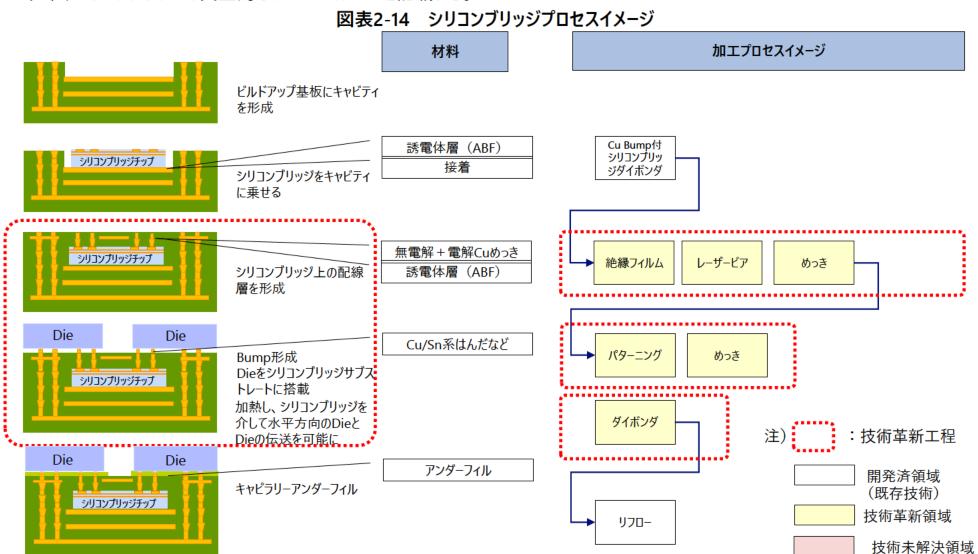

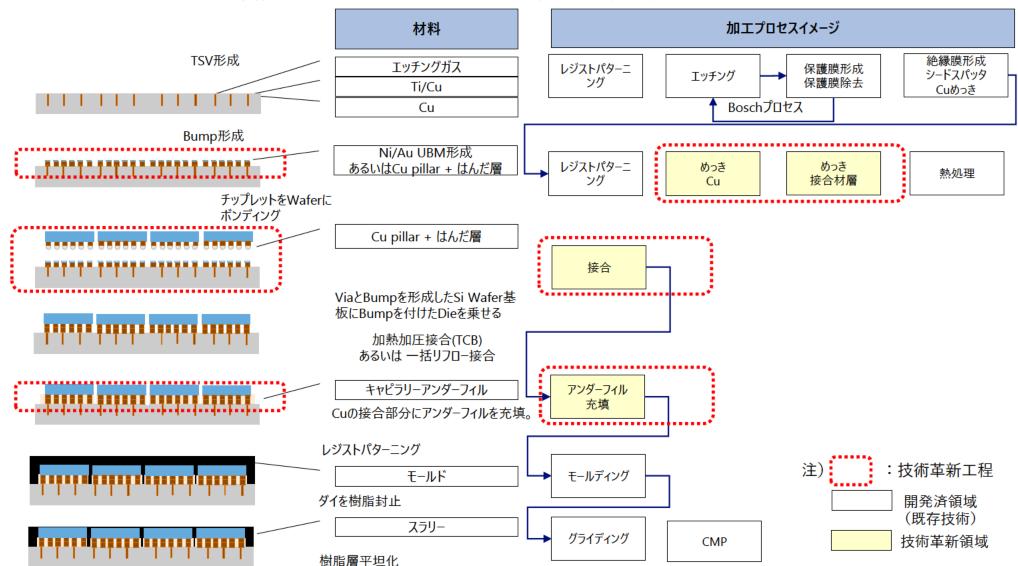

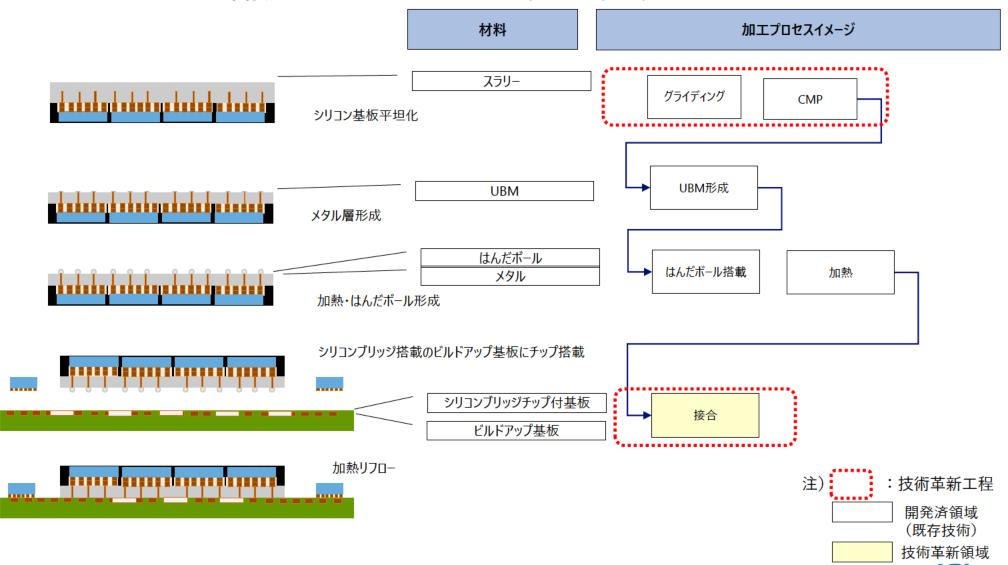

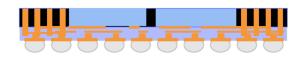

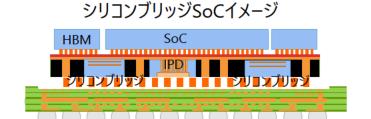

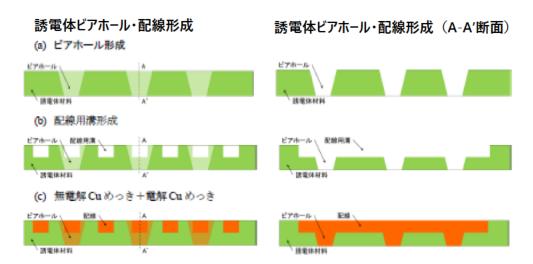

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス シリコンブリッジプロセスイメージ

■ ビルドアップ基板に小さなシリコン配線層であるシリコンブリッジを埋め込み、ビルドアップ基板上のDie間を高速で通信可能にする。 以下、シリコンブリッジの典型的なプロセスイメージを記載する。

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス 3Dスタッキングプロセスイメージ (1/2)

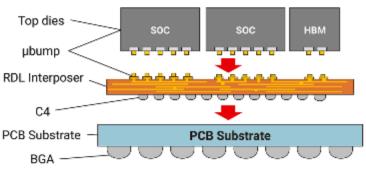

■ シリコンインターポーザをベースとする 3 Dスタッキングプロセス技術のイメージ。

図表2-15 シリコンインターポーザベースの3Dスタッキングプロセスイメージ

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス 3Dスタッキングプロセスイメージ (2/2)

図表2-16 シリコンインターポーザベースの3Dスタッキングプロセスイメージ

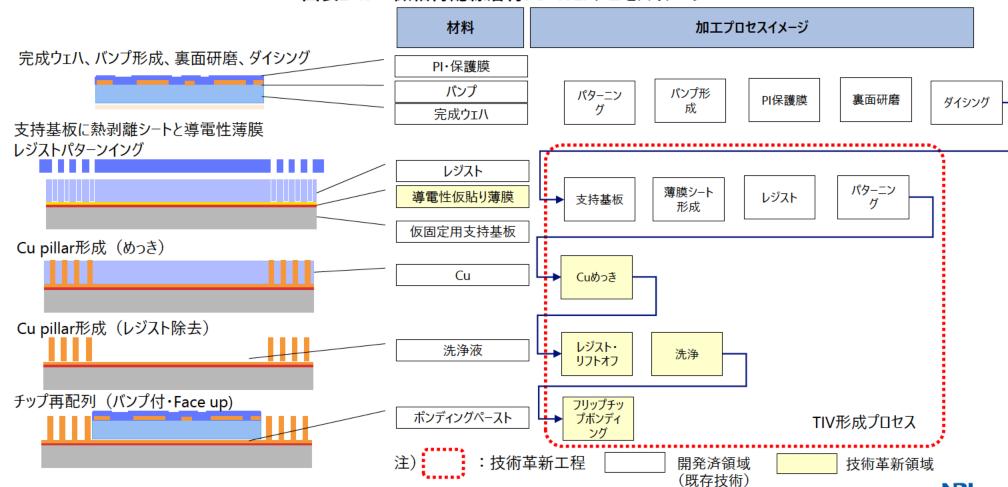

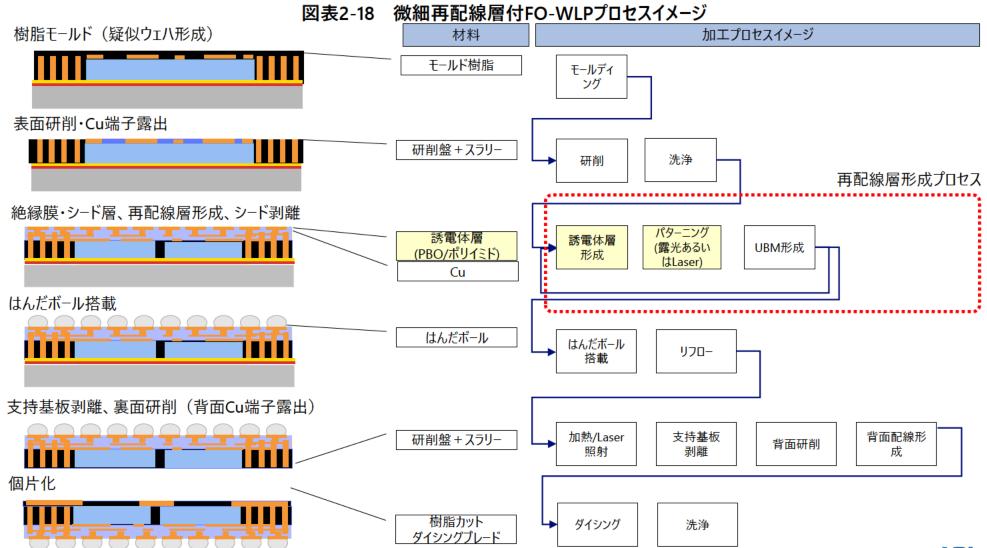

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス 微細再配線層付FO-WLPプロセスイメージ (1/2)

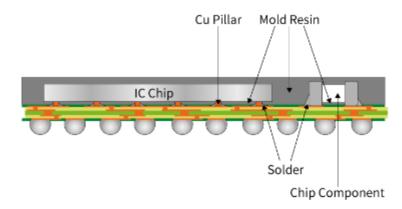

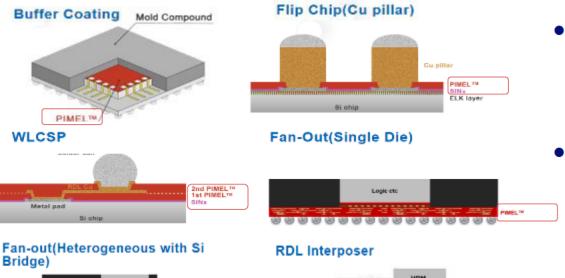

- 有機誘電体層の再配線層付Fan Out WLPは、有機基板の配線層形成技術を活用したプロセス。

- ガラス支持基板上に、チップとCu pillarをMold樹脂で封止しグラインディング+CMPでチップとCu pillar 表面を露出した後、その上に、再配線層を形成することで、高密度かつ薄型のSiP(システムインパッケー ジ)を実現する。Cu pillarは、樹脂モールドで固定化され、シリコン上の等TSVと同じ構造を形成。

微細再配線層付FO-WLPパッケージ

#### 微細再配線層付FO-WLPプロセスイメージ 図表2-17

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス 微細再配線層付FO-WLPプロセスイメージ(2/2)

■ 再配線層は、疑似モールド後、研削し、Cu端子を露出した後に、感光性絶縁膜(感光性プロイミドなど)でパターン形成し、 その後、Cuのめっきにより配線を形成する。この工程を繰り返し、多層の再配線層を形成する。

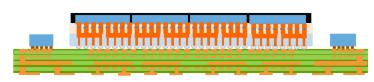

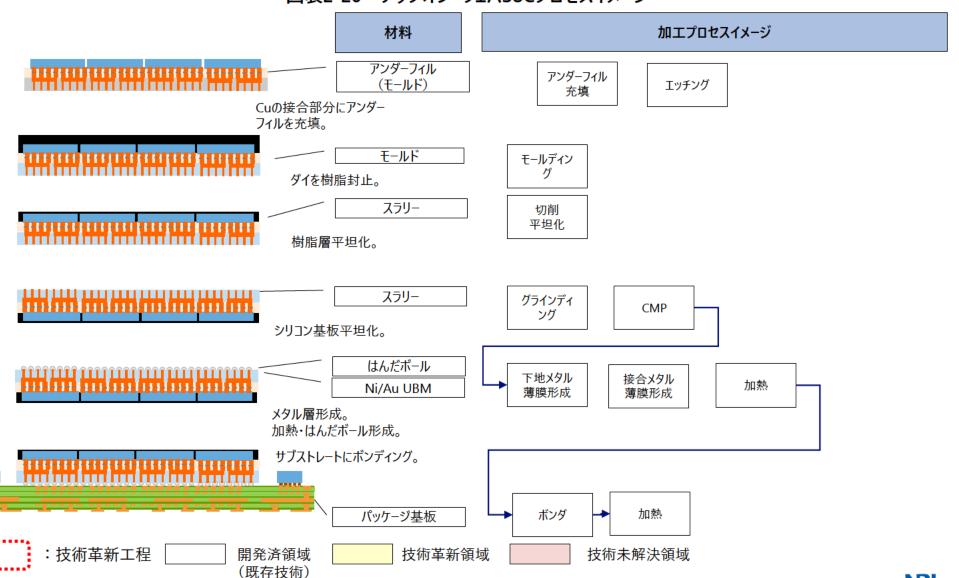

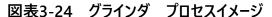

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス チップ・オン・ウェハSoCプロセスイメージ(1/2)

チップ・オン・ウェハSoCイメージ

■ パッケージ基板の上にシリコンインターポーザを中間基板として、複数のシリコン ダイをマイクロバンプによって接続し、シリコンインターポーザの表面と裏面はTSV (シリコン貫通ビア)によって接続した構造を持つ。

#### 図表2-19 チップオン・ウェハSoCプロセスイメージ

(既存技術)

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス チップ・オン・ウェハSoCプロセスイメージ (2/2)

#### 図表2-20 チップオン・ウェハSoCプロセスイメージ

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス シリコンブリッジSoCプロセスイメージ (1/2)

図表2-21 シリコンブリッジSoCプロセスイメージ 材料 加工プロセスイメージ 支持基板に熱剥離シートと導電性薄膜 レジストパターンイング レジスト パターニン 薄膜シート 導電性薄膜 レジスト 支持基板 グ 形成 熱剥離シート Cuピラー形成(めっき) 仮固定用支持基板 TIV形成プロセス Cu Cuめっき Cuピラー形成(レジスト除去) レジスト・ 洗浄液 洗浄 リフトオフ LSI/IPD実装 **IPD** シリコンブリッジ シリコンブリッジ ボンディン ボンディングペースト モールディング 開発済領域 (既存技術) モールド樹脂 モールディ シリコンブリッジ ング 技術革新領域 ブリッジ形成プロセス

# 2-2. 後工程先端プロセスの現状 3) 先端プロセス シリコンブリッジSoCプロセスイメージ(2/2)

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 2-3. 後工程プロセスの将来動向

- 1) 将来技術動向

- 2) 技術開発動向

- 3) 先進事例

1) 将来技術動向:半導体ロードマップの整理と後工程及びチップレット実装工程の技術革新

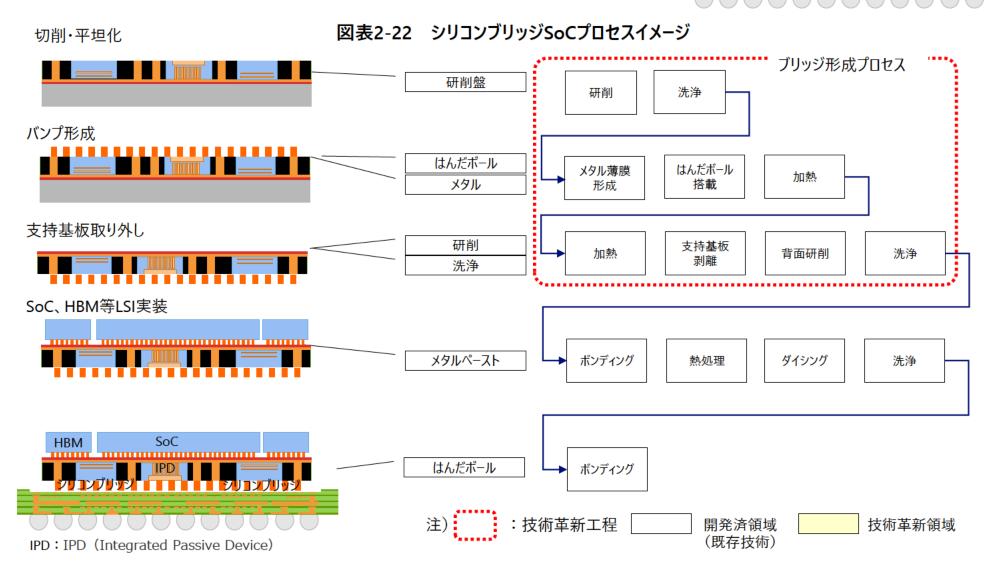

# 電子産業の将来動向 :新たなデジタルワールドの発展

自動車のEV化に代表されるようにあらゆる機器が電子制御され、同時にリアルな現実社会とバーチャルなデジタルワールドとの連携 が進む。トラフィックとサービスのコンピューティングは一元化されたクラウドからネットワークエッジとクラウドの先のデジタルワールドとの連 携により、莫大なデータが飛び交うBig Data社会になる。

図表2-23 ビッグデータ社会の構造

# 1) 将来技術動向:半導体ロードマップの整理と後工程及びチップレット実装工程の技術革新

# Big data社会とAIエンジン

- Intel社は、人類が生み出すデジタルデータ量は、2020年に50ZB(ゼタバイト(10の21乗バイト、あるいは2の70乗バイトの単位)) を超え、2025年には175ZBに急拡大すると予測している。また、このようなビッグデータを処理するために、人工知能(AI)向けの半 導体市場も急拡大し、2020年には10BUS\$を超え、10年後には10倍になると予測している。

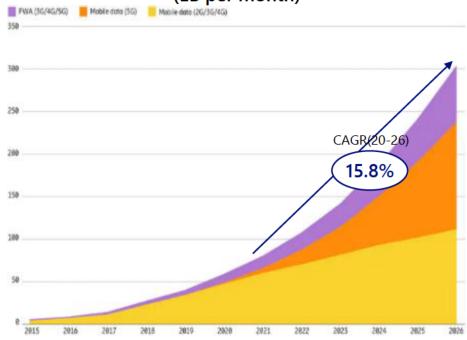

- モバイルネットワークトラフィックの合計は、デバイス機能の向上、データ集約型コンテンツの増加、ネットワークパフォーマンスの継続的な 改善を背景に、2026年に月300EB(エクサバイト( 10の18乗バイトの単位))を超える見込み。

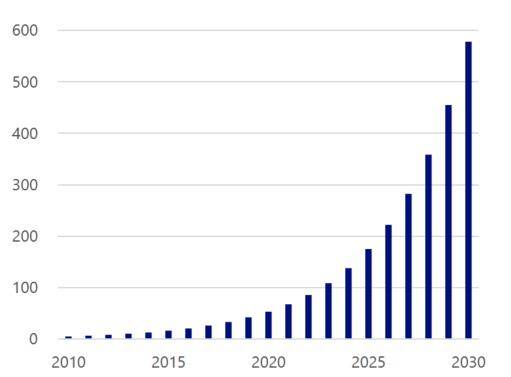

#### 図表2-25 人類が生み出すデジタルデータ量 (ZB)

注: ZB(ゼタバイト): 10の21乗バイト、あるいは、2の70乗バイト 出所)Intel Architecture Day 2020 2025年までの見通し、2030年までトレンド推移 https://newsroom.intel.com/wp-content/uploads/sites/11/2020/08/ Intel-Architecture-Day-2020-Presentation-Slides.pdf

図表2-26 世界のモバイルネットワークトラフィック (EB per month)

注) EB (エクサバイト): 10の18乗バイトあるいは、2の60乗バイト

出所) Ericsson Mobility Report (2021June)

https://www.ericsson.com/4a03c2/assets/local/reports-papers/mobilityreport/documents/2021/june-2021-ericsson-mobility-report.pdf

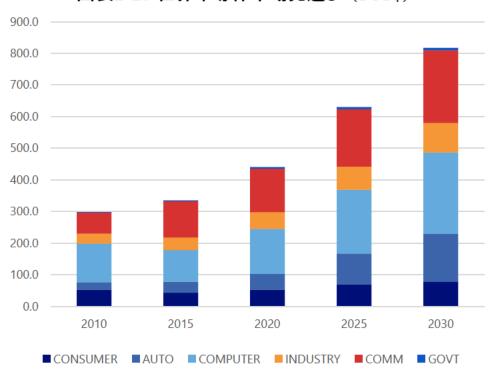

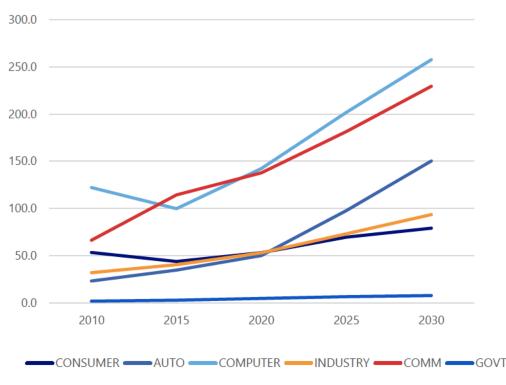

1) 将来技術動向:世界の半導体市場見通し

半導体市場は、2030年 800BUS\$ (104兆円) 市場へと拡大。従来からのコンピュータ、 ミュニケーションに加えて自動車分野が半導体の第3の柱となる。

#### 図表2-27 世界半導体市場見通し(BUS\$)

出所) WSTS 「世界半導体市場統計(2010年-2020年)」を基にNRIにて予測

#### 図表2-28 応用市場別世界半導体市場見通し(BUS\$)

「世界半導体市場統計(2010年-2020年)」を基にNRIにて予測

1) 将来技術動向:半導体ロードマップの整理と後工程及びチップレット実装工程の技術革新

# SoC(System on Chip)3D構造による高集積化 高集積化を続けるLogic LSIの構造変化

デジタル社会の発展に対応するためLogic LSIは、3次元的に高集積化して行く。基本構造は、従来のプレーナー型からFinFETに 進化しており、これがGAA(Gate all around)さらに、CFET(complementary FET)とトランジスタ自体の3次元化が進む。 さらに、30年以降はトランジスタを積層化し、高集積化するものと予想されている。

図表2-29 IRDS2022 Logicデバイスロードマップ

| 量産時期                                                                                 | 2022     | 2025     | 2028             | 2031                | 2034                   | 2037                   |

|--------------------------------------------------------------------------------------|----------|----------|------------------|---------------------|------------------------|------------------------|

| Generation                                                                           | G48M24   | G45M20   | G42M16           | G40M16/T2           | G38M16/T4              | G38M16/T6              |

| Logic Node(nm)                                                                       | 3        | 2.1      | 1.5              | 1.0                 | 0.7                    | 0.5                    |

| 3D Integration                                                                       | Stacking | Stacking | Stacking         | 3DVLSI              | 3DVLSI                 | 3DVLSI                 |

| Structure                                                                            | FinFET   | GAA      | GAA<br>CFET-SRAM | GAA<br>CFET-SRAM-3D | GAA-3D<br>CFET-SRAM-3D | GAA-3D<br>CFET-SRAM-3D |

| FinFET—fin field-effect transistor<br>GAA— Gate all around<br>CFET—complementary FET | Cutor.   | Guiss    | Cuide            | tier tier tier tier | tier tier tier tier    | tier tier tier tier    |

| M0 (nm)                                                                              | 24       | 20       | 16               | 16                  | 16                     | 16                     |

| Gate Pitch (nm)                                                                      | 48       | 45       | 42               | 40                  | 38                     | 38                     |

| Lg Gate Length HP(nm)<br>Lg Gate Length HD(nm)                                       | 16<br>18 | 14<br>14 | 12<br>12         | 12<br>12            | 12<br>12               | 12<br>12               |

| Spacer width (nm)                                                                    | 6        | 6        | <u>5</u>         | <u>5</u>            | <u>4</u>               | 4                      |

| Contact CD(nm)                                                                       | 20       | 19       | 20               | 18                  | 18                     | 18                     |

| Device lateral pitch (nm)                                                            | 24       | 26       | 24               | 24                  | 23                     | 23                     |

| Lateral GAA Vertical pitch (nm)                                                      |          | 18       | 16               | 16                  | 15                     | 14                     |

| Lateral GAA sheet thickness (nm)                                                     |          | 6        | 6                | 5                   | 5                      | 4                      |

| Number of vertical nanosheets                                                        |          | 3        | 3                | 4                   | 4                      | 4                      |

- 1) 将来技術動向:半導体ロードマップの整理と後工程及びチップレット実装工程の技術革新

- SoC(System on Chip)3D構造による高集積化

# 高集積化を続けるLogic LSIとメモリ

- Logicデバイス、メモリともに3次元高集積化が進展する。

- ■特に、NANDは、Tierという積層構造により高集積化を続けており、2021年現在64-97層程度の積層レベル であるが、2030年代には1,000層レベルの積層をターゲットに開発が進められている。

#### 図表2-30 IRDS2022 デバイスロードマップ

| 量産時期                                                                                                                   | 2021                     | 2022                           | 2025                            | 2028                           | 2031                          | 2034                          | 2037                          |

|------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------|---------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Generation                                                                                                             | G51M29                   | G48M24                         | G45M20                          | G42M16                         | G40M16/T2                     | G38M16/T4                     | G38M16/T6                     |

| Logic Node(nm)                                                                                                         | 5                        | 3                              | 2                               | 1.5                            | 1.0                           | 0.7                           | 0.5                           |

| 3D Integration                                                                                                         |                          | Stacking                       | Stacking                        | Stacking                       | 3DVLSI                        | 3DVLSI                        | 3DVLSI                        |

| Structure                                                                                                              | FinFET                   | FinFET<br>GAA                  | GAA                             | GAA<br>CFET-SRAM               | GAA<br>CFET-SRAM-3D           | GAA-3D<br>CFET-SRAM-3D        | GAA-3D<br>CFET-SRAM-3D        |

| Logic cell and Functional Target                                                                                       |                          |                                |                                 |                                |                               |                               |                               |

| M0 ½ Pitch(nm) Gate length(nm) Lateral GAA Min, Thickness(nm) Number of stacked tiers Number of stacked nanosheets Vdd | 15<br>17<br>0.75         | 12<br>16<br>1<br>1<br>1<br>0.7 | 10<br>14<br>3<br>1<br>3<br>0.65 | 8<br>12<br>3<br>1<br>3<br>0.65 | 8<br>12<br>4<br>2<br>4<br>0.6 | 8<br>12<br>4<br>4<br>4<br>0.6 | 8<br>12<br>4<br>6<br>4<br>0.6 |

| DRAM                                                                                                                   |                          |                                |                                 |                                |                               |                               |                               |

| Min half pitch(nm)<br>Cell size(μm2)<br>Strong node cell capacitor Voltage(V)                                          | 17.5<br>0.00184<br>0.5   | 15.5<br>0.00165<br>0.45        | 13<br>0.00118<br>0.45           | 14<br>0.00085<br>0.43          | 11.5<br>0.00062<br>0.4        | 10<br>0.00042<br>0,4          | 10<br>0.00025<br>0.4          |

| NAND                                                                                                                   |                          |                                |                                 |                                |                               |                               |                               |

| 2D NAND ½ pitch(nm)<br>Density(3D)commercialized)<br>Max bit/cell<br>3D NAND Max number of layers                      | 15<br>1T<br>2,4<br>64-97 | 15<br>1.3T<br>4<br>128-192     | 15<br>2.6T<br>5<br>256-384      | 15<br>4T<br>5<br>384-576       | 15<br>6T<br>6<br>576-768      | 15<br>8T<br>6<br>768-1024     | 15<br>12T<br>6<br>1024-1536   |

出所) IRDS 2022 Executive Summary (ieee.org) https://irds.ieee.org/editions/2022/executive-summary

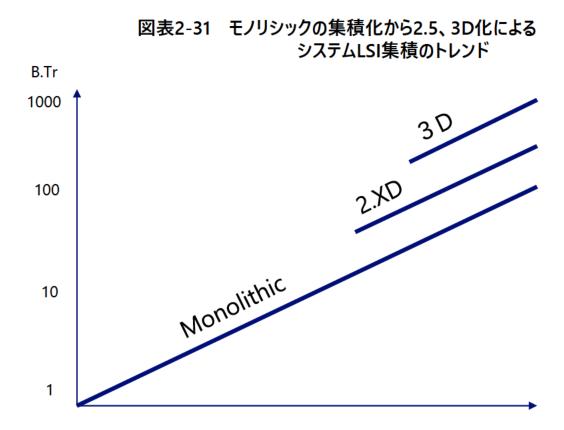

1)将来技術動向:半導体ロードマップの整理と後工程及びチップレット実装工程の技術革新 半導体技術は前工程の進化である「微細化」に加えて、後工程技術の進化をドライビング フォースとする①「2.XD」、②「3D」高集積化が進む。

- 3nmプロセスの量産は2022年に開始、2年で2倍の高集積化が進展している。

- TSMCは3nmプロセスまで従来のFin FET構造を採用。3nmプロセスは5nm比トランジスタ密度1.7倍、演算速度11%、消費電力27%減を実現。

- Samsungは、3nmからゲートオールアラウンド(GAA)構造の採用を計画

- さらに、微細化・3 次元構造進化と同時に、2.XDパッケージング技術等により、チップ単体レベルの数倍以上の高集積化を実現。

1) 将来技術動向:半導体パッケージの高成長

半導体パッケージは2021年に全世界で約3千億個の巨大市場であり、高成長が続く。 中でも、高集積化のキーとなる2.XDパッケージが増加し、FO-WLPが急成長する。

「2022 エレクトロニクス実装ニューマテリアル便覧 (2022年度) 」を基にNRI作成

半導体パッケージ市場規模と成長性 図表2-33 (2021-2028年)

「2022 エレクトロニクス実装ニューマテリアル便覧 出所)富士キメラ総研 (2022年度) 」を基にNRI作成

Copyright (C) Nomura Research Institute, Ltd. All rights reserved. 47

1) 将来技術動向

出所) NRI作成

半導体技術は前工程の進化である「微細化」に加えて、後工程技術をドライビングフォースと する①「2.XD高集積化」、②「3D構造」、③「ヘテロジニアスインテグレーション」に高集積化。

半導体は、従来からの「微細化」という流れだけでなく、パッケージ基板に複数のチップを集積する「①2.XD高集積化」、デバイス をシリコン基板同士接合させ、3次元的な集積化を図る「②3D構造」、さらに、これまでは集積化が難しかった異種デバイスを 集積する「③ヘテロジニアスインテグレーション」によって、高集積化を加速する。

# 図表2-34 エレクトロニクス市場トレンドと半導体集積化技術 将来技術 ← スマートフォン普及期 → ← AI及びマルチクラウドが普及 拡大するビッグデータ社会 ヘテロジニアス インテグレーション 前工程と後工程の融 合による集積化 3 D 2.XD 前工程主導 の集積化 微細化 2010年 2020年 2030年

#### 図表2-35 次世代高集積化技術トレンド

### ヘテロジニアスインテグレーション

**Photonics**

Si-Photonics、基板の光配線 など光電融合化の進展

Power

グリーン化に向けた省エネ、 電化の動きに対応した集積化

**Ouantum**

既存のアーキテクチャを超える 新たな可能性

3D

半導体デバイスを3次元に積層・高集積化することで、 2次元の高集積化の壁を超える

#### 2.XD

デバイスをチップレットとして基板に集積化する技術を進 化させ、デバイスの高パフォーマンス化と低コスト化を実現

# 1) 将来技術動向

「①2.XD」高集積化においては、微細かつ大型の基板への集積化、「②3D」高集積化については多層積層化、「③ヘテロジニアス インテグレーション」では、EV/再エネで利用が拡大するPower、高速伝送のPhotonics、新アーキテクチャーのQuantumなど多様な 技術の集積化が課題となる。

将来の次世代高集積化 図表2-36 次世代高集積化技術ロードマップ 注) 技術で重要となる技術 2010-20年 現状 中期 長期 3-5年 5年後以降 10年後以降 ヘテロジニアスインテグレーション **Photonics** Power Quantum 3 D 積層型 多層積層型 光融合型 2.XD マイクロFan Out Fan Out 微細化による高集積化 High-NA EUV ArF/ArF-i **FUV** NGL

# 2-3.後工程プロセスの将来動向 1)将来技術動向 2.XDパッケージテクノロジーロードマップとコア要素技術

図表2-37 今後の技術要求と要素技術開発(Fan Out)

注)

将来の次世代高集積化 技術で重要となる技術

|      |                   |                                 |                      |                          | 1人間(主女になる)人間          |  |  |  |

|------|-------------------|---------------------------------|----------------------|--------------------------|-----------------------|--|--|--|

|      |                   | 現状                              |                      | 中期<br>3 – 5 年            | 長期<br>5 年後以降          |  |  |  |

|      | 2.XD<br>Fan       | 3,000mm2以上<br>スティチング、50mm角      |                      | 3,500mm2以上<br>55-60mm角以上 | 4,200mm2以上<br>65mm角以上 |  |  |  |

|      | Out               | Build Up                        | L/S 12/9 – 8/8μm     | L/S 5-8μm                | L/S 2-5µm以下           |  |  |  |

| 技術要求 |                   | Si Bridge                       | L/S 2-1μm            | L/S 0.4 – 0.8μm          | L/S 0.3-0.5µm以下       |  |  |  |

| 女水   |                   | RDL                             | L/S 3-4μm            | L/S 2-1μm                | L/S0.5µm以下への挑戦        |  |  |  |

|      |                   | μBump/Cuピラー B                   | ump ピッチ20-30μm       | Bump ピッチ 10 – 20μm       | 5 – 10μm以下への挑戦        |  |  |  |

|      |                   | 光融合                             |                      | Co-package               | e(パッケージの中まで光配線で信号伝達)  |  |  |  |

|      |                   | 基板・パッケージのLarge Fieldを 露光(基板)    |                      | 5μm 500mm角(多層)           | 2μm以下 500mm角 (多層)     |  |  |  |

|      |                   | 微細に加工を可能にする。従<br>の光源・光学系の壁を超える。 |                      | 20μm                     | 5-10μm以下              |  |  |  |

|      | プロセス              | の元派・元子宗の至を起える。                  | 露光(Wafer)            | 0.8μm 55-60mm角以上         | 0.5μm以下 65mm角以上       |  |  |  |

|      |                   | 微細化に伴うパターンの倒れて                  |                      |                          |                       |  |  |  |

| 要素   |                   | 剥がれといった課題を克服し、<br>微細化・高集積化を実現。  | Bump形成・めっき           | 10 – 20μm                | 5-10µm以下への挑戦          |  |  |  |

| 技術   | l                 | スイッチング                          | <br>ブデバイスなど超高周       |                          |                       |  |  |  |

|      |                   |                                 | より光を使った伝送<br>ge化が進む。 | i-Photonics              | Co-Packageの実現         |  |  |  |

|      | <del>1 +</del> 40 |                                 | <b></b>              |                          |                       |  |  |  |

|      | 材料                | 絶縁フィルムの誘電正接を最<br>限の抑える開発が続く。    |                      | Df 0.002以下               | Df 0.0015以下           |  |  |  |

|      |                   |                                 |                      |                          |                       |  |  |  |

# 2-3. 後工程プロセスの将来動向 1) 将来技術動向

# 2.XD基板形成テクノロジーロードマップとコア要素技術

図表2-38 今後の技術要求と要素技術開発(ビルドアップ・サブストレート基板)

注)

将来の次世代高集積化 技術で重要となる技術

|    |                | 現状                                                                                  | 3                            | 中期<br>- 5 年                         | 長期<br>5 年後以降                                                     |

|----|----------------|-------------------------------------------------------------------------------------|------------------------------|-------------------------------------|------------------------------------------------------------------|

| 技術 | L/S<br>Via径    | 12/9 – 8 / 8 μm<br>50 – 30μm                                                        | 2-3年<br>6/6 5/5μm<br>10-20μm | 5年<br>3/3μm<br>5-10μm               | 2/2μm以細<br>5 μm                                                  |

| 要求 | レーザ加工          | CO2レーザ加工                                                                            | UVレーザ加工                      | UVレーザ加工<br>Excimerレーザ加工<br>フォトVia加工 | $\Rightarrow$                                                    |

|    | 誘電正接Df<br>低CTE | 0.004 - 0.002<br>20-10                                                              | 0.002以下<br>同左                | 0.002以下<br>⇒                        | ⇒<br>⇒                                                           |

|    |                | Via径の微細化とともにViaの数の量産性能を追求するには、レー高スループット化を追求。<br>ビアメカ、三菱電機、Spectroni                 | げの短波長化と同時に、                  |                                     | ーザ光の短波長化が必要であり、20μm以降<br>cimer、あるいはフォトビア加エへと移行が必要                |

| 要素 | プロセス           | 最小加工寸法の微細化に伴い。<br>Fieldでの露光プロセスがクリティン<br>露光装置の開発が進む。Cano                            | カルになっており、新たな                 |                                     | 露光プロセス<br>um以下の露光をLargeField(500×500mm)で<br>fうのは困難であり、露光装置の開発が必要 |

| 技術 |                | 微細化に伴いドライプロセスの導り、将来的にスイッチの可能性あ現状、ユニマイクロ、ULVACなど                                     | <i>9</i> 。                   |                                     | Dryプロセス導入<br>微細化を追求していくと、ウェットプロセスの<br>限界が想定され、一部ドライプロセス導入        |

|    |                | データセンター等での超高速スイッ<br>化を実現すると同時に、低消費<br>融合、Si-Photonicsの開発が進<br>現状、Intel・CISCO、IBMなどが | 電力化を実現する光電<br>んでいる。          | 低誘電体新材料                             | 光電融合プロセス導入<br>パッケージ基板への光配線導入。<br>Co-Package化の進展。                 |

|    | 材料             | 個々の材料の限界を追求しつつ<br>形状変化を加味し、パッケージ基<br>した材料の探索が求められる。                                 |                              | デバイスの高速・高周波・                        | 化に対応し、誘電率・誘電正接を極限まで下<br>化に対応した加工性能の材料を開発が必要                      |

# 2-3. 後工程プロセスの将来動向 1) 将来技術動向

# 3 D・ヘテロジニアスインテグレーション・テクノロジーロードマップとコア要素技術

図表2-39 今後の技術要求と要素技術開発(3D)

注)

将来の次世代高集積化 技術で重要となる技術

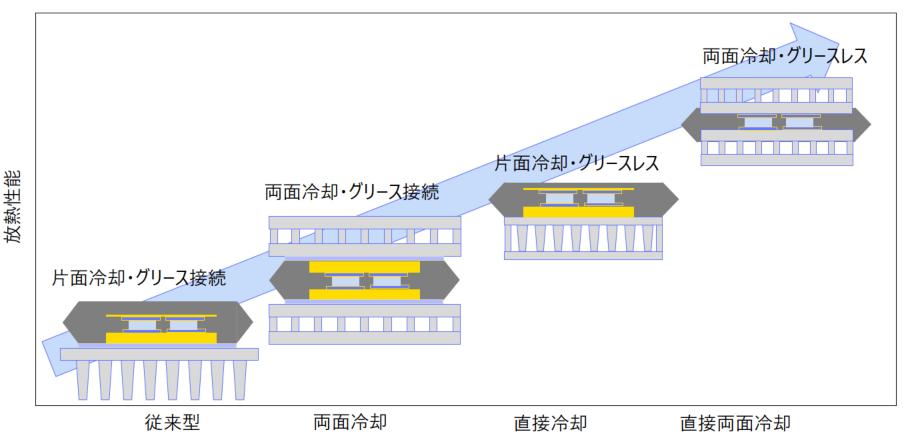

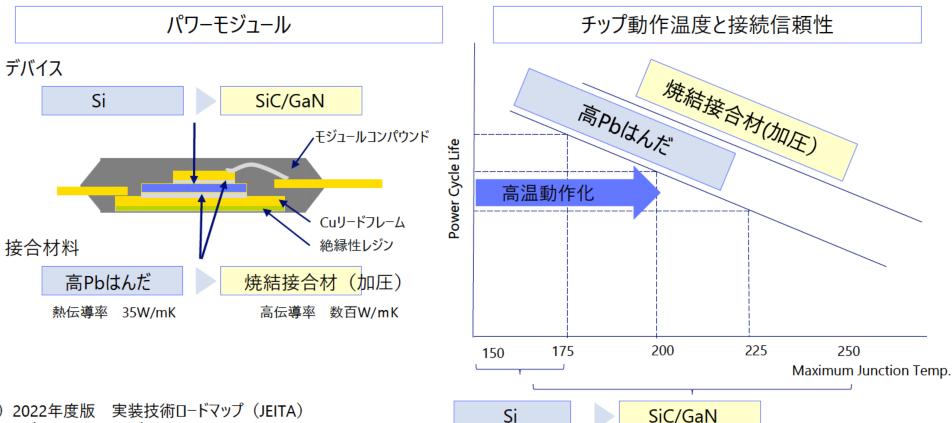

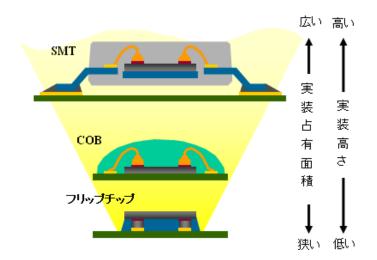

# 2-3. 後工程プロセスの将来動向 1) 将来技術動向 パワーデバイス分野における熱マネージメント 高出力パワーデバイスにおける熱対策が課題となっており、片面冷却から両面冷却、 グリースレス化の傾向がある。

■ 欧州系メーカでは、両面冷却を後押しする企業が多く、日系自動車メーカも採用を行っている。電装部品も増えてくる背景から、 自動車向けではトレンドとなっている。

図表2-40 パワーデバイスの高放熱化動向

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 2-3. 後工程プロセスの将来動向

- 1) 将来技術動向

- 2) 技術開発動向

- 3) 先進事例

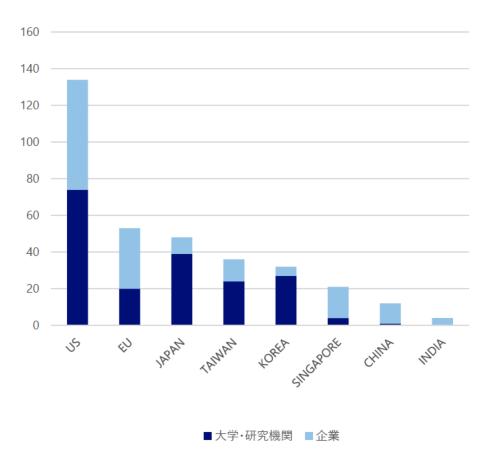

2) 技術開発動向 (2) ECTC2022における発表者勢力分布

日本は後工程の装置・材料で高いシェアを持っているが、先端研究では諸外国が開発を強化している。 ECTCの発表件数Top10には日本企業はなく、TOP30以内に2団体が入るのみ。

図表2-41 ECTC2022 発表論文件数上位

|    | 国         | 企業名                                     | 件数 |

|----|-----------|-----------------------------------------|----|

| 1  | 韓国        | Samsung Electronics                     | 20 |

| 2  | US        | IBM                                     | 15 |

| 3  | SINGAPORE | Institute of Microelectronics (IME)     | 15 |

| 4  | US        | Intel                                   | 14 |

| 5  | 台湾        | ASE                                     | 11 |

| 6  | US        | Georgia Institute of Technology         | 11 |

| 7  | US        | Auburn University                       | 7  |

| 8  | US        | University of Florida                   | 6  |

| 9  | EU        | Fraunhofer Institute (Germany)          | 6  |

| 10 | US        | University of California, Los Angeles   | 6  |

| 11 | 日本        | レゾナック(昭和電工)                             | 5  |

| 12 | US        | Amkor                                   | 5  |

| 13 | 台湾        | Siliconware Precision Industries        | 5  |

| 14 | EU        | IMEC                                    | 5  |

|    | US        | Binghamton University                   | 5  |

| 16 | 台湾        | TSMC                                    | 4  |

| 17 | 韓国        | Electronics Telecommunications Research | 4  |

|    | US        | Texas Instruments                       | 3  |

| 19 | US        | Western Digital                         | 3  |

| 20 | 韓国        | SK -Hynix                               | 3  |

|    | US        | GE                                      | 3  |

|    | US        | Cisco Systems, Inc.                     | 3  |

|    | 台湾        | National Taiwan University              | 3  |

| 24 | US        | University of Texas at Arlington        |    |

| 25 | EU        | Technical University of Berlin          | 3  |

| 26 | 日本        | 大阪大学                                    | 3  |

| 27 | 台湾        | National Cheng Kung University          | 3  |

| 28 | インド       | Indian Institute of Science             | 3  |

| 29 | EU        | Delft University of Technology          | 3  |

| 30 | US        | Air Force Research Laboratory           | 3  |

図表2-42 ECTC2022 発表論文件数の国別分布

出所) ECTC2022プログラムよりNRI集計

# 2-3.後工程プロセスの将来動向 2)技術開発動向 (3) ECTCにおける主要企業の発表動向

図表2-43 ESTC2022における主要な企業の発表及び開発動向

|         | ECTC2022に見る最近の動向                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| TSMC    | InFO、CoWoSの進化系プロセスを開発。Organic Interposer CoWoS-R+を発表。                                                                                |

| Intel   | 2.X、3Dデバイスに注力。独自のDtoWプロセスを新たに開発。                                                                                                     |

| Samsung | ECTCは、他分野で発表を行い最大の発表件数。特徴は、パネルベースプロセスで世界をリード。<br>メモリのハイブリッド接合技術を開発。                                                                  |

| IBM     | Direct Bonded Heterogeneous Integration (DBHi)を発表。光のCo-Packageも発表。                                                                   |

| IMEC    | 2.5D・3D Packageにおいて低温でのプロセスを開発、背面から電源配線をした3Dプロセスを発表。                                                                                 |

| ASE     | Fan Out Packaging向けにHybrid Substrate Integration、RDL for High Performance RF Filter向け<br>Cu-Cu Side by-Side Interconnectionなどを発表。    |

| Amkor   | Substrate Silicon Wafer Integrated Fan Out Technology として、2µmの微細RDLをDual DamasceneをModifyした<br>独自プロセスで形成。感光性絶縁膜をマルチトーン露光し、フォト工程数を削減。 |

| レゾナック   | ポリイミドでの低温ハイブリッド接合を開発                                                                                                                 |

| DNP     | 2μm セミアディティブプロセスによるパネルベースRDL インターポーザを開発                                                                                              |

| 新光電気    | Soldered and Sintered Interconnections分野において、Micro-Voids in Flip Chip Bump on Electromigration Reliability についてIntel、IBMなどと共同発表。     |

出所) ECTC2022プログラムよりNRI集計

# 2-3.後工程プロセスの将来動向 2)技術開発動向(4)ECTCにおける主要企業の発表動向

#### 図表2-44 ECTC2022における主要企業の発表件数

|                                         |                                                                              |    | I[       | DM/ファ      | ァウンドリ | J—     | Tech   | nology | (          | OSAT  |

|-----------------------------------------|------------------------------------------------------------------------------|----|----------|------------|-------|--------|--------|--------|------------|-------|

| Committee                               | Sesson                                                                       | S  | amsur    | ng I       | ntel  | TSMC   | IBM    | IMEC   | ASE        | Amkoı |

|                                         | Advanced Packaging for Heterogeneous Integration and HPC                     |    | <u> </u> | 1          |       | 1      | 1      |        | <u>1</u> 1 |       |

|                                         | Advanced Flip Chip and Embedded Substrate Technologies                       |    |          |            | 2     |        |        | :I C   |            | 1     |

| Dli Tkli                                | Technologies for Heterogeneous Integration, Automotive and Power Electronics |    |          | 1 ,        |       | 2 1    | 2 2    | 2      | 2          | 2     |

| Packaging Technologies                  | Advances in Fan Out Panel Level Packaging                                    |    | ο        | 1 -        |       | 3      | 3      |        |            | _ 3 1 |

|                                         | Advancements in 2.5D and 3D Packaging Technology                             |    | _        | 1          |       | 1      | 1 1    |        | 1          | TI [  |

|                                         | Fan Out Packaging Technologies and Applications                              |    |          | 1          |       | $\Box$ | $\Box$ | ТГ     | 1          | 1     |

|                                         | High Performance Dielectric Materials for Advanced Packaging                 |    |          |            | 1     |        |        |        |            |       |

|                                         | Novel Bonding and and Stacking Technologies                                  |    |          | П.         |       |        | 1      | T      | 1          |       |

|                                         | Enhancements in Fine-Pitch Interconnects, Redistribution Layers and Vias     |    | <u> </u> | 1 ,        |       |        | 1      |        |            |       |

| Materials & Processing                  | Packaging Assembly: Solder, Sintering, and Thermal Interface Materials       |    | _        | <b>-</b> 4 | 1     |        | 1 -    | - 2    |            | _ 21  |

|                                         | Materials and Processes for Fan Out and Advanced Packaging                   |    | -        | ╗          | 1     |        |        | -      |            |       |

|                                         | Processing Enhancements in Fan Out and Heterogeneous Integration             |    |          | 乚          | 1     |        |        | -      | 1          | 1     |

|                                         | Hybrid Bonding and Innovations for 3D Integration                            |    | <b>7</b> | 1          |       |        |        |        | _          |       |

|                                         | Hybrid and Direct Bonding Development and Characterization                   | _  | _        | 1          |       |        | 2      |        | 1          |       |

| Interconnections                        | Hybrid & Direct Bonding Innovation, Optimization & Yield Improvement         |    | 4        | 1 1        |       |        | 5      |        | 1          |       |

|                                         | Soldered and Sintered Interconnections                                       |    |          | 1          | 1     |        | 2      |        |            |       |

|                                         | Advanced Interconnect and Wire Bond Technologies for Flexible Device         | —I |          | _          |       |        | 1 1    |        |            |       |

|                                         | Emerging Modeling Including AI and Machine Learning                          |    |          |            |       |        | 1      |        |            |       |

|                                         | Manufacturing and Assembly Process Modeling                                  |    | -        | 1          |       |        |        |        |            |       |

| Thermal/Mechanical Simulation           | Thermal Management and Warpage Analysis of Highly Integrated Packages        |    | 2 -      | 1          |       |        | 1      |        | 2 2        |       |

| & Characterization                      | Advanced Reliability Modeling and Characterization                           |    |          |            |       |        |        |        |            |       |

|                                         | Modeling and Characterization of Interfaces and Interconnects                |    |          |            |       |        |        |        |            |       |

|                                         | Antenna-in-Package for Communication, Radar and Energy Transfer              |    |          |            |       |        |        |        | 1          |       |

| RF. High-Speed Components &             | Millimeter-Wave Antenna-in-Package: Design, Manufacturing and Tes            |    |          | _ ^        | 1     |        |        |        |            |       |

| Systems                                 | Millimeter-Wave RF Components and Modules for 5G                             |    | 2        | <u> </u>   |       |        | 1 —    | - 1 -  | 2<br>1     |       |

| .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | High-Speed Challenges in Power and Signal Integrity                          |    |          | 1          | 1     |        | 1      |        | 1          |       |

|                                         | Bonding Technology: Novel Assembly Methods and Processes                     |    | <u> </u> |            | 1     |        |        |        | 7          |       |

| Assembly & Manufacturing                | Enhanced Methods & Processes for Heterogeneous Integration Assembly          |    | 3        | 1 3        | 1     | 1      | 2 2    |        | 3          |       |

| Гесhnology                              | Advanced Processes for Manufacturing and Yield Enhancement                   | —Ľ | <u> </u> |            | 1     | 1      |        |        | _ []       |       |

|                                         | Automotive and Harsh Environment                                             |    |          |            |       |        |        |        |            |       |

| Applied Reliability                     | Novel Characterization Techniques and Test Methods                           |    | _        | _ 1        |       | _      |        | 1 _    | 1 1        |       |

| Applied Reliability                     | Interconnection Reliability                                                  |    | _        | _          | 1     |        |        |        |            |       |

|                                         | Flexible, Wearable Sensors and Electronics                                   |    |          | 1          |       |        |        |        | 1          |       |

| Emerging Technologies                   | Al, Quantum Computing and Novel 3D Packaging Solutions                       |    | 2 -      | 1 1        |       |        | 1 1    |        | 2 1        |       |

| ine.gg recimologics                     | Packaging with Additive Manufacturing for Harsh Conditions                   |    | _        |            | 1     |        |        |        |            |       |

| Photonics                               | Novel Photonics Packaging Technology                                         |    |          |            |       |        | 1 1    |        |            |       |

| HOTOTICS                                | 140 ter i notonica i dekaging reciniology                                    |    |          |            |       |        |        |        |            |       |

# 第2章:後工程プロセスの現状及び将来動向

- 2-1. 後工程プロセスの現状及び関連市場動向

- 2-2. 後工程先端プロセスの現状

- 2-3. 後工程プロセスの将来動向

- 1) 将来技術動向

- 2) 技術開発動向

- 3) 先進事例

## 3) 先進事例

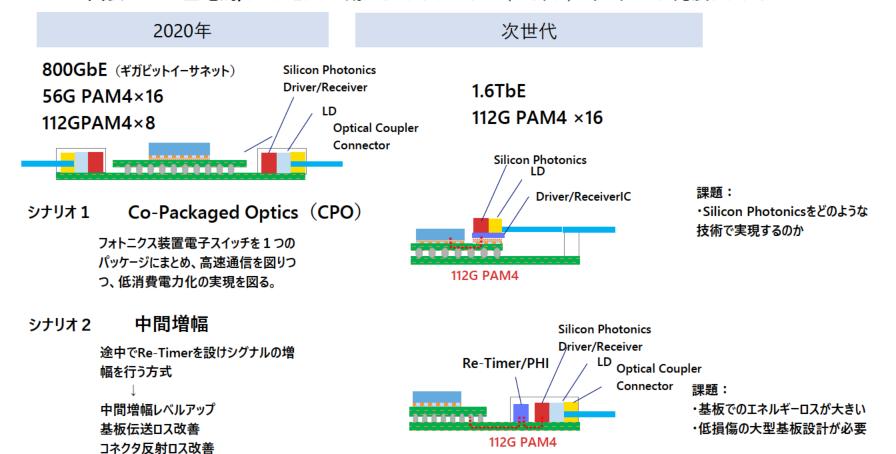

# 基地局/データセンター用ハイエンドデバイス (スイッチ)

- 高速伝送技術において技術革新が必要となっており、光トランシーバ技術「Near Packaged Optics」やパッケージ内の「Co-Package Optics」などが 非常に大きな課題となっている。

- Co-Package Opticsにおいては、次世代高速通信向けに下図のような技術の実現性と同時に、方式検討が行われており、複数の可能性を検討し てゆく必要がある。

基地局/データセンター用ハイエンドデバイス(スイッチ)のパッケージ発展シナリオ

3) 先進事例

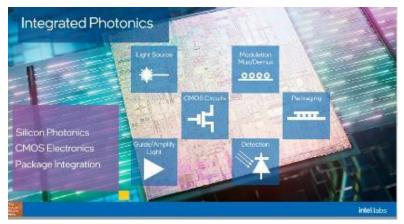

# シリコンフォトニクス(Intelの事例)

- Intelは、データセンター、ネットワーク等の次世代通信技術として、フォトニクス技術開発を強力に推し進めている。

- Intel Labは、2022年6月に8波長分散帰還(DFB)レーザーアレイを含めた、業界最先端を進む多波長集積光モジュールを開発。

- 1つのシリコンウエハー上に発光・シグナル変換・変調・受光並びにコアプロセッサー処理までを完全に統合したデバイスを試作し、業界 の仕様を上回る+/-0.25デシベル(dB)の高出力で、±6.5%の空間均一性を達成している。

#### ■ 革新テーマ

- レーザーアレイは、インテルの300mm シリコン・フォトニクス製造プロセスで設計・製造。

- マイクロリングの電圧コントロールによりシグナル変換

- 8波の異なるレーザー光をシリコン上で集積

- 高密度波長分割多重化 (DWDM) により シグナルの通信を可能に

- 100個以上のマイクロリングを1パッケージに集積

- 発光素子の接合にIII-V族ウエハー・ボンディング接続 プロヤス

#### ■ 次期革新テーマ

現在開発中のビルディング・ブロックには、光の生成、 増幅、検出、変調、CMOSインターフェイス回路、 パッケージ統合テクノロジーなどを集積

図表2-46 Intelのシリコンフォトニクス集積化技術

micro-ring Modulators

8波集積化技術

出所) Intel

上段:https://newsroom.intel.com/wp-

content/uploads/sites/11/2021/04/Labs Day expert session SiPh slides final.pdf 下段:https://www.intc.com/news-events/press-releases/detail/1555/intel-labsannounces-integrated-photonics-research

#### 3) 先進事例

# 量子デバイス

- 2021年11月にIBMは、自社が開催するQuantum Summit 2021において、127量子ビットの「Eagle」プロセッサーを発表。

- 従来型コンピューターを超える量子コンピュータの実現可能性を 示した。

- IBMは、さらにこの技術を用いたシステムをクラウド経由で 利用可能なIBM Quantumサービスを提供することで、全世界で の量子コンピュータの研究を推進している。既に、ドイツの フラウンホーファー研究所、東京大学、クリーブランド・クリニック、 韓国ソウルの延世大学などに設置導入。

図表2-47 IBMの量子デバイス

出所) IBMニュースリリース2021 https://jp.newsroom.ibm.com/2021-11-17-IBM-Unveils-Breakthrough-127-Qubit-Quantum-Processor

- 日本国内においては、NTT、東京大学、理化学研究所、 JSTなどが協力し、量子デバイスを開発を進めており、 2021年12月に光量子コンピューターの基幹技術である 新型の量子光源モジュールを開発発表。

- 入出力の光ファイバーと一体化した「光ファイバー接続型」 構造であり、モジュールと光ファイバー光学系だけで実現 できることが実証。この素子をベースに新たな 量子コンピュータの実現に動いている。

- 2-3. 後工程プロセスの将来動向

- 3) 先進事例

パワーデバイスにおける熱マネージメント

Si IGBT搭載の高出力EV用インバータでは、両面冷却、フィンや水冷機構が導入されている。 一方、動作許容温度が高いSiCを採用し、片面で冷却機構を簡素化する事例も増えている。

図表2-48 EV用インバータ向けパワーデバイスにおけるパッケージ

|      | ポルシェ Taycanのケース                       | Tesla Model3のケース                                            |

|------|---------------------------------------|-------------------------------------------------------------|

| 冷却方式 | 直接両面冷却                                | 片面冷却                                                        |

|      | 個々の両面に冷却水が流れる方式                       | 水冷方式                                                        |

|      | Taycan用インバーターのパワーモジュール                | Model3用インバーターのパワーモジュール                                      |

|      | ヒートシンク<br>リード端子<br>サ                  | Cuリード   封止樹脂     Al線   Pb入高温はんだ     SiCチップ   Ag焼結     DBC基板 |

|      | 鉛フリーはんだ Si Si 内層Cu 絶縁樹<br>IGBT Di 箔 脂 | ヒートシンク                                                      |

3) 先進事例

# パワーデバイスにおける熱マネージメント

# 動作温度が高いSiCを採用し、熱伝導性の高い焼結接合材料を採用が進む。

- SiCを採用することで動作許容温度を高くすることが可能となる。現在、ハイエンドのEV自動車では、SiCの採用が増加しており、 接合材料も鉛はんだから焼結接合材料にシフトしつつある。環境対策の上でも、鉛の使用は削減される方向にある。

- 焼結接合材料は、高温での信頼性を上げると同時に、熱伝導度も高くできるため、このトレンドは続くものと予想される。

#### パワーモジュールにおける接合材料の変化 図表2-49

出所) 2022年度版 実装技術ロードマップ (JEITA) レゾナックホームページ

# 第3章:後工程材料・装置の現状及び将来動向

- 3-1. 後工程材料・装置の市場動向

- 3-2.後工程材料・装置の現状

- 3-3.後工程材料・装置の将来動向

- 1) 半導体後工程・パッケージ主要材料

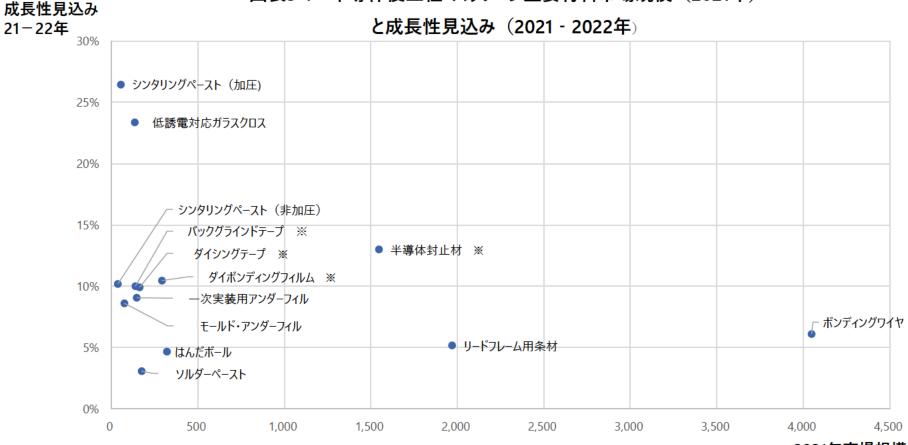

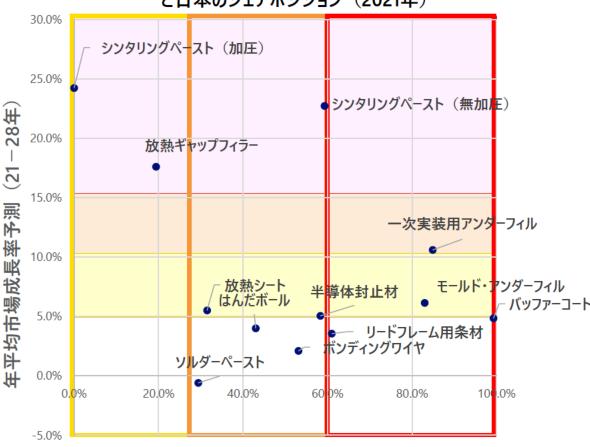

- ①規模と成長性

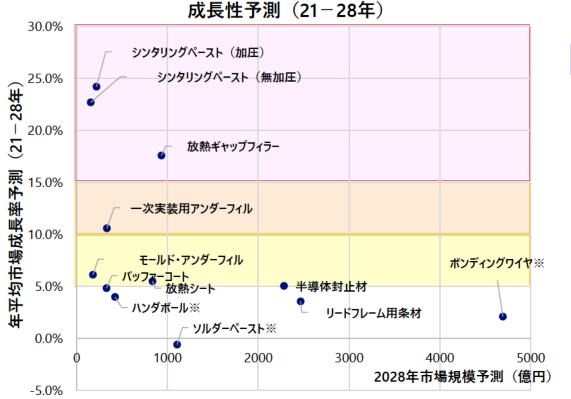

- 成長が著しいのが、放熱特性に効くシンタリングペースト(加圧)、高周波デバイスでニーズのある低誘電体ガラスクロスなどがあげら れる。一方、旧来から使用されてきたボンディングワイヤ、リードフレーム条材、はんだボールなどは、比較的低位の成長にとどまっている。

半導体後工程・パッケージ主要材料市場規模(2021年)

2021年市場規模(億円)

出所)※:富士経済「2022年 半導体材料市場の現状と将来展望(2022年度)(2021年/2022年予測)」及び 富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧(2022年度) (2021年見込/2022年予測) Jを基にNRI作成

- 1) 半導体後工程・パッケージ主要材料

- ②日本のシェア

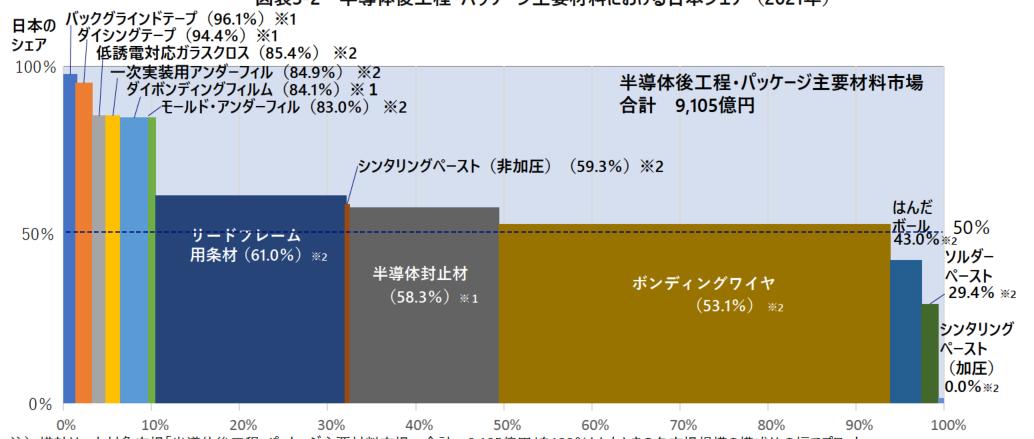

- 半導体後工程・パッケージ主要材料において、日本は、多くの製品で非常に高い市場ポジションを占めている。

- 特に、グラインドテープ、ダイシング、低誘電体ガラスクロス、一次実装用アンダーフィル、ダイボンディングフィルム、モールド・アンダーフィルは、市場の80%以上 のシェアを持ち、非常に重要な供給先となっている。

- リードフレーム、半導体封止材、ボンディングワイヤ、はんだボールなど汎用的で量を必要とする部材では、韓国・台湾・欧米の需要先市場での企業が育って いる。 図表3-2 半導体後工程・パッケージ主要材料における日本シェア(2021年)

注)横軸は、本対象市場「半導体後工程・パッケージ主要材料市場 合計 9.105億円」を100%としたときの各市場規模の構成比の幅でプロット、 左にある市場程、日本の市場シェアが高い順に配置。

出所)※1:富士経済「2022年半導体材料市場の現状と将来展望(2022年度)」

※2: 富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧(2022年度) |を基にNRI算出

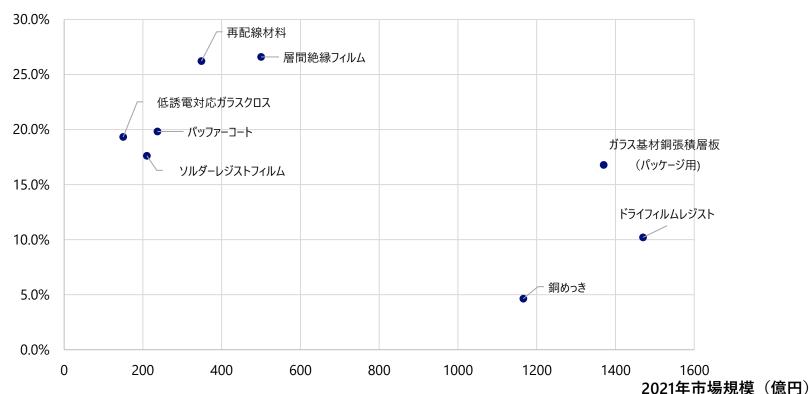

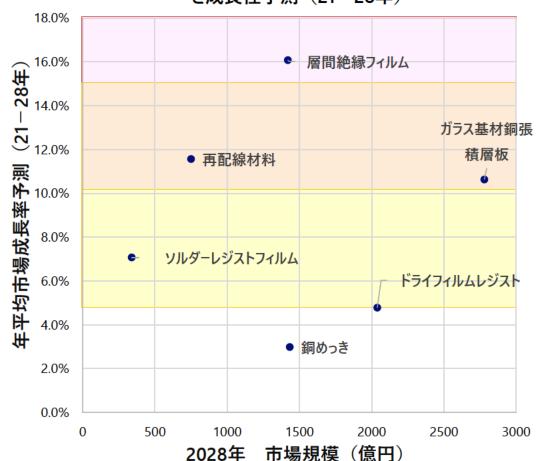

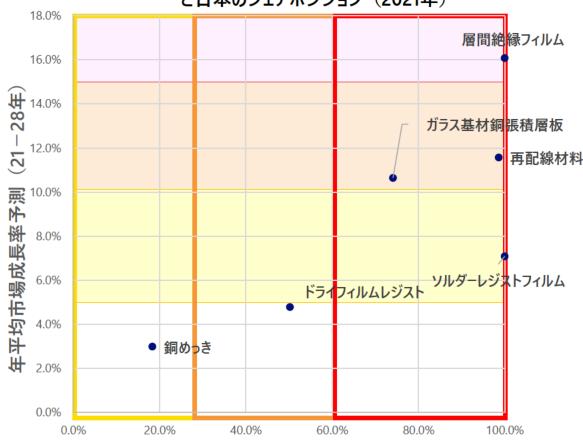

- 2) パッケージ基板材料

- ①規模と成長性

- ■パッケージ基板材料は、20%前後の成長を遂げており、半導体需要拡大に応じて高い成長を遂げている。

- ■中でも、2.XDやFan Outプロセスなどの増加により、RDLで必要な再配線材料、パッケージ基板の高周波特性と 絶縁性能を決める層間絶縁フィルムなどが特に高い成長を遂げている。

図表3-3 半導体パッケージ基板関連材料の市場規模(2021年)

成長性見込み 21-22年

と成長性見込み(2021 - 2022年)

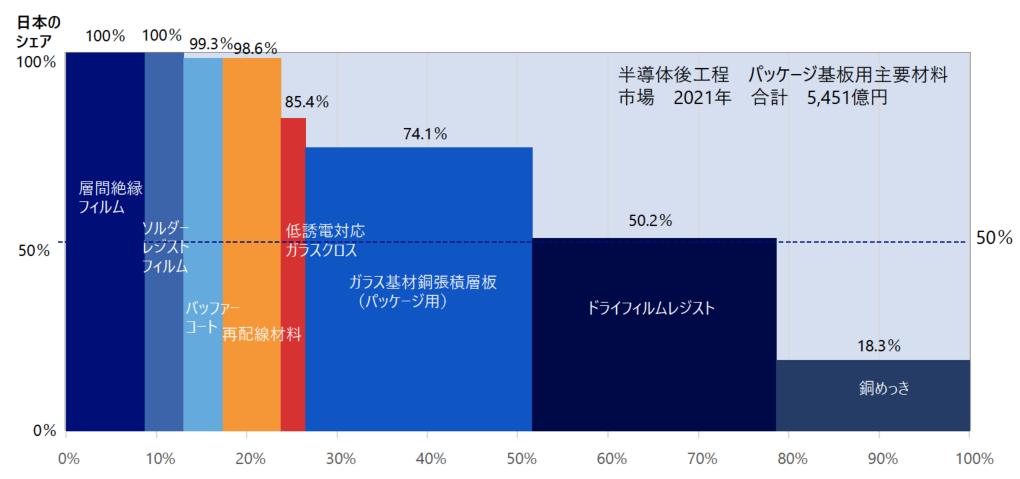

- 2) パッケージ基板材料

- 日本のシェア

図表3-4 半導体後工程 パッケージ基板関連主要材料における日本シェア(2021年)

注)横軸は、本対象市場「半導体後工程 パッケージ基板用主要材料市場 2021年 合計 5,451億円」を100%としたときの各市場規模 の構成比の幅でプロット、左にある市場程、日本の市場シェアが高い順に配置。

出所) 富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧(2022年度)」を基にNRI算出

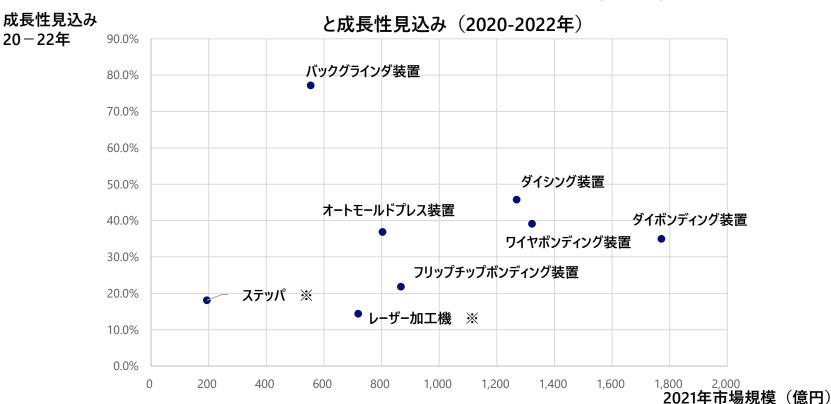

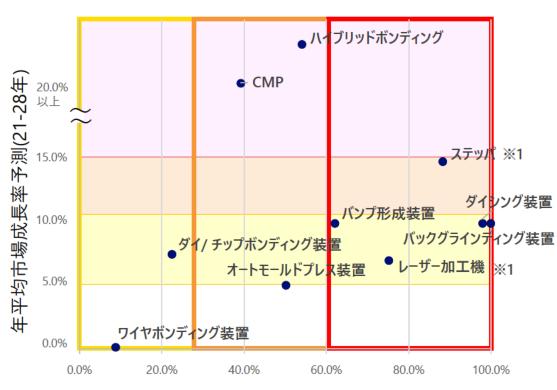

- 3) 半導体後工程関連の装置市場

- ①規模と成長性

- 足元の成長では、全市場平均で30%強の成長を遂げており、極めて高い成長市場である。

- 平均30%を超える成長を遂げているのは、バックグラインダ装置、ダイシング装置、オートモルドプレス装置、ワイヤボンディング装置、 ダイボンディング装置等がある。

図表3-5 半導体後工程主要装置市場規模(2021年)

出所) GNC「世界半導体製造装置・試験/検査装置市場年鑑2022(2022年度)(2021年/2022年見込) |及び 富士キメラ総研「2022 エレクトロニクス 実装ニューマテリアル便覧(2022年度)(2021年/2022年見込) |基にNRI作成

- 3) 半導体後工程関連の装置市場

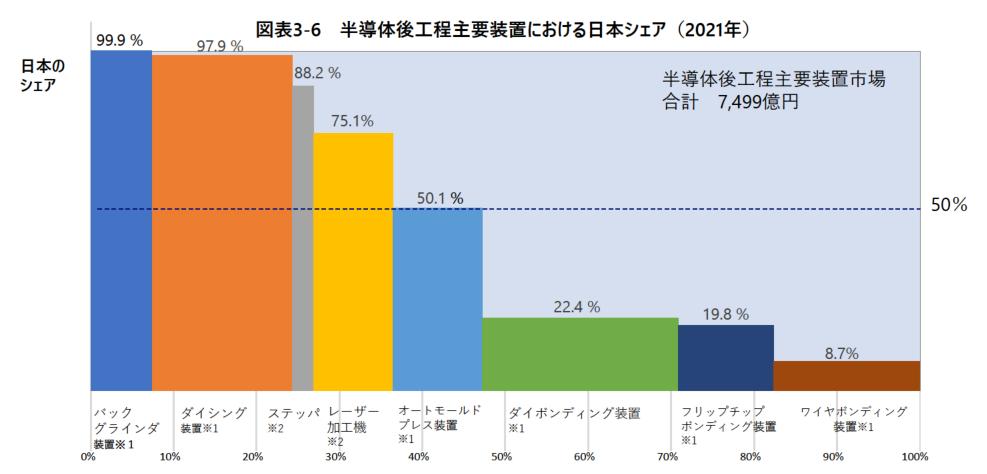

- 日本のシェア

- 横軸に半導体後工程における主要装置の合計市場7,499億円を100%とし、主要装置の市場規模の占める比率を示す。 縦軸を日本企業のシェア合計をプロットした。

- 日本は、後工程において50%を占める有力装置を持つ一方で、市場の半分を占めるボンディング装置においては、海外の後塵を拝する状況にある。

注)横軸は、本対象市場「半導体後工程主要装置市場 合計 7,499億円」を100%としたときの各市場規模の構成比の幅でプロット、左にある市場程、 日本の市場シェアが高い順に配置。

出所)※1:実績値GNC「世界半導体製造装置・試験/検査装置市場年鑑2022 (2022年度) |

※ 2 :富士キメラ総研「2022 エレクトロニクス実装ニューマテリアル便覧(2022年度)」を基にNRI算出 Copyright (C) Nomura Research Institute, Ltd. All rights reserved. N 70

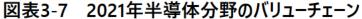

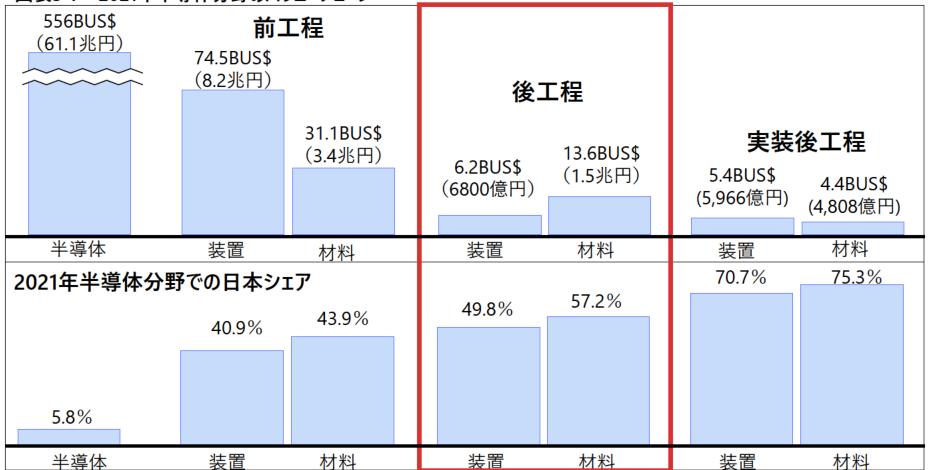

4) 競争状況

今後の半導体高集積化のドライビングフォースとなる後工程において、日本は高いシェアを 確保しており、その発展に重要な役割を担っている。

出所)半導体:WSTS 「世界半導体市場統計(2021年)」、前工程製造装置: GNC 「世界半導体製造装置・試験/検査装置市場年鑑2022 (2022年度)」、 前工程材料:富士経済 「2022年 半導体材料市場の現状と将来展望(2022年度)」、後工程・装置・材料及び

実装工程装置・材料:富士キメラ総研「2022及び2021 エレクトロニクス実装ニューマテリアル便覧(2022・2021年度)」、富士経済「「2022年 半導体材料市場の現状と 将来展望(2022年度) |及びGNC「世界半導体製造装置・試験/検査装置市場年鑑2022 (2022年度) |を基にNRI算出

注: 為替レート 1US\$=110円

## 3-1.後工程材料・装置の市場動向

4)競争状況

先端半導体メーカは、2.XD・3D技術の開発に注力し、前工程・実装工程の企業が 参入をし、開発競争が激化している。

図表3-8 半導体後工程における市場革新の現状

出所)半導体:WSTS「世界半導体市場統計(2021年)|、前工程製造装置: GNC「世界半導体製造装置·試験/検査装置市場年鑑2022(2022年度)|、 前工程材料:富士経済 「2022年 半導体材料市場の現状と将来展望(2022年度) 」、後工程·装置·材料及び実装工程装置·材料:

富士キメラ総研「2022及び2021 エレクトロニクス実装ニューマテリアル便覧(2022・2021年度)」、富士経済「2022年 半導体材料市場の現状と将来展望(2022年度) |及び

GNC「世界半導体製造装置・試験/検査装置市場年鑑2022 (2022年度) |を基にNRI算出

注:為替レート 1US\$=110円

## 3-1.後工程材料・装置の市場動向

### 4)競争状況

## 学会発表及び市場上位企業・団体等のマッピング

■ 各国は、私企業のみならず、公的研究機関・大学を上げて後工程の開発を加速

#### 図表3-9 後工程関連学会・主要機器材料市場にみる世界の主要開発機関の分布

- 1) 半導体後工程・パッケージ主要材料

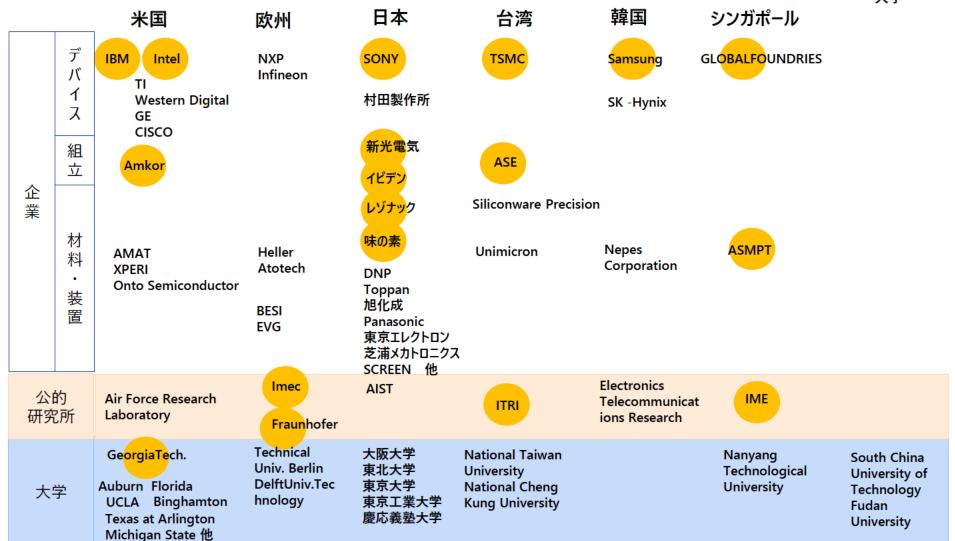

- バックグラインドテープ:主たる用途及び技術動向

#### <主たる用途>

- 半導体のウェハプロセスを完了し、配線、Bumpなどを形成後、ウェハを 薄化する工程で使用される。

- 素子や配線、Bumpを保護しつつ、バックグラインド工程の圧力による 破壊や欠陥を防ぐ。加工工程では、Bumpなどで生じる表面を埋める 追従性が高い一方で、剥離段階では、Bumpなどを破壊しない 剥離性の高い材料が使用される。

- バックグライディング工程における保護力と剥離時の容易性を保持する ため、UVあるいは熱などによりテープの接着力をコントロールするため、 下記の製品タイプがある。

- UVタイプ :紫外線(UV)照射により、フィルムの弾性率が上昇すると同 時に、体積が収縮し、粘性が低下し、剥離しやすい性質を持つ材料。

- 非UVタイプ:弱粘着剤を使用するタイプ。

#### 図表3-10 UVタイプの使用例

- バックグラインドテープは、グラインド工程における保護材料であり、WLP などプロセスの高度化、表面のBump構造の微細化などに対応して、 材料レベルからの開発・改良が進められている。

- Bumpの微細化、狭ピッチ対応

- Bumpの直径は、従来の100μmオーダーから数十μm、10μm クラスまで微細化が進んでいる。微細化が進展すると、Bump 自体の剛性が失われる他、加工時にBumpが倒れる、はがれ るといった欠陥を生じる。こういった欠陥を削減する材料の開発 が各社進められている。

- 低パーティクル性

- パターンの欠陥につながるパーティクルの発生を抑制し、発生し た場合の除去性能などを考慮した材料開発が必要。

- 気密性

- 物理的な衝撃・圧力への保護だけでなく、グラインド工程におけ る水の浸透やそれによる表面の劣化などを防止するため、工程 で使用する薬液、水、ガス等の浸食を防止する気密性を確保。

- 耐熱性

- パワーデバイスやディスクリートなど、ウェハ裏面のウェット処理や 金属成膜の工程におけるウェハ温度の上昇に耐える材料の 開発。

- 1) 半導体後工程・パッケージ主要材料

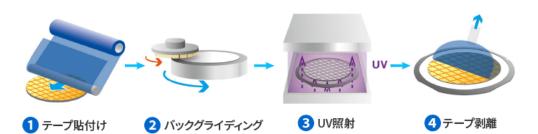

- ② ダイシングテープ:主たる用途及び技術動向

#### <主たる用途>

- ダイシング工程におけるウェハ及びウェハ上のチップの固定を目的に使用 されるテープ。テープの強度を確保するベースフィルムの上に、ウェハを固定 する粘着層を持つフィルムであり、使用する直前に、剥離(離型) フィルムを剥がして使用する。

- ダイシングフレームまで覆う必要があるため、バックグラインドテープよりも 2-3割大きなフィルムとなっている。 ダイシングテープは、 剥離する際には 粘着力を弱め剥離するが、ダイシング時のブレードの研削力により 飛び散らないような強い粘着力が必要。

- 製品品種としては、バックグラインドテープ同様に、①UV硬化タイプと ②非UVタイプがあるが、量的には、UV硬化型がメインとなっている。

#### 図表3-11 ステルスダイシングとダイシングテープの使用例

出所)リンテックホームページ

https://www.lintec.co.jp/dream/tsunagu/technology/18/modal02.html

#### <技術動向>

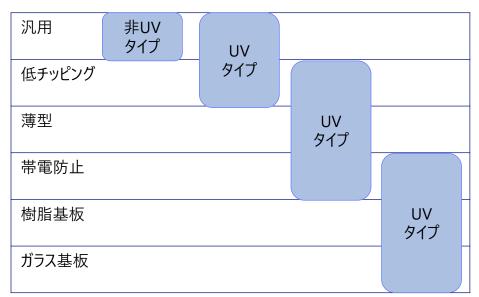

- ダイシングテープは、加工プロセスと対象物により、求められる要求が異 なるため、用途により使い分けが行われている。

- 薄型基板用UVタイプ:デバイスは、モバイル用途などで低背化が図ら れ、ウェハの薄型化が進められてきた。このため、従来型の汎用的なもの から、薄型ウェハに対応した強度と素子ダメージを防ぐための帯電防止 機能のついたフィルム。

- パッケージ基板などの樹脂基板やガラス基板向けUVタイプ:基板の 加工工程に適応した構造と強度を持ちつつ、素子ダメージを防ぐための 帯電防止機能のついたフィルム。

図表3-12 ダイシングテープの用途と使分け

出所) 日東電エホームページ

https://www.nitto.com/jp/ja/products/semicon/dicing001/

- 1) 半導体後工程・パッケージ主要材料

- ③ ダイボンディングフィルム:主たる用途及び技術動向

#### <主たる用途>

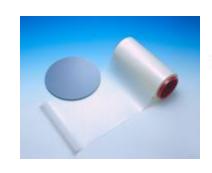

- ダイボンディングフィルムは、ダイとダイ、あるいは、ダイと基板を接着・ 固定するために使用されている。メモリなど、多段積層化が進む半導体 チップの接着には、超薄型フィルム状接着剤が使用されている。

- 樹脂液でなく、フィルムを使用するのは、加工工程をシンプルにし、かつ、 平坦な接着を実現し、接着後のはみだし等を無くす効果がある。

- 構造としては、薄型でも、フィルムの特性を出す、積層構造になっており、 基材に柔軟性に優れるアクリルポリマやポリオレフィンなどを使用し、 接着・固定に接着性に優れるエポキシ樹脂などを使用し、薄型で 柔軟性と接着性を維持したフィルムが使用されている。

#### 図表3-13 ダイボンディングフィルムの使用例

#### <技術動向>

- ダイボンディングフィルムは、デバイスの組立工程における接合材料であり、 シンプルで信頼性の高いプロセスを実現する上で必須な材料となっている。 そのため、デバイスの低背化・薄型化、多層化などへの対応などに対応して 改良が進んでいる。

- デバイスの低背化に対応した薄型化

- ダイの固定に使用されるが、デバイス自体が薄くなる中で、接合 を担うダイボンディングテープ自体の厚さが課題となり、超薄型の フィルムが求められてきてる。10μmを下回るものも開発され、 実用化されている。

#### 高信頼性

- ダイボンディングフィルムは、デバイスの実使用に足る高い信頼性 の確保が必要であり、そのためには、低弾性率と高い接着性の 両面を持つ必要がある。しかし、相矛盾する性質であり、 単一膜では実現が困難なことから、個々の特性を保持した 樹脂の積層化が必要となっている。

- ダイシングとの複合プロセス

- ダイボンディングは、ダイシング工程の後、ダイをピックアップし、 基板に実装する工程で使われる。一方、ダイシング工程で ダイシングテープを使用し、剥離後、ダイ及び基板との接合の際 には、新たにボンディングフィルムに接着する必要があり、工程数 が長くなるディメリットがある。そのため、ダイシングとダイアタッチ のフォルムを積層し、一連のフィルムで実現できるフィルムDDAF (ダイシングダイアタッチフィルム) が近年拡大している。

- 半導体後工程・パッケージ主要材料

- ④ 半導体封止材:主たる用途及び技術動向

<主たる用途>

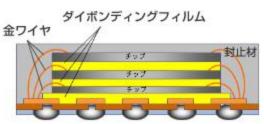

- 半導体封止材は、ICからディスクリートまで使用される材料であり、 半導体を樹脂で覆うことでデバイスを空気や湿気、光や熱、物理的な 衝撃などから保護する材料である。

- 封止材の主たる材料は、エポキシであり、エポキシをベースマテリアルとして、 シリカフィラーなどを混ぜ込み、熱伝導度などを調整し使用する。

- エポキシ樹脂は、従来からノボラック系やビフェニル系のエポキシが用いられ てきたが、ハロゲンフリー化に対応するために、ビフェニルアラルキル骨格を 含む難燃性エポキシやファインピッチ化に対応して低粘性の材料など改良 が進んでいる。

- 封止方法により2つのタイプに分かれる。

- トランスファーモールド:従来から用いられてきた方式であり、 プランジャーと言われる容器で、一旦溶融した樹脂をチップ配置し たキャビティに充填し、固化させる方式。樹脂を射出成型する方式。

- コンプレッションモールド:キャビティ内の樹脂を圧着する方式で、樹 脂の流動がほとんどなく、チップやワイヤ等配線への負荷を最小限 に抑えることが可能なプロセス。

#### 図表3-14 封止材の熱伝導特性

出所)住友ベークライトホームページ https://www.sumibe.co.jp/solution/loT/5G/emc.html

- 半導体封止材に求められるニーズと技術トレンド

- 対環境対応

- ハロゲンフリー材料、加工プロセスの採用

- フロンを使用しない難燃性材料の使用

- その他、環境負荷を最低限とする開発は今後も継続

- 低温硬化,低応力,低収縮率

- WLP、PLP向け封止材は、加工時における変形を無くす ため、低温硬化、低応力・低収縮率の材料が求められる。

- 高放熱特性

- 現状3W/mkクラスの熱伝導度の材料が採用されている が、さらなる高放熱特性の材料へのシフトが求められてお り、2025年以降には、10 W/mkクラスの開発がターゲット。

- 低損失·低誘電

- 5 Gミリ波など高周波デバイスには、極限まで誘電率・ 誘電正接を下げた材料が求められている。

- 1) 半導体後工程・パッケージ主要材料

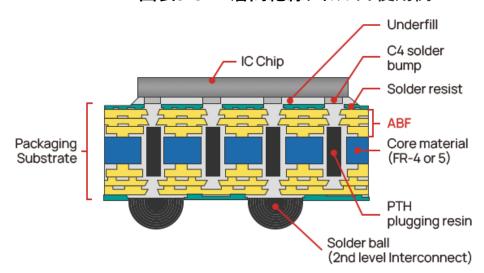

- モールド・アンダーフィル:主たる用途及び技術動向

#### <主な用途>

- モールド・アンダーフィルとは、集積回路の保護を目的とした封止 と、集積回路と基板間まで覆うアンダーフィルの両機能を備えた 材料のことである。

- なお、一次実装用アンダーフィルは、ダイとパッケージ基板とのBump接合 を保護する目的でダイと基板の間に浸透させ固める材料であり、チップの 上面までを覆うモールドの機能を持たない。

- モールド・アンダーフィルはフリップチップ実装に採用されており、 その利点は封止工程及び一次実装用アンダーフィルを一括で 行うことによる工数の削減並びにコスト削減につながる可能性がある。

- 20µm以上の狭ギャップに対応しており、モバイル向け・目盛り向けのCSP パッケージ、モジュールパッケージなどに採用されている。

#### 図表3-15 モールド・アンダーフィルを利用したパッケージイメージ

出所)新光電気ホームページ https://www.shinko.co.jp/product/package/assembly/muf.php

- 製造工程は半導体封止材と違いは少ないが、より狭ギャップ に対応できるようにフィラー充填率7割超程度と高い点に加え、小径フィ ラーを採用している点が特徴である。

- 狭ギャップ対応: 粒径は20µmが主流であるが、モバイルや目盛り向け への供給のために狭ギャップ対応のニーズが高まっており、 中には7μm程度の粒径ニーズが発生しており、 各社粒径の縮小化のための技術開発が求められる。

- ハイエンドスマートフォン向けアプリケーションプロセッサやDRAM向けに 対応するため、高放熱性が近年求められつつある。

- 高放熱対応: 現在は3W/m・K程度に対応したものが主流であるが、 5W/m・K程度への対応要求が発生してきている。 放熱性の向上のために、フィラーの充填率を高める必要があるが、 フィラーメーカにも限りがあるため、技術開発だけでなく供給体制の 確保も課題となる。

- また、5Gの普及等に伴い、近年ミリ波のアンテナ・イン・パッケージ (AiP) 向けで誘電正接 (Dissipation factor) 0.001程度の要求を求められる 場合が出始めている。

- 1) 半導体後工程・パッケージ主要材料

- QFN(Quad Flat Non-leaded package)リードフレーム:主たる用途及び技術動向

#### <主たる用途>

- QFNタイプのパッケージは、外部接続のリードがパッケージの外側でなく 内側にあるため面積が小さく、半導体チップを固定するダイパッドを樹脂 で封入するタイプの半導体パッケージに比べて放熱性が高い。

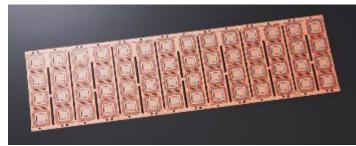

- このQFNタイプのパッケージに使われるリードフレームには、チップ性能の 向上に関わる"小型・多ピン化"に対応する高精度な加工と銀めっき エリアの形成が必要である。また車載用のパッケージでは水分の侵入を 抑える高い信頼性が求められる。

- また、近年は、WLPのパッケージにも利用されており、外周部だけで接点 を持つものではなく、多列構造でコンタクトを増やした構造のものが使用 され、需要を押し上げている。

図表3-16 リードフレームの使用例

出所)DNPホームページ https://www.dnp.co.jp/news/detail/10161604\_1587.html?from=rss

注) QFN: Quad Flat Non-leaded package

#### <技術動向>

- OFNリードフレーム材に求められるニーズと技術トレンド

- 高集積化に伴うリードピッチの微細化推進

- 現状リードピッチは、0.18 0.2mmが中心であるが、 高集積化とともに微細化が進み、0.16 - 0.18mmに 移行するものとみられている。また、ICの多ピンかに伴い リードも1列か2-3列の多列化も使用されている。

- QFN内に実装されるICはワイヤーボンディングだけではなく、 スマートフォンではRF ICのWL-CSPも実装されている。

- 低背·薄型化

- モバイル機器の普及により、薄型に対するニーズは強く、 今後も薄型が求められる。低背化のため、リードフレーム 自体の薄型化、ボンディングワイヤの低背化、構造の シンプル化と薄型化などが進められている。

- 小型・多ピン化に対応した高精度銀めっき

- パッケージ電極をパッケージ周辺部に配置するが、パッケー ジ端部分でめっきの位置がずれ、それによる気密性の 低下、水分の進入などにより欠陥を生じる可能性がある。 この対応策として、パッケージ端面までのめっき加工精度を 向上することで、デバイスの長寿命化がはかることができる。

- 封止材と銅リードフレーム等の密着性を高める粗化技術

- パッケージは、パッケージ内のLSIダイは元より、配線材料 などの酸化を防止するため、密着性を高める必要がある。

- 放熱特性の向上

- リードレスであり、リードがチップからはみ出さない構図を 持ち、チップの面積が非常に小さい特徴を持つ一方で、 デバイスの高集積化が進んでいるため、狭いスペースで 優れた放熱特性が必要となる。

Copyright (C) Nomura Research Institute, Ltd. All rights reserved. 79

- 1) 半導体後工程・パッケージ主要材料

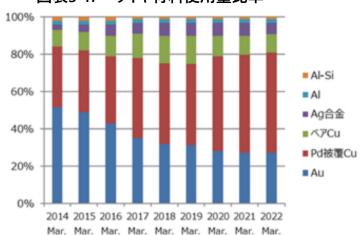

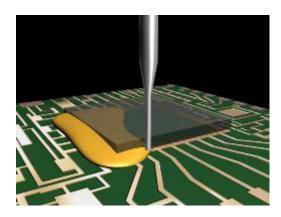

- ボンディングワイヤ:主たる用途及び技術動向

#### <主たる用途>

- ボンディングワイヤは、2010年頃まで金が主流であったが、金の高騰に 対抗し、金ワイヤの代替品として、銅ワイヤ、パラジウム被膜銅(PCC) ワイヤ、銀あるいは銀合金ワイヤへの移行がおこる。2007年には、 パッケージメーカに出荷されたボンディングワイヤ160億メートルの内、 金ワイヤは約98%を占めたが、2013年までに、その割合は総出荷量の ほぼ半分にまで下落。2014年に出荷された200億メートル超のボンディング ワイヤのうち、金ワイヤの比率は44%にまで低下。その後も、金の構成比率 は低下を続けている。

- Au:ハイエンド製品、高信頼性かつ低ループ構造で使用

- Cu及びCu合金:低コスト。金ワイヤの10分の1

- Ag合金:金ワイヤの代替として使用。反射率からLED等に使用

- 大電流などパワー系で使用

図表3-17 ワイヤ材料使用量比率

- ボンディングワイヤに求められるニーズと技術トレンド

- 低コストのCuでの高性能・高信頼性

- Cu配線は、金に代わる材料として普及。一方で、酸化に よる劣化の問題、ループ形状などに抱えており、これを 打開するため、パラジウム被膜銅(PCC)をはじめ、 最適化が図られている。

- リサイクルシステム

- ボンディングワイヤは、貴金属であり、高価な資源である。

- そのため、半導体製造工程で生じるロスを最小限にする ことでコストダウンになるいだけでなく、対地球環境・ 資源問題に応えることが可能。それに向けた再生率、 再生純度の向上などが図られている。

- 設備と材料のトータルコスト削減

- 金を銅配線にすることで、材料コストは劇的に削減が 可能だが、装置コストは高くなるというジレンマがある。

- そのため、金のような高品質で、加工性に優れた材料で ありながら、設備負荷が大きくならないプロセスの導入。

- Ag合金あるいは、PCCなどAuに代わる新たな材料の開 発ニーズは今後も継続。

- 自動車など高温かつ振動など過酷な環境下に適したワイヤ

- 耐湿性に優れ、大電流などにも適合するAIがパワー系で 使用されているが、ファインなパターンには不向きである。

- こうしたニーズに適合した材料の開発は、クルマのEV化の 進展により加速するものと予想される。

- 1) 半導体後工程・パッケージ主要材料

- めっき (銅めっき/金めっき):主たる用途及び技術動向

#### <主たる用途>

- めっきは、パッケージ基板の配線をつなぐビア及び基板の上位レイヤーの 再配線層及び基板と基板を接合するBumpの形成に使用されている。

- めっきの代表的なプロセスとしては、シード層を形成した後、配線の銅を めっきで成長させ、さらに、銅の保護膜であり、接合を助けるNi、Pd、Au などの薄膜を形成する。

- 銅の厚膜や埋込みには、膜厚成長速度の制御が容易な電解めっきが 使用され、膜質の高い薄膜形成には、無電解でのめっきが使用されること が多い。さらに、めっきは、配線の主要材料の銅のみならず、Ni、Pd、Au やその合金を積層する必要があり、これを量産性高く微細に加工する プロセスには各社のノウハウが蓄積されている。

#### 図表3-18 パッケージ及び実装に使用される銅めっき工程

# ビア及び再配線層 バンプ 30 µm 10µm 20µm Cu Bump Dielectric Nix Auかっき Fine trace ENEPIG(Ni/Pd/Au)

#### <技術動向>

- めっき市場に求められるニーズと技術トレンド

- 10µmの壁を超えるBump形成

- 現状 量産のBumpは、20-15μクラスが先端であり、開 発レベルで10μmサイズに迫りつつある。一方で、Bumpを 微細化すると埋込みパターンとして形成したレジストの 側壁の傾斜や底のにじみが影響し、底の設置面積が狭く なり、シード層除去の際に、Bumpが倒れるなどの欠陥を 生じやすくなる。このため、10µmクラスのBump形成の ためには、ドライフィルムレジストのシャープな加工性と細い 穴へのめっき液の浸透のための薬液及びその循環のため の浴槽の改良が必要となる。

- さらに、Bumpは、5µmクラスまでの微細化が期待されて おり、プロセスを改良し、極限を追求できるかどうか期待 されている。

#### 小径ビアの穴埋め

- 銅の積層配線レイヤ間をつなぐビアは、パッケージ基板と なるビルドアップ基板製造の重要技術である。汎用的な レベルで70-100μm、量産の先端で50μm、開発で 30µmレベルとなっている。

- ビルドアップ基板のビアは、底が下地のメタル層のブライン ドホール形状であるため、めっき液が底部に浸透し、メタル 層を成長させるには、薬液及び添加剤、循環の方法など の改良が必要となる。薬液の循環性を高めるために、逆 電解パルスめっきなどの電流波形の精密な制御を含めた 改良がおこなわれている。

- さらに、ビアは、30μmを下回り、20μmオーダの加工が求 められており、穴あけ技術の革新と同時に、埋込性の高 いめっきプロセス開発が必要となっている。

- 2) パッケージ基板材料

- パッケージ基板用銅張積層板:主たる用途及び技術動向

#### <主たる用途>

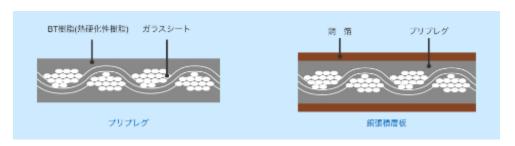

- 銅張積層板は、基板のコア材となる部材である。適度な剛性と 絶縁性を持つプリプレグを基板の芯材料とし、その両面を銅箔で挟んで 加熱・加圧したものが銅張積層板である。

- プリント基板のコア材であり、配線加工、積層のベースとなる材料であり、 基板の性能に大きく影響するべース材料である。

- プリプレグは、ガラスクロスシートにエポキシ等の絶縁性硬化樹脂を含侵 させ、半硬化状態まで熱処理・乾燥させた絶縁シートである。パッケージ 基板用では、誘電率・熱伝導度の調整のため、用途に応じてフィラーを 混ぜ、特性をコントロールする。

- 厚さは、15µmクラスから100µmクラスまである。

- なお、ここで使用する樹脂としては、エポキシ系樹脂が使われるが、 代表的な材料としては、BT樹脂「B成分(ビスマレイミド)とT成分 (トリアジン) 」とを主成分とした付加重合させた樹脂などがある。

#### 図表3-19 プリプレグと銅張積層板

- パッケージ基板用銅張積層板は、デバイスの高速・高周波対応から 低誘電損失の材料でありつつ、モバイル対応機器向けには、極限まで の薄さが求められる。サーバー等のハイエンドでは厚板が必要となっており、 デバイスの性能を決めるコア基材として技術革新が求められている。

- 低誘電損失材料

- 誘電正接Dfが2021年現在0.004クラスから、2022年に は、0.003クラスが求められ、2025年頃には、0.002クラス までの低減が求められている。

- モバイル向けの薄型化

- モバイル向けNANDを中心に、薄型化が進む。総厚で 80µmを切るために、16µmクラスのプリプレグが採用され ているが、さらに薄い12 - 13μmの採用が検討されている。

- ハイエンドパッケージ用のそり防止厚板

- ハイエンドなFC-BGA基板においては、基板の大型化に 対応し、銅張積層板のそり抑制のため、厚コアを採用す る動きがある。現在、サーバー向けには、0.8 - 1.2mm厚の ものが採用されており、2025年には、さらに厚い1.4-1.6mm 厚が必要となる見込み。

- 2) パッケージ基板材料

- ソルダーレジスト:主たる用途及び技術動向

#### <主な用途>

- ソルダーレジストとはプリント配線基板表面上の回路パターン を保護する絶縁膜となるインキである。

- ソルダーレジストの用途及び役割は以下の通り3点が主である。

- 1つ目は、不要部分へのはんだの付着防止であり、 プリント配線基板が部品に実装する際の電気的接続部分 へのはんだ等の不純物の付着を防ぎ、ショートの発生を防ぐ。

- 2つ目は、ほこり、熱、湿気などから回路パターンを保護である。

- 3つ目は、回路パターン間の電気絶縁性の維持であり、 電子機器のダウンサイジングに伴う回路パターン間の 絶縁性維持並びにショート防止に貢献する。

#### 図表3-20 ソルダーレジストのパターソニング後の基板表面画像

ソルダーレジスト:緑色部分

出所) 太陽ホールディングホームページ https://www.taiyo-hd.co.jp/jp/business/electronics/solderresist/

- 1980年代から現在に至るまで、フォトリソグラフィー法を用いた 光・熱硬化併用材料が開発され、それを用いた絶縁膜形成 技術が主流となっている。

- 1つ目のアルカリ現像型は、露光による未硬化部分を現像 液で現像する形成方法であり、微細形成が可能。

- 2つ目のUV硬化型は、スクリーン印刷法で印刷された パターンをUV光照射することで硬化させる。

- 3つ目の熱硬化型は、スクリーン印刷法で印刷された パターンを加熱することで硬化させる。

- ソルダーレジストへの要求特性は製造工程(塗布・パターニング)と 永久レジスト(保護膜)それぞれで異なってくる。 以下の通りの要求特性に対応するべく研究開発が行われる。

- 製造工程においては、長有効期限・印刷性・ 薄膜均一性・高感度・高解像性が求められる。

- 永久レジストとしては、耐薬品性・はんだ耐熱性・ 硬度密着性,電気絶縁性,耐湿性,耐衝撃性, 耐移動性が求められる。

- また、マイクロLED基板に対応した現像型高反射 ドライフィルムソルダーレジストなども開発されている。

- 3) 半導体後工程製造装置

- パッケージ基板用露光機:主たる用途及び技術動向

#### <主たる用途>

- パッケージ基板用露光機は、基板の配線層のパーターニングに使用され、 Via形成に使用するレーザー加工機と組み合わせて使用される。

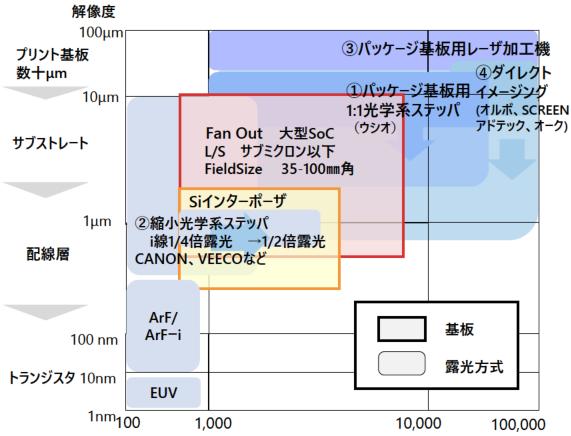

- 1:1のレンズ光学系投影露光機が主流であり、焦点深度が深く、大きな 基板を一括で露光することを可能にしている。一方で、基板の高集積・ 微細化が進展し、微細な配線を可能としながら、量産性の高い装置が 必要となり、縮小投影系の導入やダイレクトイメージングの利用も進む。

図表3-21 パッケージ基板用露光機の方式比較

|             | コンタクト        | 1:1光学<br>系投影露光         | 縮小レンズ光<br>学系投影露<br>光         | ダイレクト<br>イメージング                              |

|-------------|--------------|------------------------|------------------------------|----------------------------------------------|

| 解像力         | 1 -5μm       | 2-15μm                 | 0.2-2μm                      | 2-15μm                                       |

| 焦点深度        | 浅い           | 深い                     | 浅い                           | (深い)                                         |

| 露光面積        | 大<br>-600mm角 | 中-大<br>Ф60-200mm       | 小-中<br>Ф30-80mm              | 大                                            |

| マスク寿命       | 短い           | 半永久                    | 半永久                          | -                                            |

| 装置コスト       | 安い           | 中-高い                   | 非常に高い                        | 安い-中                                         |

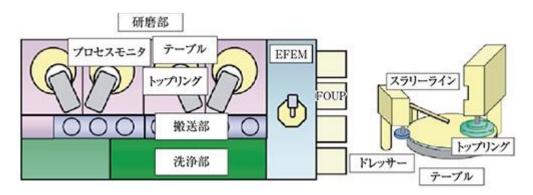

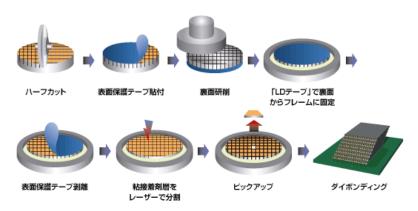

| 露光形態        | 一括露光         | 一括/分割露光                | 分割露光                         | 直接描画                                         |