# ポスト5 G情報通信システム基盤強化研究開発事業 研究開発計画

令和5年7月11日

経済産業省 商務情報政策局

## 目次

| 1.  | 目的・概要                 | . 2 |

|-----|-----------------------|-----|

| 2.  | 目標                    | . 2 |

| 3.  | 研究開発内容                | . 2 |

| ( ) | 1 )研究開発項目             | 2   |

| ( : | 2) 研究開発期間             | 24  |

| 4.  | 成果最大化に向けた仕組み          | 25  |

| ( ) | 1 ) ユーザーのニーズ把握        | 25  |

| ( : | 2)研究開発期間中の製品化         | 25  |

| (;  | 3) 民間企業等による市場展開を促す仕組み | 26  |

| ( 4 | 4) 民間企業等による負担         | 27  |

| 5.  | 実施者の採択                | 28  |

| ( ) | 1 ) 予算規模              | 28  |

| ( : | 2)採択方法                | 30  |

| 6.  | 実施体制等                 | 30  |

| ( ) | 1 )役割分担               | 30  |

| ( : | 2)研究開発の進捗把握・管理        | 31  |

| (;  | 3) 調査・広報              | 31  |

| 7.  | その他                   | 31  |

| ( : | 1)研究開発成果の取り扱い         | 31  |

| ( : | 2 )実施期間               | 32  |

| (:  | 3)中間評価・事後評価           | 32  |

| ( 4 | 4) 研究開発計画の見直し         | 32  |

| (別  | 紙)収益納付額の計算方法          | 33  |

### 1. 目的・概要

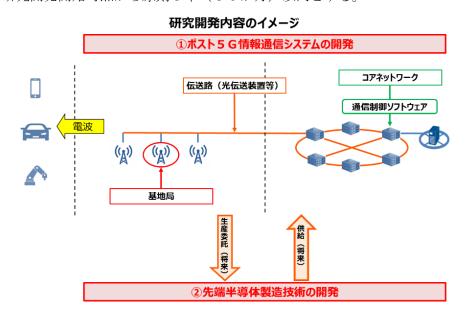

第4世代移動通信システム (4G)と比べてより高度な第5世代移動通信システム (5G) は、現在各国で商用サービスが始まりつつあるが、更に超低遅延や多数同時接続といった機能が強化された5G (以下、「ポスト5G」)は、今後、工場や自動車といった多様な産業用途への活用が見込まれており、我が国の競争力の核となり得る技術と期待される。

本事業では、ポスト5Gに対応した情報通信システム(以下、「ポスト5G情報通信システム」)の中核となる技術を開発することで、我が国のポスト5G情報通信システムの開発・製造基盤強化及びデジタル社会と脱炭素化の両立の実現を目指す。

具体的には、ポスト5G情報通信システムや当該システムで用いられる半導体等の関連技術を開発するとともに、ポスト5Gで必要となる先端的な半導体を将来的に国内で製造できる技術を確保するため、先端半導体の製造技術の開発に取り組む。

### 2. 目標

本研究開発事業全体の目標として、以下の通り、アウトプット目標及びアウトカム目標を定める。なお、研究開発内容に変更が生じた場合には、必要に応じて、本目標を見直す。

<アウトプット目標>

- 中間目標

- テーマごとに設定した最終目標の達成に向けた中間的マイルストーンを達成すること。

- 最終目標

ポスト5G情報通信システムを構成する各要素及び、ポスト5G情報通信システムに必要となる先端半導体の製造技術や材料技術等について、有識者の意見に基づき開発テーマごとに設定した目標を達成したテーマの割合(※):80%以上

※開発テーマごとに設定した目標を達成したテーマ数/当該時点までに研究開発を完了 したテーマ数(先導研究は除く)

<アウトカム目標>

本事業で開発した技術の実用化率(※):50%以上(各採択テーマ終了後概ね3年時点) ※開発した技術が実用化に至ったテーマ数/先導研究以外の採択テーマ数

### 3. 研究開発内容

### (1) 研究開発項目

以下①~③の項目について、研究開発を実施する。研究開発項目は、技術動向や市場動 向等を踏まえ、必要に応じて柔軟に追加・変更する。

また、研究開発項目毎もしくは個々の開発テーマ毎に開発目標を設定し、研究開発の進捗状況管理の一環として、当該目標の達成状況を国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)が評価する。必要な場合には、開発目標の見直しを行う。なお、【GX】は、対応する開発テーマの類型が「グリーントランスフォーメーション」(以下「GX」)であることを表す。

①ポスト5 G情報通信システムの開発(委託、助成)

情報通信ネットワーク全体やそれを構成する各要素(コアネットワーク、伝送路、基地局、モバイルエッジコンピューティング(MEC)、端末)、情報通信システムにおける情報処理を加速する計算基盤について、以下の技術開発に取り組む。なお、【システム技術開発】は、対応する開発テーマの類型が「システム技術開発」であることを表す。また、開発

テーマが助成事業である場合は(助成)で表し、(助成)表記がない開発テーマは委託事業であることを表す。

### (a) コアネットワーク

ポスト5Gのコアネットワークには、多様なサービスの要求に対応しつつ、膨大なトラフィックを可能な限り省電力かつ低コストで効率的に処理するため、仮想化や計算リソース管理等に関する高度な技術が求められる。また、低遅延や高信頼といった要求に対応するため、将来的には、巨大な単一のデータセンタで処理を行う形から、地理的に分散した複数の計算リソースを活用し、クラウドベースでコアネットワークを実現する形へと形態が大きく変化する可能性がある。このため、多様なサービスの要求に対応する上で適切なシステム構造とすることに留意しつつ、仮想化や計算リソース管理等に関する高度な技術を備えるとともに、クラウドベースでも動作が可能なコアネットワークのソフトウェア技術等を開発する。

具体的な開発テーマは、以下の通りとする。

(a1) クラウド型コアの高度化技術の開発【システム技術開発】

#### <開発対象>

• 3GPPの仕様(リリース15~17)に準拠し、クラウド基盤上で動作する5Gコアを実現するソフトウェア技術

#### <開発目標>

- U-planeにおける単位計算リソース当たりのユーザデータの処理性能(※): 研究開発開始時点で普及している製品(クラウド基盤上での動作を前提としていないもの)と比較して同等以上

- ※例えば、「Gbps/CPUコア」で表される処理性能。

- C-planeにおける単位計算リソース当たりの制御信号の処理性能(※):研究 開発開始時点で普及している製品(クラウド基盤上での動作を前提としていないもの) と比較して同等以上

- ※例えば、「TPS/CPUコア」で表される処理性能。TPSは、Transaction Per Secondを表す。

### (a2) クラウド型ネットワーク統合管理・自動最適化技術の開発【システム技術開発】 <開発対象>

- 情報通信ネットワークの機能がクラウド基盤を利用して提供されることを前提として、OSS (Operation Support System) 及びMANO (Management and Network Orchestration) に、アプリケーションの要求に応じたネットワークスライスを無線アクセスネットワーク (RAN: Radio Access Network) からコアまでエンドツーエンドで生成・管理する機能や、情報通信ネットワークから収集した情報を基にリアルタイムで品質の監視・劣化予測等を行う機能及び当該予測等に基づきリアルタイムで計算リソースの最適配置を行う機能等を搭載するためのソフトウェア技術

- ※OSSは、情報通信事業者等による情報通信ネットワークの運用を支援するシステムを表す。

- ※MANOは、NFV(Network Functions Virtualiz ation)において、NFVI(NFV Infrastructure)、やV NF(Virtual Network Function)、OSS等に指示を出しながら、ネットワークサービスやそれに必要な計算リソースの統合的な管理・制御を担うシステムを表す。

- ※NFVは、従来は専用装置により提供されていた情報通信ネットワークの機能を汎用サーバによる仮想化基盤上でソフトウェアとして実現する方式を表す。NFVIは、物理的な計算リソースを仮想化された計算リソースとして扱うための仮想化基盤を表す。VNFは、NFVI上で動作する仮想化された情報通信ネットワークの

機能を表す。

#### <開発目標>

- 5 G情報通信ネットワークの構築及び運用に関する自動化率(※):研究開発開始時 点の自動化率と比較して30%以上向上

- ※構築及び運用に必要な全作業量(例えば、「工数(人日)」で表される作業量)のうち、自動化可能な作業量の割合を表す。

### (b) 伝送路

ポスト5Gの伝送路には、データ伝送の遅延を短く保ちつつ、膨大なトラフィックの増加に対応するため、光伝送装置の大幅な性能向上が求められる。また、機能分割された各基地局機能間の信号やMECで処理されたデータなど、容量や経路が異なる光信号を柔軟に制御する必要がある。加えて、ビル壁面や街路灯へのアンテナ設置やビル間伝送などにおいて光ファイバ伝送より効率的な無線伝送や、遠隔医療等の産業用途サービスを島しよ部等の条件不利地域でも展開するために効率的に伝送路を構築する技術が必要となる。

このため、伝送路上の光信号を高速で電気信号に変換(及びその逆変換)することが可能な光伝送装置、光伝送装置内においてデジタル信号の高速処理を担うDSP(デジタル・シグナル・プロセッサ)、膨大な情報を高速かつ省電力で書込み・読出し可能な不揮発性メモリ等に関する技術、MFH(MobileFrontHaul)や基地局~<math>MECサーバー間等比較的短距離のイーサネット伝送リンクにおいて利用される超高速光デバイス、大容量固定無線伝送装置、柔軟に経路制御可能な光スイッチ技術、島しょ部等に効率的にMBH(MobileBackHaul)回線を整備する技術を開発する。

具体的な開発テーマは、以下の通りとする。

### (b1) 光伝送システムの高速化技術の開発【システム技術開発】

#### <開発対象>

- 1波長当たり最大伝送速度1Tbps以上の光伝送装置を実現する技術(当該装置を 実現するためのデバイス・ソフトウェア等を含む)

- 伝送路運用(伝送品質、伝送リソース、消費電力 等)の自動最適化技術

### <開発目標>

光伝送装置における1ポート(1Tbps以上)の消費電力性能:120mW/Gbps以下

#### (b2) 光伝送用DSPの高速化技術の開発

#### <開発対象>

• デジタルコヒーレント光伝送で用いる最大伝送速度1Tbps以上のDSPを実現する技術

### <開発目標>

DSPの消費電力性能(W/bps):研究開発開始時点で普及している製品と比較して1/5以下

#### (b3) 微細化の進展に対応した高速不揮発性メモリ技術の開発

### <開発対象>

• 5 n m以降のロジック半導体製造プロセスに対応した不揮発性メモリアレイを実現する技術(当該メモリアレイを実現するための素子を含む)

※当該メモリアレイを用いることにより実現可能な新たな光伝送技術についても、 必要に応じて、開発対象に含めることが可能。

#### <開発目標>

- メモリアレイの1ビット当たり書き込み時間:10ns以下

- メモリアレイの1ビット当たり書き込みエネルギー:1fJ以下

- メモリアレイの書き換え可能回数:10<sup>15</sup>回以上

### (b4) 固定無線伝送システム大容量化技術の開発【システム技術開発】

### <開発対象>

• 最大伝送速度25Gbps以上のミリ波帯固定無線伝送装置を実現する技術(当該装置を実現するためのデバイス・ソフトウェア等を含む)

#### <開発目標>

- 伝送速度: 25Gbps以上

- 送信パワー: 10dBm以上(25Gbps伝送時に達成すること)

### (b5) バス型伝送高度化技術の開発【システム技術開発】

#### <開発対象>

- ケーブル分岐機能を備えたバス型伝送トポロジにより島しょ部等において効率的に伝送路(基地局~モバイルコア区間のMBH)を構築する技術

- 給電装置をブランチ部に設置しないバス型伝送システムにおいて、ブランチケーブル 長を延伸する技術

- トランクからブランチへの給電電力の高出力化を実現する技術 ※トランクとはバス型伝送路において共有区間となる幹線部分を指す。 ※ブランチとはトランクからケーブル分岐機能により枝分かれする支線部分を指す。<開発目標>

- トランクからブランチへの給電電力:400W以上

- ブランチ区間長:200km以上

- 光中継装置の消費電力:研究開発開始時の普及品に対し20%減

### (b6) 超高速光リンク技術の開発

#### <開発対象>

• 超高速イーサネット用光デバイスを実現する技術

#### <開発目標>

- 変調方式:強度変調

- 伝送速度: 200Gbps/波長以上

- ON/OFF比:5dB以上

- 伝送距離: 1 k m以上

### (b7) 光スイッチ高度化技術の開発

#### <開発対象>

• フレックスグリッド用光スイッチの光学特性向上、入出力ポート数拡大を実現する技術

### <開発目標>

- 挿入損失:8dB以下

- 周波数分解能: 6. 25GHz以下

- スイッチ規模:  $1 \times N$ 型で $1 \times 20$ が4並列以上、 $M \times N$ 型で $8 \times 16$ 以上 ※ $M \times N$ 型はMが入力ポート数、Nが出力ポート数を表す。 $1 \times N$ 型、 $M \times N$ 型の目標値をそれぞれ実現すること。

- 消費電力:研究開発開始時点の普及品に対しポート当たり50%以上削減

### (c) 基地局

ポスト5Gの基地局には、広帯域である高周波数帯の無線リソースを有効利用するため、多数の端末との同時接続を実現する高度なビーム制御が求められるとともに、利用周波数帯が上がるにつれアンテナ間隔が狭まるため放熱効率の向上が求められる。また、基地局内で膨大な信号を低遅延で処理するため、基地局内部においても高い伝送速度を確保することが求められる。加えて、遠方まで届きにくい高周波数帯の電波の利用により基地局の設置数が増加するため、基地局の無線ユニットやそこで用いられる高周波デバイス等の高出力化・小型化による省電力化、またソフトウェア化の進展によるコスト低減等が求めら

れる。

このため、高度なビーム制御機能を備え、省電力性能等に優れた基地局、基地局のソフトウェア化、基地局に搭載される高出力・小型の高周波デバイスや基地局内部の光配線化等に関する技術、高効率アンプー体型アレイアンテナ実装技術を開発する。

また、近年、基地局を構成する装置間の接続インターフェイスをオープンにすることにより、複数のベンダーの装置で基地局を構成し、調達の多様化を実現するための取組(O-RAN)が進められており、基地局を構成する一部装置やインテグレーション技術で競争力を有する日本のベンダー・オペレーターが世界シェアを獲得する千載一遇の機会であるが、実際に多様なベンダーの多様な装置間での相互接続性を確保する上では、検証に必要なプロセスやツールが整備されていない等、技術的なハードルが存在している。このため、装置間の相互接続性の評価・検証等を行うための技術を開発する。加えて、O-RANの国際的な普及拡大にあたっては、各国・オペレーター毎の周波数や利用する通信方式、現地オペレーターが保有する伝送路やコアネットワークとの接続等を考慮した莫大な数のインテグレーション・品質保証が必要となる。そこで、O-RANインテグレーションを抜本的に簡易化する技術を開発する。また、基地局をオペレーター間で共有することによって抜本的な効率化を図る基地局シェアリングが一部の国では必須となっているため、O-RAN基地局のシェアリングを可能とする技術を開発する。

さらに、ポスト5Gで実現が期待されるスマート工場や自動運転等の産業用途サービスでは、高い信頼性や用途に応じた通信品質の保証が必要になる。そこで、RANの安定動作やアプリケーション要求に応じた品質制御に資する技術を開発する。

具体的な開発テーマは、以下の通りとする。

### (c1) 仮想化基地局制御部の高性能化技術の開発【システム技術開発】 <開発対象>

- 3GPPの仕様(リリース15~17)に準拠し、ネットワークスライシングに対応 した5G基地局制御部を汎用ハードウェア上で実現するソフトウェア技術

- ※5G基地局制御部は、「CU (Central Unit)及びDU (Distributed Unit)」を表す。

### <開発目標>

- 5 G基地局制御部に関する単位伝送速度当たりのCAPEX (設備投資コスト)及び OPEX (運用コスト) (円/bps):研究開発開始時点で普及している製品 (専用 ハードウェアで機能を実現するもの)と比較して30%以上削減

- 多数同時接続もしくは超低遅延の実現に寄与する5G基地局制御部の中核技術に関する性能:研究開発開始時点で普及している製品(専用ハードウェアで機能を実現するもの)と比較して3倍以上(※)

- ※例えば、「5G基地局への端末の同時接続数:研究開発開始時点で普及している製品 (専用ハードウェアで機能を実現するもの)と比較して3倍」といった形で設定。

### (c2) 基地局無線部の高性能化技術の開発【システム技術開発】

#### <開発対象>

- 3 G P P の仕様(リリース15~17)に準拠し、ビームフォーミング機能を備えた 5 G 基地局無線部を実現する技術(当該装置を実現するためのデバイス・ソフトウェ ア等を含む)

- ※5G基地局無線部は、RANの機能を低いレイヤ(Lower Layer)で分割する場合には「RU(Radio Unit)」、高いレイヤ(Higher Layer)で分割する場合には「RU及びDU」を表す。

#### <開発目標>

- 5 G基地局無線部の単位システム容量当たり装置サイズ (m³/(bps/Hz/km²))及び消費電力 (W/(bps/Hz/km²)):

- (A) 研究開発開始時点で普及している製品と比較して装置サイズ1/2以下かつ消費電力同等以下

#### 又は

- (B)研究開発開始時点で普及している製品と比較して装置サイズ同等以下かつ消費 電力70%以下

- $%システム容量は、単位面積当たり・単位周波数帯域当たりの伝送速度(<math>bps/Hz/km^2$ )を表す。

- 多数同時接続もしくは超低遅延の実現に寄与する5G基地局無線部の中核技術に関する性能:研究開発終了時点で想定される世界最高水準の性能(※) ※例えば、「5G基地局への端末の同時接続数:X台/km²」といった形で設定。

- (c3) 基地局装置間の相互接続性等の評価・検証技術の開発

#### <開発対象>

- O-RANのインターフェイス仕様に準拠した装置について、異なるベンダーの装置間の相互接続性及び当該接続が情報通信ネットワーク全体に与える影響を評価・検証するための技術(評価・検証等に必要なプロセス、ツール、ソフトウェア等を含む)

- 当該技術を開発するための評価・検証環境の設置

- ※複数のベンダーの装置で基地局を構成する取組を、国際的に普及させる観点から、 当該評価・検証環境は、原則として海外に設置し、海外のユーザーのニーズを取り 込みながら開発を実施する。

#### <開発目標>

- 海外における評価・検証環境の設置件数:1件以上

- 開発した技術を用いて相互接続性等の評価・検証を行った装置の組み合せ: 10 通り以上

- (c4) 高周波デバイスの高出力・小型化技術の開発

#### <開発対象>

- 高出力の基地局向け高周波GaNデバイスの製造に用いる基板の結晶成長技術

- 当該技術を用いて製造する基地局向け高周波GaNデバイス(Sub-6GHz帯向けデバイス及びミリ波帯(28GHz以上)向けデバイス)を実現する技術 ※当該デバイスを利用した増幅器や、基地局への当該増幅器の搭載を効率化する上で

- \*当該アバイスを利用した増幅器や、基地局への当該増幅器の搭載を効率化する上で有効なモジュール化技術等についても、必要に応じて、開発対象に含めることが可能。

### <開発目標>

- Sub-6GHz帯向け高周波GaNデバイスの出力電力密度:25W/mm以上

- ミリ波帯向け高周波G a Nデバイスの出力電力密度: 12W/mm以上

- ■継続研究開発(助成)

### <開発対象>

- c4 で開発した結晶及び素子の信頼性向上に向けた、結晶の高抵抗化技術及び絶縁膜物性に立脚した素子作製技術

- c4 で開発したG a Nデバイスの広帯域増幅器を実現する技術

- 高周波に対応した集積回路の積層化等に伴うピーク温度低減のための放熱技術 <開発目標>

• Vp変動量(Vp:閾値電圧):20%以内

帯域幅(Sub-6GHz) : 400MHz以上

熱抵抗値 : 5.3℃/W以下

#### (c5) 高温動作可能な光接続技術の開発

#### <開発対象>

- 基地局(RU)のアレイアンテナシステム内に搭載可能なシリコンフォトニクス光トランシーバを実現する技術

- 当該トランシーバをRUのアレイアンテナシステム内に搭載し、アレイアンテナとそ

- の制御回路等を光配線により接続するための実装技術(実装に必要なモジュール化を 含む)

- ※アレイアンテナシステムとは、アンテナアレイとその制御回路等から成るシステムを表す。

#### <開発目標>

- 光トランシーバの消費電力性能: 4 mW/Gbps以下

- 光トランシーバの最大伝送速度:1Tbps/cm²以上

- 光トランシーバが正常動作可能な環境温度:100℃以上

### (c6) 高周波帯アンプー体型アレイアンテナ実装技術の開発

### <開発対象>

- ミリ波帯 (40GHz以上)で動作しビーム制御が可能なアンプー体型アレイアンテナモジュールにおいて、高い放熱効率を実現する実装技術の開発

- スモールセルやインドア用途を想定した高効率なアンプを実現する技術の開発 <開発目標>

- アレイアンテナ素子数: 4 x 4以上

- 熱源(アンプ)からヒートシンクまでの熱抵抗:1.0K/W以下

- 出力パワー: 5 mw/アンテナ素子以上(40~50GHzの場合)

※出力パワーは、他の周波数帯の場合はスモールセル・インドア用途で必要と認められる値を設定するものとする

### (c7) RAN制御高度化技術の開発【システム技術開発】

### <開発対象>

• O—RAN標準のRIC(RAN Intelligent Controller) により産業用途アプリケーションに応じたRAN制御を実現する技術

#### <開発目標>

- Non-RT RICのrApp機能もしくはNear-RT RICのxApp機能のいずれか、あるいは両方を用いた、産業アプリケーションに応じたRAN制御の有効性検証:合計2件以上

- ※有効性検証として、例えばアプリケーションに応じた制御モデル構築と動作検証、アプリケーションに応じたRAN制御とQoE(Quality of Experience)の関係明確化等、産業用途のRIC活用・製品競争力向上に資すると認められるものを実施する。

- ※有効性検証において少なくとも1件は対象とするアプリケーションで必要な実機を 用いたものとする。

- •開発した r A p p または x A p p またはその両方が動作する R I C と、O R A N のインターフェイス仕様に準拠した基地局装置との相互接続性の評価/検証:異なるベンダーの基地局装置を用いて 2 通り以上

- ※評価/検証のうち1通りは自社開発の基地局装置を含めることが可能。また、自社開発品ではない基地局装置を用いた検証が困難な場合は、O-RAN準拠製品を模擬できることが確認されたシミュレータや試験装置等を用いてもよい。

### (c8) O-RANインテグレーション基盤技術の開発(助成)

### <開発対象>

- 様々な周波数帯、無線・有線区間の通信方式、ハードウェアやソフトウェア等の莫大な組み合わせに対し代表的なパターンとして多くの国・オペレーターで共通利用可能なO—RAN基地局インテグレーションパターンのモデル化技術、および各モデルで共通に利用可能なソフトウェアの開発

- O-RAN基地局を構成する個々のコンポーネント、および端末~O-RAN基地局 ~コアネットワーク~検証サーバー間のエンドツーエンドでの接続検証、解析、改修 や品質保証等に関わる検証作業を自動化する技術

### <開発目標>

- PoCモデル作成数:3以上

- ※グローバル展開において十分な数のオペレーターに適用可能と認められるモデルを 作成するものとする。

- 作成したモデル間でのソフトウェア共用割合: 70%以上

- ※ソフトウェアスタックの共通化やソースコードの流用度等、ソフトウェアの共用としてインテグレーションの効率化に資すると認められるものを設定するものとする。

- 検証業務の自動化率:50%以上

- ※作成したPoCモデルおよび共通ソフトウェアを用いるものとする。また、自動化技術の検証に必要な設備等の構築を含んでもよい。

- 作成したPoCモデルの実環境での検証: 3件以上

- ※都市部・ルーラルといった地域特性や、伝送路やコアネットワーク等のオペレーター設備との接続を考慮した実環境でのデータ取得、および、O—RANを国際的に普及させる観点から、原則として適切な環境を有する海外オペレーターと協力して検証を行うこととし、候補となる海外オペレーターを提案に含むものとする。

### (c9) O-RAN基地局シェアリング技術の開発(助成)

#### <開発対象>

- O-RAN基地局無線部を複数のオペレーターで共有(シェアリング)する構成において、オペレーターごとに必要な処理能力や周波数等を割り当てる技術

- シェアリングしたO-RAN基地局を保守・監視する技術

### <開発目標>

- O-RAN基地局無線部の処理能力や周波数等をオペレーターごとに柔軟に割り当て 可能とする機能を具備すること

- ※例えば、オペレーターが利用する周波数と周波数帯域幅の組み合わせを、複数オペレーター分収容可能とする機能等、基地局無線部のシェアリングで必要と考えられる機能を開発目標として設定。

- 2以上のベンダーの基地局無線部、および2以上のベンダーの基地局制御部を用いたマルチベンダー接続により構成したO-RAN基地局において、2以上のオペレーターを収容可能とすること

- 基地局シェアリング時に保守・監視可能なオペレーター数: 2以上 ※保守・監視項目は其地昌シュアリングの運用にあたって必要し考えられ

- ※保守・監視項目は基地局シェアリングの運用にあたって必要と考えられるものを設 定するものとする

- 実環境での検証:2件以上

- ※都市部・ルーラルといった地域特性や、伝送路やコアネットワーク等のオペレーター設備との接続を考慮した実環境でのデータ取得、および、O—RANを国際的に普及させる観点から、原則として適切な環境を有する海外オペレーターと協力して検証を行うこととし、候補となる海外オペレーターを提案に含むものとする。

- ※実環境での検証のそれぞれについて、1以上は実在のオペレーターを収容するものとし、他の1以上のオペレーター相当として測定器等を用いて複数オペレーターでの基地局シェアリングを模擬してもよいものとする。

### (d) MEC

ポスト5Gネットワークの低遅延性・多数同時接続とIoT、AI等の活用により多様な産業活動や国民生活のスマート化が期待されている。また、エッジの端末やセンサーで生み出される大量なデータの蓄積や解析の高度化、AI学習の高性能化の進展が予想されている。しかし、全てのデータをデータセンタ等のクラウドサーバーに送信し、解析、AI学習等をした場合、情報伝送に大量エネルギーとコストがかかり、ネットワーク負荷も多大になるとともに、ポスト5Gの特徴である低遅延性の実現が困難となる。このため、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理を可能とするMEC

サーバーの普及が求められる。また、低遅延ネットワークを実現するためには、MEC、ネットワーク構成機器、MECと情報通信するエッジデバイス自体の高性能化も求められる。これらMECサーバーやネットワーク機器、エッジデバイスのコンピューティング性能を決定づける重要な役割を担っているのが、大規模・高性能・低消費電力な先端ロジック半導体や、広帯域化で低遅延な大容量メモリモジュールである。

そこで、MECを用いた低遅延処理の実現に向けて、最先端のプロセスノードを適用した大規模先端ロジック半導体の設計技術を開発するとともに、大容量・広帯域なメモリシステムを開発する。

### (d1) MEC向け大規模先端ロジックチップ設計技術の開発

### <開発対象>

• 先端ロジック世代 (3nm ノード以降\*\*) のAI処理可能なSoC設計技術、スケーラブルなマルチチップシステム (2.5次元・3次元実装、チップレットパッケージ等のSiP(System in package)モジュール) を実現するための設計技術、システムアーキテクチャ技術、テスティング手法を含むその他の関連する設計環境の開発。

※IEEE の IRDS (International Roadmap for Devices and Systems™) 2020 中の「Logic industry "Node Range" labeling (nm)」における「3」以降を意味する。

#### <開発目標>

- チップレット\*1間インタフェース性能 (FOM\*2): 3(Tbps/mm)/(pj/bit)以上

- SiP モジュール間の帯域: 400Gbps 以上

- AI 処理性能 (チップレット単体): 20TOPS/W 以上

- AI 処理性能 (SiP モジュール): 300TOPS 以上

- ※1 SiP内の単体チップを意味する。

- ※2 Figure of Merit の略。1ビットのデータ伝送に必要なエネルギー(pJ/bit)で 規格化した1mm当たりのデータ伝送量(Tbps/mm)。FOM値が大きいほど高効率なシステムを意味する。

#### (d2) MECサーバー向け広帯域・大容量メモリモジュール設計技術の開発

### <開発対象>

• ビッグデータ処理向けの低消費電力かつ広帯域、大容量なメモリモジュールの設計 技術

### <開発目標>

- メモリモジュールの消費電力:40W以下

- メモリモジュールの容量:2TB以上

- メモリモジュールの帯域:64GB/s以上

### (e) 端末

ポスト5G情報通信システムにおいては、スマート工場や自動運転など用途に応じた多種多様な端末開発が行われることが想定されるため、さまざまな端末に汎用的に利用可能な端末通信チップ・モジュール等を開発する。

また、ポスト5Gネットワークの超低遅延性・多数同時接続と IoT、AI 等の活用により、生成・処理されるデータ量が爆発的に増大することが予測されており、これまでのデータ集約・処理型のクラウドサーバーに加えて、端末でデータ処理を行うエッジコンピューティング技術が必要となる。一方、端末では利用可能な電力量が制限されるため、低消費電力での AI 処理が求められる。そこで、端末での効率的なデータ処理を実現するコンピューティング技術の研究開発を行う。

#### (e1) 端末通信機能構成技術の開発

### <開発対象>

• 3 G P P の仕様(リリース 1 5 ~ 1 7)に準拠し、超低遅延通信を実現する通信機能 部を構成する技術

- 通信設定を柔軟に変更し様々な用途/端末に対応可能な通信制御技術 <開発目標>

- 超低遅延の実現に寄与する5G端末通信機能部の中核技術に関する性能:研究開発終 了時点で想定される世界最高水準の性能

- ※例えば、「端末内処理遅延: Xmsec以下」といった形で設定。

- 通信設定をユーザーが変更できる機能を具備すること

- ※変更可能な通信設定とは、例えば大容量通信モードと超低遅延通信モードの切り替え、上下の帯域割り当て比率等、産業用途で必要と考えられるものを開発目標として設定。

- 開発した端末通信機能を備えた通信チップ・モジュールと、基地局装置との相互接続性の評価/検証:異なるベンダーの基地局装置を用いて2通り以上

- ※相互接続性の評価/検証は少なくとも1通りはローカル5G基地局を用いての実施を必須とする。評価/検証のうち1通りは、接続性評価/検証に必要な機能を備えたシミュレータや試験装置等を用いてもよい。

- (e2) 端末向け低消費電力コンピューティング技術の開発

#### <開発対象>

- ・端末での AI 処理を想定した低消費電力コンピューティング技術※1※2

- ※1 半導体関連技術を利用した低消費電力化技術であること。また、AI チップ単独の研究開発による低消費電力化の技術は対象外とする。

- ※2 ロジック及びメモリ等を搭載したモジュールを試作し、動作実証をすること。 <開発目標>

- 端末での AI 処理<sup>※1</sup> における、従来技術<sup>※2</sup> と比較した消費電力の削減<sup>※3</sup> 割合:50%以上

- ※1 実施者が提案時に端末での AI 処理のユースケースを設定し、複数のモデルで検証すること。

- ※2 研究開発開始時点で普及している技術。

- ※3 半導体の微細化等による削減は除く。

- (f) 超分散コンピューティング

ポスト5Gの特徴である低遅延性の実現のためには、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理が求められている。他方、現状ではネットワークを介したデータ処理の多くは、特定の場所に集中した巨大なデータセンタで行われており、現在の集中型を前提としたデータ処理技術では低遅延性の実現が困難となる。低遅延ネットワークを実現するためには、データセンタやMEC、ネットワーク構成機器、エッジデバイスなど、地理的に分散した計算資源を最適に活用してデータ処理を行うことが求められる。また、ポスト5Gによる広帯域・多数同時接続の結果、より多数のステークホルダーが大量のデータを保有することが想定される中、こうしたデータをステークホルダー間で円滑・安全に利活用する仕組みや技術も求められている。

このため、地理的に分散したデータセンタからコアネットワーク、伝送路、基地局、MECに至るまで、全体を仮想的な一つのシステム(以下、「超分散コンピューティング環境」という。)と見なして、地理的条件や動的な処理負荷も踏まえて処理需要をデータ処理拠点に割り振り、低遅延性などの制約を満たしつつ最適に実行するアプリケーション実行技術や、複数の計算資源やステークホルダー間での円滑で安全なデータ利活用を実現するデータ利活用技術、これらを統合しシステム化するシステム統合技術を開発する。加えて、超分散コンピューティング環境において、特にプライバシーの保護や機密性を要するデータ処理を可能にするデータ流通技術を開発する。

(f1) 超分散コンピューティング技術の開発【システム技術開発】 <開発対象>

- 超分散コンピューティング環境におけるアプリケーション実行技術

- ※地理的に分散した計算資源の状態把握・制御を担う資源管理技術、応答時間や消費 電力等の制約に応じて最適に複数アプリを配置・実行可能にする最適化実行技術、 ユーザーの要求やイベントの発生を起点に一定の時間内に処理結果を応答する低遅 延実行を可能にする低遅延実行技術、アプリの開発・導入を簡便化するフレームワ ーク技術など。

- 超分散コンピューティング環境におけるデータ利活用技術

- ※地理的に分散した計算資源で取得・管理される膨大なデータを利活用するためのデータ基盤技術およびデータ処理効率化技術、動的なアクセス制御・データ漏洩等に対する包括的な防御・データ取得から利用までのトレーサビリティを実現するセキュリティ基盤技術など。

- 超分散コンピューティング環境を実現するシステム統合技術 ※アプリケーション実行技術およびデータ利活用技術を統合したシステム化技術、サービスモデル設計・検証など。

#### <開発目標>

- ポスト5Gで実現が期待される産業用途の実応用サービスを用いた評価/検証:2件以上

- ※うち1件はポスト5Gの特徴である低遅延性を活用した実応用サービスでの実施、 1件は超分散コンピューティング環境の特徴である地理的に分散した計算資源を活 用した実応用サービスでの実施、を必須とする。

- 研究開発終了時点で想定される規模の超分散コンピューティング環境において、開発 した超分散コンピューティング技術の有効性を検証

- ※例えば、管理者が異なる国内10箇所以上のデータセンタと5Gネットワークに接続されたN台以上の5G端末等から構成される規模の環境において、アプリに応じた遅延制約を満たす実行やデータ処理性能等を検証。ただし端末数Nは、世界のIoT端末数の研究開発終了時点での予測値等から定めることとし、有効性検証にあたってはシミュレーションなどによる外挿を認める。

実施に際しては、事業成果の最大化のため、プラットフォーム事業者を実施体制に加えるともに、本事業と並行して開発した成果の積極的な社会実装を推進できる体制をとることとする。また、データセンタ事業者、通信事業者、学術機関等との共同開発やその他の連携を推進する等、可能な範囲でオープンイノベーションを推進するとともに、必要に応じ、本事業で構築するパイロットプラットフォーム等の活用による評価・検証、ユーザー企業・機関との連携、国際連携の推進、オープンアーキテクチャ化・API等の標準化の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。また、必要に応じて随時、研究開発項目①(f2)とも連携を行う。

### (f2) 高機密データ流通技術の開発【システム技術開発】

#### <開発対象>

- 超分散コンピューティング環境におけるデータおよびアルゴリズムの秘匿化流通・実 行技術

- ※データおよびアルゴリズムの提供者、利用者、プラットフォーム事業者間でデータ やアルゴリズムの機密性を担保したまま処理を行う秘匿化実行技術など。

- 超分散コンピューティング環境におけるデータおよびアルゴリズムの可搬性技術 ※計算資源の物理的な配置や秘匿化処理の有無等によらず、透過的にアルゴリズムの 実行やデータアクセスを可能にする可搬実行技術など。

### <開発目標>

- ポスト5Gで実現が期待されるカーボントレースや電力データ流通・制御など横串の 社会課題解決を見据えた実応用サービスを用いた評価/検証:2件以上

- ※うち1件は地理的に分散した計算資源を活用したサービスでの実施、を必須とする。

- 超分散コンピューティング環境における実応用サービスに即して、開発した高機密デ

### ータ流通技術の有効性を検証

※例えば、実応用サービスに即して「秒間 N 万レコード以上の秘匿化データ処理性能 を、通常のデータ処理と同等程度の計算資源で達成」といった形で設定。

実施に際しては、事業成果の最大化のため、プラットフォーム事業者を実施体制に加えるともに、本事業と並行して開発した成果の積極的な社会実装を推進できる体制をとることとする。また、可能な範囲でオープンノベーション等の推進を行うとともに、必要に応じて随時、研究開発項目① (f1) とも連携を行う。

### (g) 計算可能領域拡大のための計算基盤技術開発(委託)

デジタル化の進展により大量のデータ処理への需要が高まっており、自動運転、スマートファクトリ、物流などポスト5G時代で導入が進むアプリケーションによってさらなる計算需要の拡大が予想される。こうした計算需要に応えるためには、従来のクラウドサーバー等では処理能力が不十分なため、ポスト5G情報通信システムの一部として計算可能領域を拡大する計算基盤が必要であり、その計算基盤はスーパーコンピュータやAIコンピュータなど、いわゆる古典コンピュータだけでなく、量子コンピュータなどの様々な計算質源をネットワークでつなぎ、情報処理を進化させたものになると考えられる。このような計算可能領域拡大のための計算基盤技術の確立には、極めて先端的な技術開発を要し、外国政府による貿易管理規制の域外適用等の外部要因によって市場の有無が大きく左右され得るため、委託事業として実施する必要がある。

### (g1) 量子・スパコンの統合利用技術の開発

量子コンピュータは、従来のコンピュータとは全く異なる原理で動作し、特定の領域の問題に対しては情報処理を劇的に高速化できることから、従来のコンピュータでは事実上計算不可能な問題を処理できる特徴をもつ。このような領域の問題として、創薬・素材開発等における量子化学シミュレーション、金融・交通分野等における組み合わせ最適化、暗号解読等における素因数分解等の計算が挙げられており、ポスト5G情報通信システムを活用したユースケースとしては、スマートグリッドやサプライチェーン等の最適化などが期待される。こうした量子コンピュータの応用可能性については、様々な期待が寄せられつつも、日本では依然として未来の技術と見なされ十分な理解が進んでいない。結果として、企業等による投資や開発が停滞しており、特にゲート式量子コンピュータの開発では日本企業の国際競争力は見劣りする状況にある。

現在稼働中、あるいは提案されている量子コンピュータの多くは、周囲の熱や電磁気などによるノイズに弱く単体では実用的な計算が困難であり、そのため、古典コンピュータによる適切な制御、ノイズによるエラーの修正・補正、回路分割・最適化を行い、その上で量子と古典で得意な計算を分担しながら全体として計算能力を高める、いわゆる量子・古典ハイブリッド計算が注目されている。そうした中、量子コンピュータの性能向上に伴い、ハイブリッド計算に要求される古典コンピュータ側の処理も急速に高度化しており、従来の30量子ビット程度までは通常のサーバーでも処理できていたものが、最先端の100量子ビット級、さらにその先の大規模システムではスパコン超級の処理能力が不可欠になると予想される。このため、今後の量子コンピュータの早期の実用化による計算可能領域の拡大には、量子・スパコンの有機的な統合利用技術の確立が必須である。

本開発テーマでは、最先端の量子コンピュータに関わる技術や知見を活用しつつ、量子・スパコン連携ソフトウェア技術の開発に取り組む。具体的には、量子・スパコン連携のためのシステムソフトウェア、最適化ソフトウェア等を開発するとともに、これらを統合したパイロットプラットフォームを開発し、量子・古典ハイブリッド計算の有効性を実証する。なお、本テーマで開発する技術は、スパコン技術において世界最先端の一角を担う我が国において、特に量子コンピュータを支えるチョークポイント技術として育成すべきものでもあり重要性が高い。

#### <開発対象>

- 量子・スパコン連携システムソフトウェア、スパコン向け量子プログラム最適化ソフトウェア、その他関連するソフトウェアに関わる技術

- パイロットプラットフォームの構築ならびに運用に関わる技術

- ※パイロットプラットフォーム構築にあたっての注意事項を参照。

- 実証に必要となる、量子ソフトウェア (アルゴリズム、アプリケーション)、性能指標 に関わる技術

- 開発した上記技術、アプリケーション等をクラウドサービスとして提供するための技術

### ※パイロットプラットフォーム構築にあたっての注意事項:

- 現に保有するスーパーコンピュータ等に加え、技術開発に必要な機器(ゲート式量子 コンピュータ実機、量子回路シミュレーション加速環境など)を利用すること。

- 量子コンピュータ実機は、量子ビット数 100 以上など、今日のスパコンではエミュレートが困難な性能・容量仕様を満たす、最先端機器とすること。複数基利用する場合は異なる特性のものとすること。

- 利用する機器は、量子・古典ハイブリッド計算の可能性を最大限追求できるように、 現に保有するスパコン等と同一建屋内に設置され、高速・低遅延なネットワークで相 互に接続されること。

- 産官学の利用者が当該プラットフォームを利用するための枠組みを整備すること。

#### <開発目標>

● 本開発テーマで開発した量子・スパコン連携パイロットプラットフォームによる量子・古典ハイブリッド計算が有効になるアプリケーションドメインを明らかにし、計算可能領域の拡大および有効性を実証すること。: 1 件以上 ※例えば、「実応用において、開発したプラットフォームが、スパコン単体より処理速度や消費電力の点で優位であることを示す」といった形で設定し、その際、提案者にて具体的な指標、目標値を提案時に設定すること。

### <応募条件>

- 5年以上のスパコン運用の経験を有し、量子・スパコン連携プラットフォームの一部として利用可能なスパコンを現に保有し、事業期間終了時まで運用可能な企業等による応募、または、当該企業等との連携による応募であること。なお、ここでいうスパコンとは、「スーパーコンピューター導入手続」に定める理論的最高性能(※)以上のシステムに限る。

- ※「政府調達の自主的措置に関する関係省庁等会議」

(https://www.cas.go.jp/jp/seisaku/chotatsu/index.html) 別紙2を参照

- 開発した成果の社会実装を担う企業等と共同で研究開発事業を実施すること。当該企業等は、開発した成果のクラウドサービスとしての提供等を担うものとする。

- 事業成果の最大化のため、必要に応じ、本事業で構築するパイロットプラットフォームはユーザー企業等にも利用してもらい、そのフィードバックを得て更なる改善を行うなど、可能な範囲でオープンイノベーションを推進するとともに、ユーザー企業等との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等を行うこと。

### ②先端半導体製造技術の開発(助成、委託)

情報通信システムにおいては、装置内で信号の処理を行う半導体が極めて重要な役割を担う。また、デジタル化の進展により大量のデータ処理への需要が高まっており、自動運転、スマートファクトリ、物流などポスト5G時代で導入が進むアプリケーションによってさらに計算需要が増えると予想される。こうした計算需要に応えるためには高性能かつ高効率な計算基盤の構築が必要であり、その計算基盤はスーパーコンピュータやAIコンピ

ュータ、高性能コンピュータだけでなく、量子コンピュータなどの様々な計算資源をネットワークでつなぎ、情報処理を最適化したものであると考えられる。

現在、日本国内には、ポスト5Gを含む情報通信システムや計算基盤において必要となる先端的なロジック半導体等(以下、「先端半導体」)の製造能力が無く、供給安定性等の観点で脆弱な状況にある一方で、ポスト5G以降の情報通信システムや計算基盤においては、先端半導体の重要性が更に増していくと考えられる。

このため、将来的に、情報通信システムや計算基盤で用いられる先端半導体を国内で製造できる技術を確保するため、先端半導体の製造技術の開発に取り組む。具体的には、パイロットライン(一部の製造工程から成るリサーチライン、ウェハーを国内で相互に移送することにより一繋ぎのラインとして機能するものを含む。)の構築等を通じて、国内に無い先端半導体及びその周辺デバイスの製造技術(ロジック半導体と組み合わせて動作するメモリや光デバイス等に関する技術、ロジック半導体を含む複数の半導体の実装技術等を含む。)を開発する。さらに、国際連携により、最先端ロジック半導体の製造技術を確立する。

先端半導体は更なる微細化が進展しつつあり、2020年において最先端のロジック半導体は5nmノードに達するとともに、前工程の製造・プロセス技術は今後も微細化(More Moore)が継続し、高性能化・低消費電力化することが想定されている。

また、後工程の More than Moore 技術においても、2 次元高密度実装や2.5 次元・3 次元 実装の進展、パッケージ基板の大面積化により、SiP (System in Package) としての高性能化やチップ間インターコネクトの帯域幅拡大が進みつつある。

加えて、ロジック半導体が十分に機能を発揮するためには、メモリ(SRAM、DRAM等)、ストレージクラスメモリ(MRAM、PCRAM等)、ストレージ(NAND Flash等)、センサー(イメージセンサー等)等の周辺デバイスとの高速なインターコネクトの確保も不可欠であり、その帯域幅拡大やこれら周辺デバイス自体の性能向上(高速化・低消費電力化)によって、SiP全体の性能向上が期待できる。

さらに、先端半導体の製造において今後重要性が増すと考えられる分野の材料・部材に 関する技術を開発する。

具体的な開発テーマは、以下の通りとする。

### (a) 先端半導体の前工程技術 (More Moore 技術) の開発 (助成)

先端半導体は更なる微細化が進展し、IEEE の IRDS<sup>TM</sup>2020 によると、プロセスノードは 2022 年に 3nm ノード、2025 年に 2.1nm、さらにその先では 2028 年、2031 年、2034 年にそれぞれ 1.5nm、1.0nm、0.7nm へと進むことが予想されている。そして、微細化の進展に伴い、トランジスタ構造は FinFET からナノシートを活用した三次元構造や GAA(Gate All Around)構造へと変化、チャネル材料はシリコンゲルマニウム(SiGe)やゲルマニウム(Ge)、2 次元材料が多用されるようになり、配線材料も銅(Cu)からルテニウム(Ru)へ変化する等、新構造と新材料を用いたトランジスタへと変化していく。このため、半導体製造・プロセス技術全般について新規技術開発や抜本的な性能向上が必要となる。

そこで、2nm以降のプロセスノードの先端半導体において求められる高性能な露光・微細加工技術、成膜技術、アニール技術、エッチング技術、洗浄技術等のうち、特に新規開発や大幅な性能向上が必要となる製造・プロセス技術等(以下の開発対象技術全てを含める必要は無い。)を開発するとともに、パイロットラインの構築等を通じて、微細加工を施した実ウェハーによる製造装置の評価・検証を実施し、国内に無い先端性を持つロジック半導体の製造技術を確立する。

### <開発対象※1>

- 露光・微細加工技術(微細な三次元構造の加工・形成技術等)

- 成膜技術(新材料チャネル、新材料配線、極薄膜/多層積層技術等)

- 配線技術(微細孔への埋め込み、裏面配線等)

- アニール技術(極薄膜対応技術、低熱履歴化技術等)

- エッチング技術 (新材料、新構造のエッチング技術等)

- 洗浄技術(微粒子/メタル濃度の極低濃度化等)

- 革新的な高生産性プロセス技術

- 先端半導体と一体として機能するメモリ(キャッシュ用途等)の製造技術

- その他の重要な製造・プロセス技術

#### <開発目標>

- 次世代 (2.1nm や 1.5nm ノード<sup>\*\*2</sup>) の先端半導体製造・プロセスにおいて求められる 基本性能を具備する製造・プロセス技術を開発し、評価・検証すること。(製造装置と しての検証であり、先端半導体の実工場ラインでの検証までは必須としない。) なお、さらに先端的な次々世代 (1.0nm ノード以降<sup>\*\*3</sup>) の先端半導体において求められる技術開発を含める場合は、要素技術開発あるいは初期的な試作機の開発まで終えること。

- ※1 括弧内は開発対象の技術例。

- ※2 IRDS™2020中の「Logic industry "Node Range" labeling (nm)」における「2.1」及び「1.5」を意味する。

- ※3 IRDS™2020中の「Logic industry "Node Range" labeling (nm)」における「"1.0 eq"」以降を意味する。

実施に際しては、事業成果の最大化のため、必要に応じ、本事業で構築するパイロットライン等は半導体の装置・部材メーカー等にも利用してもらい、そのフィードバックを得て更なる改善を行う等、可能な範囲でオープンイノベーションを推進するとともに、ユーザー企業・機関との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。

なお、開発の実施に当たっては、個々の製造技術単体の開発に留まらず、先端半導体製造工場へ高い適用性を確保するため、開発期間全体を通じて、技術の将来的なユーザーにあたるファウンドリー企業や半導体デバイスメーカー等との連携体制を積極的に構築し、最新のユーザーニーズを踏まえ、必要に応じて、研究開発内容を柔軟に見直す等、成果の最大化に取り組むこととする。

### (b) 先端半導体の後工程技術 (More than Moore 技術) の開発 (助成)

ポスト5G情報通信システムにおけるクラウド・MECサーバー等の高性能コンピューティング、及びエッジコンピューティングでは、多様なアプリケーションに対応するために、ロジック半導体の微細化の進展による高性能化はもとより、ロジック半導体と周辺デバイス(メモリ、センサー、AIチップ、RF等)とを単一パッケージに統合する、2次元高密度実装や2.5次元・3次元実装技術の進展が不可欠である。特に、高性能コンピューティング向け実装技術ではパッケージ基板の大面積化や3次元・高密度実装向けの新規の材料、製造・プロセス技術、アセンブリー・パッケージング技術等が求められ、エッジコンピューティング向け実装技術では、小型・低実装面積での高性能化、高機能化、低消費電力化を実現可能な製造・プロセス技術が求められるとともに、合わせてこれらの実装技術を支える共通基盤技術が求められる。

そこで、先端半導体において求められる、(b1)高性能コンピューティング向け実装技術、(b2)エッジコンピューティング向け実装技術、及び(b3)実装共通基盤技術(開発にあたり以下の開発対象に記載の技術全てを含めることは必須では無い。)の開発を実施し、これにより国内に無い先端性を持つ半導体の後工程技術(More than Moore 技術)を確立する。

### (b1) 高性能コンピューティング向け実装技術

#### <開発対象>

• 先端半導体の実装に必要となるパッケージ基板の大面積化、3 次元・高密度実装向け材料技術、製造装置等の開発とこれらに対応するアセンブリー・パッケージング技術、その他の関連する重要技術。

### <開発目標>

- 高性能コンピューティング向けの先端半導体(5nm ノード以降\*1)の実装・パッケージング工程において求められる基本性能を具備する材料、製造プロセス技術、実装技術等を開発し、パイロットラインの構築等を通じて、評価・検証すること。開発に当たっては、先端半導体の実工場ラインへの適用を見据えて、歩留まり向上やシステムとしての性能向上等を実現すること。

- ※ IRDS™2020 中の「Logic industry "Node Range" labeling (nm)」における「5」以降を意味する。

### (b2) エッジコンピューティング向け実装技術

#### <開発対象>

• 大きさや技術ノードが異なる複数の半導体(ロジック、AI チップ、メモリ、センサー、RF等)を3次元積層する革新的な貼り合わせ技術、微細化が進んだ半導体間を接続する狭ピッチ接続技術、広帯域・低損失インターコネクト技術、積層対象の半導体の高性能化、その他の関連する重要技術。

#### <開発目標>

• エッジコンピューティング向けの先端半導体の3次元実装技術において求められる基本性能(小型・低背化、低消費電力、高集積、多機能等)を具備する3次元実装技術を開発し、パイロットラインの構築等を通じて、評価・検証すること。開発に当たっては、3次元実装に係る実工場ラインへの適用を見据えて、歩留まり向上やシステムとしての性能向上等を実現すること。

### (b3) 実装共通基盤技術

#### <開発対象>

- 高性能コンピューティングやエッジコンピューティング向けの先端半導体実装技術の 実装技術を支える共通的な基盤技術のうち、特に新規開発や大幅な性能向上が必要と なる以下の技術。

- 実装部材(例:パッケージ基板、封止材、放熱材、研磨剤等)

- 実装部材を構成する材料(例:コア材、絶縁材料・フィルム、接合材料等)

- 実装部材の製造・アセンブリー技術(例:パッケージ基板製造技術等)

### <開発目標>

• 先端半導体実装技術 (5nm ノード以降) において求められる基本性能を具備する基盤技術を開発し、3次元実装に係る実工場ラインへの適用を見据えて、実用性の評価・検証をすること。(部材・材料、製造装置としての検証であり、先端半導体の実工場ラインでの検証までは必須としない。)

実施に際しては、事業成果の最大化のため、半導体装置・部材メーカー、学術機関等との共同開発やその他の連携を推進する等、可能な範囲でオープンイノベーションを推進するとともに、必要に応じ、本事業で構築するパイロットライン等の活用による評価・検証、ユーザー企業・機関との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。

### (c) 露光周辺技術開発(助成)

先端半導体の更なる微細化が進展する中で、特に微細化において重要となる露光工程においては、EUV(極端紫外線)光を用いたEUV露光装置が注目されている。EUV露光装置においては、光源の波長が13.5nmと従来の露光装置と比較して短いことから、その周辺材料・部材もそれに対応した技術が必要となる。

ペリクルは、異物がフォトマスクに直接付着することを防ぐために使用される保護膜であるが、これまで EUV 光に対して十分な透過率を有するペリクルは開発されていない。現時点で EUV 露光装置を用いた先端半導体の製造はペリクル無しで行われる場合があり、これがフォトマスクの寿命に影響を与え、高コストの一因となっていると考えられる。そこで、EUV 露光装置向けのペリクルを開発する。

また、微細化はマルチパターニングによっても実現が可能である一方、マルチパターニングは露光時間やマスク枚数の増加により高コスト化の要因となるため、可能な限り少ない露光回数であることが望ましい。そのため、EUV 露光装置では、より微細なパターニングを行うため開口数(NA)を向上させる等の研究開発が行われており、フォトレジストもそれに対応した高い分解能が求められている。そこで、微細化に対応した次世代フォトレジストの開発を行う。

### (c1) EUV 露光装置向けペリクル技術開発

### <開発対象>

• EUV 光に対する透過率や耐熱性等を有し、EUV 露光装置に適用可能なペリクル。

### <開発目標>

- EUV 光透過率: 94%以上

- 光源からの熱に対する耐熱性:800W以上

#### (c2) EUV 露光装置向け次世代フォトレジスト技術開発

#### <開発対象>

• EUV 露光プロセス向けの次世代フォトレジスト。

#### <開発目標>

- 1.5nm ノード\*以降の先端半導体製造に適用される高 NA EUV 露光プロセスにおいて必要となる基本的な性能を有すること。

- ※ IRDS™2020 中の「Logic industry "Node Range" labeling (nm)」における「1.5」を意味する。

### (d) 国際連携による次世代半導体製造技術開発 (委託)

次世代半導体製造技術の確立のためには、国内にない技術や知見を活用することが必要であり、国際連携が不可欠である。

2025年以降に最先端になると予想されている 2nm ノードでは、GAA(Gate All Around)構造や新材料の導入などが必要である。こうした次世代半導体の生産能力を確保するためには、各プロセス技術開発や製造装置の評価検証に加えて、所望のデバイス特性や歩留まり・コストを達成する必要がある。そのためには、微細構造を実現するために必須となる最先端の露光技術によって GAA 構造を実現するための製造技術や、それら技術で実現するデバイスの検証・評価技術等が不可欠である。一方で、これらの技術のうち、一部が現在国内には無い。そこで、2nm ノードの最先端半導体で求められる基盤的な技術を国際連携により確保した上で、2nm ノードで実現しうるトランジスタ集積度と信頼性を達成する製造技術を開発し、現在国内に無い最先端ロジック半導体の製造技術を確立する。

エレクトロニクス技術とフォトニクス技術を組み合わせた光電融合技術は、高速性・低損失性を有し、高性能かつ省エネな計算基盤の実現に重要な技術である。光電融合デバイスを半導体パッケージ内へ実装することによって、CPUやメモリ、xPU等の計算資源を、電気配線を介さずに、直接・遠距離まで高速・低損失に接続できる。また、必ず CPU を介してサーバ単位で処理をするような従来のアーキテクチャではなく、メモリプールを共有しつ合プロセッサが独立に処理を実行できるメモリセントリックアーキテクチャの実現が期待される。光電融合による分散型メモリセントリックコンピューティング技術の実現によって、高度なデータ処理を、最適にエッジ拠点・地域クラウド間で組み合わせて実行することで、消費電力の低減を実現する。その際、光電融合デバイスや共有メモリ等と相互に連携して上記システムをくみ上げる必要があるが、光電融合デバイスと同一パッケージ内に実装する高性能 CPU 等の先端半導体メーカーは現在国内には無いため、国際連携により必要な仕様等の知見を確保しながら、本技術における共通基盤技術の開発を進める。

### (d1) 高集積最先端ロジック半導体の製造技術開発

### <開発対象>

• 最先端半導体に必要なトランジスタ集積度と信頼性を達成するロジック半導体製造技

術。

#### <開発目標>

- テストチップにおいて、以下の SRAM を GAA 構造により作り、動作を実証すること。また、動作寿命予測に資する高温動作寿命試験\*\*1 を実施すること。

- ビットセル面積: 0.0187 μm² 以下<sup>\*2</sup>

- アレイ記憶容量:128 Mbit 以上

- ※1 IEC 等に準拠すること。また、ターゲットとする用途に応じた測定条件・目標値を提案時に設定すること。

- ※2 IRDS™ 2022 UPDATE MORE MOORE に記載の 2nm ノードに準拠。

### (d2) 光電融合による分散型メモリセントリックコンピューティング技術開発 <開発対象>

• パッケージ内に光電融合デバイスを実装した半導体デバイス、およびそれを用いた分 散型メモリセントリックコンピューティング技術

#### <開発目標>

- パッケージ内に光電融合デバイスを実装した半導体デバイス性能指標(帯域密度/電力) [(Gbps/mm)/(pJ/bit)]:研究開発開始時点で普及している製品と比較して800倍以上

- 本テーマで開発した半導体デバイスでデータセンタ間を直接接続し、メモリセントリックアーキテクチャによるコンピューティングシステムを実証すること。

- ※ 提案者にて具体的な目標値を提案時に設定すること。

### <応募条件>

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

- ※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同 国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

### (e) 次世代メモリ技術開発(助成)

ポスト5G情報通信システムにおいては、生成されるデータが極めて大量になることが見込まれている。それに伴い、データセンタにおいてはデータ処理量が増加し、電力消費量が増大することが予想されている。また、近年導入が進んでいるAI処理に必要な大量の計算処理を短時間で実行するため、プロセッサの高性能化と共に、プロセッサとの間で高速にデータ転送を行う広帯域メモリ(HBM)の重要性が高まっている。今後さらにAIの需要は増大していくと考えられ、これに伴いメモリにはさらなる広帯域化が求められると共にメモリ転送に伴う電力消費が膨大になると考えられるため低消費電力でこれを実現する技術が求められる。

そこで、広帯域かつ低消費電力なHBM製造技術の開発を行う。

#### (e1)次世代広帯域・低消費電力HBMの製造技術開発【GX】

#### <開発対象>

・次世代広帯域・低消費電力HBMの製造技術。

### <開発目標>

- ・以下の性能要件を満たした上で、一般的なメモリに求められる信頼性要件を満たすこと。

- ーメモリ密度: 0.5Gbit/mm<sup>2</sup>以上

- ーダイあたり容量:32Gbit 以上

- 積層数:12層以上

- -帯域:2TB/s 以上

- 伝送量あたりの消費電力の削減割合:研究開発開始時点の製品と比較して30%以上

### ③先導研究(委託、助成)

研究開発項目①②に関係するものであって、ポスト5Gでは実用化に至らない可能性があるものの、ポスト5Gの後半から5Gの次の通信世代(以下、「ポスト5G後半以降」)にかけて有望と考えられる技術課題について、先導的な研究開発に取り組む。研究開発項目①に関係する技術課題は委託事業、研究開発項目②に関係する技術課題は助成事業として実施する。

本研究開発項目では、研究開発終了時点において、実用化を前提とした研究開発への移行に向けた根拠データの取得等により、技術の確立の見通しを付けることを開発目標とする。また、開発対象は、ポスト5G後半以降にかけて情報通信システムに適用され、一定の市場シェア獲得のポテンシャルを有し、我が国の国民生活や経済、産業等への波及効果が期待される技術とする。

研究開発項目①に関係する具体的な開発テーマとして想定する開発技術は、(a) ~ (e) についてそれぞれ以下の通りとし、これら開発テーマ毎に記載の開発対象の全てあるいは一部について研究開発を行う。

得られた研究開発成果については、5G将来仕様となる3GPP等の標準化団体との連携を図ることとし、評価手法の提案、データの提供、標準化活動等を積極的に行う。

### (a) ネットワーク関連技術

ポスト5G後半以降のネットワークにおいては、5Gの10倍あるいは100倍の高速化・大容量化・低遅延化・多数同時接続等に加え、超低消費電力化、高信頼性、自律性、拡張性、などの新たな性能が求められるとともに、多種多様の新たなサービスの要求に応じたQoS(Quality of Service)が求められるため、仮想化技術やAI技術の高度化等による高速、高機能、柔軟かつ信頼性の高いネットワークのリソース分配制御技術や管理、運用技術、高精度な同期技術、クラウドサーバーやMECサーバーの低消費電力化技術が重要となる。また、今後、量子コンピュータ等の新原理に基づく高速計算機の登場が予想され、社会基盤の通信システムについても堅牢性が高くセキュアな通信が求められる。

これらに対応すべく、本開発項目では、多種多様なサービスに対応可能なコアネットワークからアクセスネットワーク、MEC、基地局、端末まで、ネットワーク全体(あるいは一部)を統合的に管理する技術や、エンドツーエンドでのデータ到達時間の超低遅延を実現する技術、安全性の担保されたオープンソースのソフトウェア基盤技術、サーバーの超低消費電力化技術の開発等を行う。さらに、今後、新原理に基づく高速計算機等でも破ることができない、堅牢性の高いセキュアな通信を実現する暗号通信技術等についても開発を行う。

| 開発対象                         | 開発技術例                            |  |  |  |  |  |  |

|------------------------------|----------------------------------|--|--|--|--|--|--|

| ネットワーク統合                     | 様々な不確実性を伴う状況下においても高信頼のネットワークやア   |  |  |  |  |  |  |

| 管理技術(超高信                     | プリケーションを実現するため、クラウド、NW、MEC、端末・エ  |  |  |  |  |  |  |

| 頼性)                          | ッジに至るまで、各機器のリソース情報を把握し、処理の細分化、動  |  |  |  |  |  |  |

| 的な処理の移行や最適配置、タスク・リソースの最適分配等を |                                  |  |  |  |  |  |  |

| する統合管理技術の開発、AI技術の高度な利用によるSDN |                                  |  |  |  |  |  |  |

|                              | ftware Defined Network)制御、運用自動化技 |  |  |  |  |  |  |

|                              | 術の開発                             |  |  |  |  |  |  |

| リアルタイム制御                     | 多種多様なリアルタイム性が求められる用途における要求を満たす   |  |  |  |  |  |  |

| 技術 (超低遅延性)                   | ため、有線区間、無線区間あるいはその変換部分、インターフェイス  |  |  |  |  |  |  |

|                              | 部分での低遅延化を通じて、超低遅延性をエンドツーエンドで実現す  |  |  |  |  |  |  |

|                              | るための技術の開発                        |  |  |  |  |  |  |

| オープンソースソ                     | アプリケーション毎のスライシング、低消費電力化、完全SDN化、  |  |  |  |  |  |  |

| フトウェア技術                      | MEC統合などの柔軟な制御の実現とポスト5G後半におけるロー   |  |  |  |  |  |  |

| (柔軟性・低コス | カル5Gの更なる普及や次の世代に向けて、安価に構築可能なオープ |

|----------|---------------------------------|

| 下)       | ンソースをベースとしたコアネットワークソフトウェア技術等の開  |

|          | 発                               |

| セキュア通信技術 | 量子コンピュータ等の新原理の高速計算機でも破ることができない、 |

| (超安全性)   | 堅牢性が高くセキュアな大容量通信を実現可能な量子暗号通信に資  |

|          | する小型チップ技術の開発、機密度の高い情報やプライバシー情報等 |

|          | を端末・エッジ、MEC等に留めながら求められる各種計算処理(例 |

|          | えばAIモデル学習)を可能とするデータの最適配置やエッジ処理に |

|          | よるセキュリティ技術の開発                   |

| クラウドサーバー | クラウドやMECサーバーにおけるビット当たりのエネルギー効率  |

| やMECサーバー | を飛躍的に向上するコンピューティングアーキテクチャの開発、当該 |

| の低消費電力化技 | アーキテクチャを利用してAI主導のオペレーションを実現する高  |

| 術(超低消費電力 | 度な知性ネットワークの開発                   |

| 性)       |                                 |

### (b) 伝送路関連技術

ポスト5G後半以降の伝送路において、5Gの10倍あるいは100倍の高速化・大容量化・低遅延化・多数同時接続等を実現するためには、必然的に更なる大容量かつ高速な伝送技術が求められる。データ容量が増加するだけでなく、産業用途向けの低遅延性もミリ秒からマイクロ秒オーダの精度が求められ、エンドツーエンドでの性能要求を担保するには伝送路における高速大容量かつ低遅延の通信の実現が重要となる。このため光伝送の更なる高速化、あるいは高速無線リンクの活用などの新たな伝送技術の開発が望まれる。

これらに対応すべく、本開発項目では、フロントホールに対応した大容量かつ低消費電力な光リンク技術、MECの情報処理性能を飛躍的に向上する光インターコネクト技術、メトロ・長距離網向け光伝送ネットワークの広帯域化技術の開発を行う。

| 開発対象      | 開発技術例                            |

|-----------|----------------------------------|

| フロントホール   | 大容量(1アレイ・1波長あたり1Tbps級以上)・低消費電力・  |

| (RU、DU間)向 | 低コストなレーザー素子と素子のアレイ化技術の開発、並びにそのフ  |

| け光リンク技術   | ロントホール向け光ファイバ伝送性能の検証             |

| MEC内通信向け  | MECの情報処理性能を飛躍的に向上させるためにプロセッサが実   |

| 光インターコネク  | 装される電子基板に光インターコネクトを一体的に集積し、MECに  |

| ト技術       | 搭載される光トランシーバとプロセッサ間等の通信の光化及び大容   |

|           | 量化(10Tbps級)を省電力で実現可能とする光電子融合型集積  |

|           | 技術の開発                            |

| メトロ・長距離網  | 既存の波長帯域用の光送受信機や波長合分波器をそのまま活用しつ   |

| 向け光伝送ネット  | つ光伝送の大容量化を実現するための波長の一括変換技術や先端的   |

| ワークの大容量化  | な波長、空間多重技術、システム技術等により伝送容量を低消費電力、 |

| 技術        | 低コストで数倍に拡大するメトロ・長距離網の大容量化技術の開発   |

| 光アクセスネット  | RANの基地局装置(無線部、制御部)と仮想化対応の光伝送装置が  |

| ワークの仮想化技  | 連動してスライスを構築し、サービス利用状況の変動に追従して動的  |

| 術         | に資源連携制御する技術や、多用なサービス毎に求められる品質レベ  |

|           | ル(大容量、低遅延、多数接続)を踏まえ、トラフィック状況の学習  |

|           | と最適な資源予測により多様なサービスの品質の維持を可能とする   |

|           | 動的スライス構築制御技術                     |

#### (c) 基地局関連技術

ポスト5G後半以降の基地局においては、さらなる高速大容量通信が加速され、ミリ波のみならずテラヘルツ波を含む高周波かつ広帯域の電波利用が検討されている。しかし、その高周波の特性による直進性や伝搬損失の大きさなどの課題が存在し、基地局においては集積回路等のデバイス・材料レベルでの革新的な技術が求められる。これと並

行し、コアネットワークにおいて先行している仮想化技術は、無線アクセスネットワークのCU、DUのみならずRUへと拡張することが予想される。

これらに対応すべく、本開発項目では、ミリ波・テラヘルツ帯の基地局に搭載可能な新規のアンテナ技術やビームフォーミング技術、高周波や高速大容量伝送時に低損失な新規基板材料、RF-IC等の集積回路技術、信号増幅器技術、多数同時接続時の通信品質向上技術の開発を行う。また、ソフトウェア基地局の自動最適化技術、CU・DU・RUを含めた基地局の仮想化、柔軟化に関する研究開発も実施する。

| 開発対象     | 開発技術例                           |

|----------|---------------------------------|

| 新規アンテナ技術 | 高周波(ミリ波・テラヘルツ帯)の高精度計測に基づく、メタマテリ |

|          | アル等新規材料を用いたミリ波・テラヘルツ帯向けのアレイアンテナ |

|          | や反射板の設計・製造技術の開発及び新規アンテナの性能検証、ビー |

|          | ムフォーミングアンテナの小型化・低消費電力化技術の開発     |

| ミリ波・テラヘル | ミリ波・テラヘルツ帯向けシリコン集積回路の高精度設計・評価技術 |

| ツ帯向け集積回路 | の開発と動作検証、超低ノイズの広帯域発振器、超高速送受信機、評 |

| 技術       | 価技術の開発                          |

| 新規基板材料等の | ミリ波・テラヘルツ帯の情報通信機器向けの低誘電率かつ低損失な次 |

| 高機能材料技術  | 世代電子基板材料等、高機能材料技術の開発            |

| 基地局増幅器のた | 4G、5G、さらには5Gの次の通信世代で想定される広い周波数帯 |

| めの広帯域化回路 | 域をカバーすることが可能な基地局信号増幅器の広帯域化技術(従来 |

| 技術       | 比で数十倍)の開発、及び多数同時接続時の通信品質向上技術の開発 |

| ソフトウェア基地 | 基地局ソフトウェアの一部機能のHWアクセラレータ化に際して、各 |

| 局の自動最適化技 | アクセラレータの種別や用途に最適となるようソフトウェア等を自  |

| 術        | 動的に変更する技術、異種ハードウェア混合システム(CPU、DS |

|          | P、FPGA、ASSP等)において各HW要素に最適な機能分割を |

|          | 実現する自動最適化技術、基地局システムの能力を可視化する技術  |

| 基地局の仮想化、 | 仮想化ソフトウェア基地局設備についてキャリア5Gとローカル5  |

| 柔軟化技術    | Gとで共用すること等により低コスト化を可能とする技術、ローカル |

|          | 5Gにおいて単一のコアで異なるベンダーの基地局を管理・制御する |

|          | 技術やRUの広帯域化技術の開発                 |

### (d) 革新的応用システム技術

ポスト5G後半以降、産業のスマート化、物流、建築、農業、健康・医療、教育、遠隔オフィス等、様々な分野で5Gや5Gの次の通信世代の利用を広げ、有効性を実感してもらうためには、新しく独創性に富む応用システム(アプリケーション)のユースケース開拓・拡大を進めることが重要となる。産業用途を鑑みると、低遅延・多数同時接続及び複数情報の同期技術などの性能要求がさらに高まり、ポスト5Gや5Gの次の通信世代の通信システムのインフラのみならず、そのシステム上でエンドツーエンド通信を行うエッジ端末や応用システムも含めて開発し性能を担保する必要がある。一方、ポスト5Gや5Gの次の通信世代をさまざまな産業に普及させるためには、教師無し学習など新たなAI技術を適用した自律的なネットワークの保守・運用技術の開発により、導入の敷居を下げる必要がある。

これらに対応すべく、本開発項目では、ポスト5G後半以降の情報通信システムを活用することにより新規に創出されるユースケースを特定し、エンドツーエンドで求められるエッジ端末や応用システム等における課題を明確化し、その課題を解決する技術を開発する。

| 開発対象     | 開発技術例                           |

|----------|---------------------------------|

| デジタルツイン実 | 無線電波の到達時間差解析や画像等の高速解析による工場内での多  |

| 現のための高精度 | 数の機器・モノ・人等の3次元センチメートル単位測位や各種モビリ |

| 測位・同期制御技 | ティ(自動車、鉄道、ドローン等)の位置測位によりデジタルツイン |

| 術        | を実現する技術及びミリ秒単位での高精度なリアルタイム機器制御  |

|          | 技術の開発                           |

|----------|---------------------------------|

| MEC利用による | ロボットにセンサ・アクチュエータ等の機能のみを残し、それ以外の |

| アダプティブロボ | 機能をMECへ集約し、大容量・高速通信を介してロボットの位置・ |

| ット群リアルタイ | 状態の認識、各ロボット及びロボット群の最適化制御を行う等、無線 |

| ム制御技術    | によりロボット群をリアルタイムに遠隔制御する技術の開発     |

| その他の革新的応 | 産業のスマート化、物流、建築、農業、健康・医療、教育、娯楽、遠 |

| 用システム技術  | 隔オフィス等の分野において、ポスト5G後半以降の情報通信システ |

|          | ムにより新規のユースケースを創出するための基盤となる革新的な  |

|          | 応用システム技術の開発(現状技術の組み合わせや実証のみの開発は |

|          | 対象外。広範なシステムに応用可能な技術開発を対象とする。)   |

### (e) MEC関連技術

ポスト5Gネットワークの低遅延性・多数同時接続とIoT、AI等の活用により多様な産業活動や国民生活のスマート化が期待されている。このうち、低遅延性を実現するためには、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理を可能とするMECサーバーの普及が求められる。また、低遅延ネットワークを実現するためには、MEC、ネットワーク構成機器、MECと情報通信するエッジデバイス自体の高性能化も求められる。これらの取組を進めることによりデータの伝送距離の短縮、伝送量削減による低消費電力化が期待される。

このため、本開発項目では、ポスト5G後半以降のさらなる低遅延かつ低消費電力な情報通信システムを実現するため、MECのみならず、ネットワーク構成機器、MECと情報通信するエッジデバイス自体の低遅延化、高性能・低消費電力化に係る技術について以下の開発を行う。

| 開発対象      | 開発技術例                                |

|-----------|--------------------------------------|

| MECを構成する  | MEC向け半導体、周辺デバイス等の高性能化・低遅延化に係る設計      |

| 半導体、周辺デバ  | 技術、MEC・クラウドサーバー向け高速な読み出し書き込みを実現      |

| イス等の高性能   | する広帯域、低遅延、大容量なメモリモジュール設計技術           |

| 化・低遅延化    |                                      |

| MEC内通信向け  | MECの情報処理性能を飛躍的に向上させるためにプロセッサが実       |

| 光インターコネク  | 装される電子基板に光インターコネクトを一体的に集積し、MECに      |

| ト技術【再掲】   | 搭載される光トランシーバとプロセッサ間等の通信の光化及び大容       |

|           | 量化(10 T b p s 級)を省電力で実現可能とする光電子融合型集積 |

|           | 技術の開発                                |

| クラウドサーバー  | クラウドやMECサーバーにおけるビット当たりのエネルギー効率       |

| やMECサーバー  | を飛躍的に向上するコンピューティングアーキテクチャの開発、当該      |

| の低消費電力化技  | アーキテクチャを利用してAI主導のオペレーションを実現する高       |

| 術(超低消費電力  | 度な知性ネットワークの開発                        |

| 性)【再掲】    |                                      |

| MEC利用による  | ロボットにセンサ・アクチュエータ等の機能のみを残し、それ以外の      |

| アダプティブロボ  | 機能をMECへ集約し、大容量・高速通信を介してロボットの位置・      |

| ット群リアルタイ  | 状態の認識、各ロボット及びロボット群の最適化制御を行う等、無線      |

| ム制御技術【再掲】 | によりロボット群をリアルタイムに遠隔制御する技術の開発          |

上記 (a)  $\sim$  (e) とともに付随する周辺技術を合わせて開発することや、上記と同等レベル以上に重要な技術の開発があれば、追加的に実施可能とする。

研究開発項目②(助成)に関係する具体的な開発テーマとして想定する開発技術は、ポスト5Gの後半以降に有望と考えられる(a)~(b)の技術のうち、特に新規開発や大幅な性能向上が必要となる技術に関する先導的な研究開発やの探索型開発に取り組む。これら開発

テーマ毎に記載の開発対象及び開発技術例の全てあるいは一部について研究開発を行う。本研究開発項目では、研究開発終了時点において、実用化を前提とした研究開発への移行に向けた根拠データの取得等により、技術の確立の見通しを付けることを開発目標とする。また、開発対象はポスト 5 G後半以降にかけて先端半導体製造技術に適用され、一定の市場シェアを獲得するポテンシャルを有し、我が国の国民生活や経済、産業等への波及効果が期待される技術とする。

### (a) 先端半導体製造技術(前工程技術)

| 開発対象 開発技術例                            |                                                                                                                                                                  |  |  |  |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 先端半導体の前工<br>程 技 術 ( More<br>Moore 技術) | 露光・微細加工技術、成膜技術、配線技術、アニール技術、エッチング技術、洗浄技術、革新的な高生産性プロセス技術、先端半導体と一体として機能するメモリの製造技術等のうち、先端的な次々世代(1.5nmノード以降*)の先端半導体において求められる要素技術                                      |  |  |  |  |  |  |  |

|                                       | (例) ・次世代 EUV 向け部材・材料技術 ・ナノシート積層構造の形成技術、洗浄技術 ・トランジスタの 3 次元積層技術 ・ナノシート構造向け二次元材料 ・層間・配線間の次世代絶縁材料 (Low-k 材料) ・薄膜・多層構造体のアニール技術 ・低熱負荷処理プロセス技術 ・次世代不揮発性メモリ技術、メモリ向け新材料技術 |  |  |  |  |  |  |  |

### (b) 先端半導体製造技術(後工程技術)

| 開発対象          | 開発技術例                               |

|---------------|-------------------------------------|

| 先端半導体の後工      | 高性能コンピューティング向け実装技術、エッジコンピューティング     |

| 程技術(More than | 向け実装技術、実装共通基盤技術等のうち、先端的な次々世代 (1.5nm |

| Moore 技術) の開発 | ノード以降*) の先端半導体の実装において求められる要素技術      |

|               |                                     |

|               | (例)                                 |

|               | ・実装部材(パッケージ基板、封止材、放熱材、研磨剤等)         |

|               | ・実装部材を構成する材料(コア材、絶縁材料・フィルム、接合材料、    |

|               | ボールバンプ等)                            |

|               | ・実装部材の製造・アセンブリー技術(パッケージ基板製造技術)      |

|               | ・パッケージ基板の高速・微細加工装置に係る要素技術           |

|               | ・超微細ハンダバンプ形成技術                      |

|               | ・三次元接合・貼り合わせ技術や評価技術                 |

|               | ・高周波対応可能なパッケージ封止材料                  |

※IRDS™2020 中の「Logic industry "Node Range" labeling (nm)」における「"1.5"」以降を意味する。

### (2) 研究開発期間

研究開発項目①~③は、原則として以下の期間で実施することとし、必要な場合には、個々の研究開発の性質等に応じて、柔軟に対応するものとする。

なお、研究開発終了時点で実用化に向けた課題が残る場合であって、終了時継続評価(実施者の希望を踏まえて評価の実施有無を判断)の結果、必要性が認められた場合には、追加的に継続研究開発(原則3年以内。ただし、基金設置期間に限る。)を実施することとする。継続研究開発を希望する可能性がある場合、実施者は、公募に対する提案書に、想定される継続研究開発の内容、想定される追加的な実施者及び再委託先、想定される研究開発費を記

載することとする。継続研究の委託、助成の別については、継続の判断時に開発テーマごとに判断する。

①ポスト5G情報通信システムの開発(委託、助成) 研究開発開始時点から原則3年(36か月)以内とする。ただし、(f1)、(f2)、(g1) は原則5年(60か月)以内とする。

- ② 先端半導体製造技術の開発(助成、委託) 研究開発開始時点から原則5年(60か月)以内とする。

- ③先導研究(委託、助成) 研究開発開始時点から原則3年(36か月)以内とする。

#### 4. 成果最大化に向けた仕組み

社会への研究開発成果の普及を強く促すため、以下の取組を実施する。これらの取組の具体的な実施方法については、事前にNEDOが経済産業省商務情報政策局(以下、「商務情報政策局」)に相談した上で、商務情報政策局が決定する。

#### (1) ユーザーのニーズ把握

研究開発の開始時点から、研究開発成果を利用するユーザーとの意見交換を行うとともに、ユーザーによる試作品の評価(利用サービスの提供を含む。)を積極的に実施することにより、研究開発期間全体を通じて、ユーザーのニーズ(技術面、コスト面 等)を適切に把握する。当該ニーズを踏まえ、必要に応じて、研究開発内容を柔軟に見直すことにより、研究開発の方向性を最適化する。

特に、研究開発項目①における「システム技術開発」の開発テーマについては、研究開発成果を海外に広く展開する観点から、国外ユーザーとの意見交換や当該ユーザーによる評価を重点的に実施する。

### (2) 研究開発期間中の製品化

ユーザーによる試作品の評価等を通じて、研究開発期間中に製品化の見込みが得られたものについては、研究開発期間中であっても研究開発の内容から一部を切り出し、早期の製品化に取り組む。

### (3) 民間企業等による市場展開を促す仕組み

研究開発項目①における「システム技術開発」の開発テーマ(但し、ステージゲート審査等により、商務情報政策局及びNEDOの判断によって研究開発期間の途中で終了した開発テーマを除く)については、実施者に対して市場展開を強く促す観点から、以下の研究開発費返還制度を適用する。

#### <研究開発費返還制度>

実施者は、公募に対する提案時に、以下に掲げる算出方法により費用対効果指標を設定することとし、費用対効果指標の設定値(以下、「設定値」)が1.0を超える場合に限り、提案を認める。その後、2027年度を目途に、費用対効果指標の達成状況を評価し、費用対効果指標の実績値(以下、「実績値」)が設定値を下回る場合には、実施者はNEDOに対して「委託費受領額×返還率」の金額を返還する。

委託費受領額は、各開発テーマにおいて実施者が受領した全委託費から、加速など予算配分の増加額及び継続研究開発において受領した委託費を差し引いた金額を表す(研究開発費返還制度において、委託費受領額は常に同じ意味で用いる)。

返還率は、以下に掲げる方法により算出する。

達成状況の評価に用いる設定値は、提案時点の設定値を原則とするが、研究開発期間中の引き上げ、もしくは、著しい経済情勢の変動、天災地変その他不可抗力(パンデミック、紛争、政変、技術潮流の著しい変化 等)、又は研究開発開始時点で予測することのできない事由であって実施者の責任によらない事情があると商務情報政策局及びNEDOが認めた場合の引き下げについては、変更を認める。

なお、高い目標への挑戦を促す観点から、設定値に応じて、開発テーマの予算規模(実施者による提案1件当たりの提案時委託費(継続研究開発において想定される研究開発費は含まない)の上限)を決定するとともに、採択後に行われる開発テーマの加速など予算配分の増加や縮小、継続研究開発の必要性を判断する終了時継続評価に反映させる。本制度を実施する上で必要な事業情報については、必要に応じて、実施者に対して提供を求める。

### 【費用対効果指標(設定値及び実績値)の算出方法】

- (a1) クラウド型コアの高度化技術の開発: 4 Gコア及び 5 Gコア用ソフトウェアの売上高増加額/予算額

- (a2) クラウド型ネットワーク統合管理・自動最適化技術の開発: OSS及びMANO用ソフトウェアの売上高増加額/予算額

- (b1) 光伝送システムの高速化技術の開発: 1 波長当たり最大伝送速度200Gbps以上の光伝送装置の売上高増加額/ 予算額

- (b4) 固定無線伝送システム大容量化技術の開発: ミリ波帯固定無線伝送装置の売上高増加額/予算額

- (b5) バス型伝送高度化技術の開発: ケーブル分岐機能を備えた光伝送システム(基地局~モバイルコア区間部分) の売上高増加額/予算額

- (c1) 仮想化基地局制御部の高性能化技術の開発: 4 G基地局及び5 G基地局の売上高増加額/予算額

- (c2) 基地局無線部の高性能化技術の開発: 同上

- (c7) RAN制御高度化技術の開発: RICソフトウェア、およびRICソフトウェアと同時にセット販売するDU とCUの売上高増加額/予算額

- (f1) 超分散コンピューティング技術の開発: 開発技術を用いたプラットフォームサービス業務およびシステム開発委託業務 の売上高増加額/予算額

- (f2) 高機密データ流通技術の開発: 同上

- ※予算額は、設定値を算出する場合には提案時委託費、実績値を算出する場合には委 託費受領額をそれぞれ表す(研究開発費返還制度において、予算額は常に同じ意味 で用いる)。

- ※費用対効果指標は、小数点以下第2位を四捨五入して算出。

- ※売上高増加額は、原則として、「2024年度から2026年度における各年度の売上高のうち、最も高いもの」から「研究開発開始前年度及び前々年度における売上高の平均値」を差し引いた金額を指す。

- ※実施者が財務諸表等の作成において採用している会計期間が政府の会計年度(4月1日~翌年3月31日)と異なる場合であって、前者の期末が後者の年度末よりも前である場合には、前者の会計期間における売上高を用いて費用対効果指標を算出することができる。

- ※上記の売上高については、製品単体の他、必要に応じ、当該製品の導入等に係るシステム構築費、工事費、保守費、管理費、サービス利用料等を含めることができる(但し、製品単体の売上高以外を含める場合には、製品単体の売上高とその他の売上高のそれぞれを明示することとし、必要な場合には、その他の売上高の内訳も提示することとする)。また、売上高に、実施者の子会社や関連会社の売上高を含める場合は、原則として連結決算における売上高を用いる。なお、売上高の計上方法は設定値と実績値の算出時で、同じ条件で算出する。

### 【返還率の算出方法】

4.0 < 実績値</li>:0%

• 1. 0 < 実績値 ≦ 4. 0: (40 - 10 × 実績値) %

実績値 ≤ 1.0: 50%

なお、上記は事業開始年度が2020年度の場合で記載したもの。事業開始年度が2021年度以降となった場合は、上記の「費用対効果指標の達成状況を評価する年度(2027年度)」は「開始年度の7年後の年度」と読み替える(ただし、(f1)および(f2)については、「開始年度の9年後の年度」と読み替える)。また、上記の売上高増加額の定義に記載されている「2024年度から2026年度」は「事業開始年度の4年後の年度~事業開始年度の6年後の年度」と読み替える(ただし、(f1)および(f2)については、「事業開始年度の6年後の年度~事業開始年度の8年後の年度」と読み替える)。

### (4) 民間企業等による負担

助成事業として実施する開発テーマについては、助成率 (1/2、1/3)を導入し、民間企業に対して自己負担を求める。ただし、学術機関等(国公立研究機関、国立大学法人、公立大学法人、私立大学、高等専門学校、独立行政法人及びこれらに準ずる機関。(以下、「学術機関等」))に対する共同研究費については、定額助成とすることが出来るものとする。また、当該助成事業の交付先の委託先において間接経費を計上する場合は、必要に応じ、経費の執行用途等について事前に協議し、助成事業の目的に合致したものであることの確認を受けた上で執行することとする。加えて、学術機関等への共同研究費のうち、公共性・公益性があると認められた研究開発に要する費用については、収益納付の対象から除外できること

とする。収益納付の具体的な計算方法等については、原則として別紙の通りとする。これを 踏まえ、事前にNEDOにて計算方法案を作成し、商務情報政策局の承認を受けた後に、決 定するものとする。

また、委託事業として実施する開発テーマについて、研究開発計画で設定した予算規模を超える研究開発費が必要となる場合には、予算規模を超える費用(以下、「自己開発投資額」)を自己負担すること及び研究開発終了後に当該負担の実績(以下、「実負担額」)及びその内訳をNEDOに対して報告することを、実施者が採択時に誓約することを条件として、実施を認める。なお、研究開発終了時点で、実負担額が「自己開発投資額 × (委託費受領額/提案時委託費)」を下回る場合には、実施者はNEDOに対してその差額を返還する。なお、実施者が自己開発投資額を負担して実施する研究開発においても、NEDOからの委託費により取得・導入した機械装置、設計ツール、ソフトウェア等は、使用可能とする。

### (5) 「GX」の開発テーマにおける社会実装のコミット

「GX」の開発テーマについては、「GX実現に向けた基本方針(令和 5 年 2 月 10 日閣議決定)」に基づき、GXの実現に向けた研究成果の社会実装への実施者のコミットの状況を提案時及びステージゲート審査等で確認する。

### 5. 実施者の採択

本事業における研究開発の実施者は、NEDOが公募(必要に応じて、複数回実施)により採択する。

### (1) 予算規模

研究開発項目①~③における開発テーマは、以下の予算規模(実施者による提案1件当たりの提案時委託費及び助成費(NEDO負担額、以降も同じ定義とする)の上限。継続研究開発において想定される研究開発費は含まない)を原則として提案を公募する。

なお、公募による実施者の採択後、必要に応じて、以下の予算規模に限らず、研究開発の 進捗や成果、情勢変化を踏まえた最新の事業化見通しとこれに向けた取組状況、費用対効果 等を踏まえ、各開発テーマの予算配分の増加・縮小を実施する。

①ポスト5G情報通信システムの開発(委託、助成)

提案1件当たりの提案時委託費及び提案時助成費は、原則として以下を上限とする。開発テーマが助成事業である場合、またその際の助成率を(助成、助成率)で表し、(助成、助成率)表記がない開発テーマは委託事業であることを表す。

なお、「システム技術開発」の開発テーマについては、研究開発費返還制度の一環として、以下の方法で設定した変動率を導入するとともに、研究開発期間が1.5年(18か月)以下の場合を除き、研究開発開始からステージゲート審査後3か月までに計上可能な提案時委託費は、研究開発期間全体の8割を上限とする。ただし、実施者の採択後、必要に応じて、予算配分の増加を実施する場合はこの限りではない。

- (a1) クラウド型コアの高度化技術の開発: 75億円×変動率

- (a2) クラウド型ネットワーク統合管理・自動最適化技術の開発: 75億円×変動率

- (b1) 光伝送システムの高速化技術の開発: 75億円×変動率

- (b2) 光伝送用DSPの高速化技術の開発: 100億円

- (b3) 微細化の進展に対応した高速不揮発性メモリ技術の開発: 20億円

- (b4) 固定無線伝送システム大容量化技術の開発: 15億円×変動率

- (b5) バス型伝送高度化技術の開発: 15億円×変動率

- (b6) 超高速光リンク技術の開発: 10億円

- (b7) 光スイッチ高度化技術の開発: 5億円

- (c1) 仮想化基地局制御部の高性能化技術の開発: 40億円×変動率

- (c2) 基地局無線部の高性能化技術の開発: 75億円×変動率

- (c3) 基地局装置間の相互接続性等の評価・検証技術の開発: 75億円

- (c4) 高周波デバイスの高出力・小型化技術の開発: 25億円 (継続研究開発(助成、助成率1/2): 5億円)

- (c5) 高温動作可能な光接続技術の開発: 50億円

- (c6) 高周波帯アンプー体型アレイアンテナ実装技術の開発: 30億円

- (c7) RAN制御高度化技術の開発: 20億円×変動率

- (c8) O-RANインテグレーション基盤技術の開発(助成、助成率1/2):150億円

- (c9) O-RAN基地局シェアリング技術の開発(助成、助成率1/3): 50億円

- (d1) MEC向け大規模先端ロジックチップ設計技術の開発: 50億円

- (d2) MECサーバー向け広帯域・大容量メモリモジュール設計技術の開発: 50億円

- (e1) 端末通信機能構成技術の開発: 35億円

- (e2) 端末向け低消費電力コンピューティング技術の開発: 40億円

- (f1) 超分散コンピューティング技術の開発: 150億円×変動率

- (f2) 高機密データ流通技術の開発: 30億円×変動率

- (g1) 量子・スパコン連携プラットフォームの開発: 提案1件当たりの初回ステージゲート審査までの提案時委託費は、原則として200億円以下とする。

### 【変動率の設定方法】

4 < 設定値 : 100%</li>

• 1 < 設定値 ≦ 4: (60 + 10 × 設定値) %

設定値 ≤ 1 : 0%

② 先端半導体製造技術の開発(助成(助成率1/2)、委託)

提案1件当たりの助成費及び委託費、開発期間毎の助成費及び委託費は、原則として以下を上限とする。ただし、波及効果が大きく一体として研究を行う必要があるが、上記の予算規模では十分な研究開発が行えない場合であり、採択審査段階における外部有識者の審査で認められた場合には、必要額を十分に精査した上で、上記を超える予算規模を認めるものとする。

なお、これらの上限は、実施者の採択後、研究開発の進捗や成果、情勢変化を踏まえた 最新の事業化見通しとこれに向けた取組状況等に係る総合的な評価を踏まえ、ステージ ゲート審査等で外部有識者に認められたテーマの加速(予算の増額)をする場合は、この 限りではない。

加えて、開発予算では、開発に当たり必要となる製造装置群(評価・測定装置等を含む) やガス・薬液等の供給設備、排気設備等のユーティリティ設備を導入したクリーンルーム 環境を必要に応じて国内に整備することができるものとする。

- (a) 先端半導体の前工程技術 (More Moore 技術) の開発 提案1件当たりの提案時助成費は、原則として380億円以下とする。

- (b) 先端半導体の後工程技術 (More than Moore 技術) の開発

- (b1) 高性能コンピューティング向け実装技術 提案1件当たりの提案時助成費は、原則として250億円以下とする。

- (b2) エッジコンピューティング向け実装技術 提案1件当たりの提案時助成費は、原則として50億円以下とする。

- (b3) 実装共通基盤技術

(開発対象技術全てを開発する大規模な提案の場合)

提案1件当たりの提案時助成費は、原則として50億円以下とする。 (開発対象技術のうち1つの技術を開発する場合)

提案1件当たりの提案時助成費は、原則として10億円以下とする。

- (c) 露光周辺技術開発

- (c1) EUV 露光装置向けペリクル技術開発 提案1件当たりの提案時助成費は、原則として40億円以下とする。

- (c2) EUV 露光装置向け次世代フォトレジスト技術開発 提案1件当たりの提案時助成費は、原則として30億円以下とする。

- (d) 国際連携による先端半導体製造技術開発

- (d1) 高集積最先端ロジック半導体の製造技術開発 提案1件当たりの初回ステージゲート審査までの提案時委託費は、原則として 700億円以下とする。

外部有識者によるステージゲート審査の結果、2,600億円を増額し、2回目のステージゲート審査までの委託費総額は3,300億円以下とする。

- (d2) 光電融合による分散型メモリセントリックコンピューティング技術開発 提案1件当たりの初回ステージゲート審査までの提案時委託費は、原則として 220億円以下とする。

- (e) 次世代メモリ技術開発

- (e1) 次世代広帯域・低消費電力HBMの製造技術開発 提案1件当たりの提案時助成費は、原則として250億円以下とする。

- ③先導研究(委託、助成(助成率1/2)) 提案1件当たりの提案時委託費及び助成費は、原則として3億円以下とする。

### (2) 採択方法

公募要領に合致する提案を対象に、一次採択審査及び二次採択審査を行った上で、実施者を採択する(本事業を実施する上で必要となる調査等に関する実施者を採択する際には、一次採択審査を行わない。)。一次採択審査は、施策目的との合致性等の観点から、商務情報政策局が行う。一次採択審査通過者に対する二次採択審査は、技術面等の観点(技術の実用化の観点を含む)から、NEDOもしくはNEDOが設置する採択審査委員会が行う。NEDOは、二次採択審査の結果を商務情報政策局に対して報告し、商務情報政策局から承認を受けた後、実施者の採択を速やかに決定し、実施者に対して採択決定通知を発出する。なお、採択に当たっては必要な条件(研究開発項目③「先導研究(委託、助成)」として採択すること等)を付して条件付き採択とする場合がある。

採択審査は非公開であり、外部からの審査経過に関する問合せには応じないこととする。 採択審査に当たって必要な場合には、提案者に対して、商務情報政策局またはNEDOから ヒアリング等を実施する。

公募の締切から採択決定までの期間は、原則として55日以内とする。採択結果については、NEDOがホームページ等を通じて公表する。

#### 6. 実施体制等

### (1) 役割分担

本事業では、商務情報政策局が研究開発の方針決定等、NEDOが研究開発の進捗状況管理等、公募により採択された実施者が研究開発の実施を担う。

商務情報政策局は、本事業を実施する上での重要な方針(研究開発計画、予算配分、委託・助成の別 等)を決定するとともに、研究開発の進捗や技術動向・市場動向等を踏まえ、必要に応じて、研究開発計画等の見直しを行う。また、事業を円滑に進める観点から、必要に応じてNEDOや実施者に対して指示を行う。

NEDOは、本事業を実施するための基金の設置及び当該基金の適切な管理、公募による

実施者の採択、契約締結・助成金交付を行う。また、本事業の研究開発成果の最大化に向けて、実施者による研究開発の進捗状況管理(実施者による研究開発の進捗状況の把握、実施者に対する必要な指示、各種委員会の開催を通じた評価等)や調査等、また、当該成果の普及に向けた広報等を実施する。

研究開発の実施者は、実用化や社会実装を見据えて研究開発に取り組む。当該実施者は、企業や研究機関等(以下、「団体」)のうち、原則として日本国内に研究開発拠点を有するものを対象とし、単独又は複数で研究開発を実施する。ただし、研究開発を実施する上で、国外の団体の特別な研究開発能力や研究施設等を活用する必要がある場合には、当該団体と連携して研究開発に取り組むことができる。

なお、本事業の実施に関する詳細(公募の進め方、採択審査における審査基準、各種委員会やステージゲート審査等を含む研究開発の進捗状況管理の方法、調査・広報の内容、研究開発費返還制度における費用対効果指標の達成状況の評価方法 等)については、NEDOが商務情報政策局に相談の上、商務情報政策局が決定する。

また、NEDOは提案者及び実施者から受領した資料や営業秘密に係る情報(事業化計画や売上高等)については、組織内の実施体制を適切に構築した上、機密保持のために十分な措置を講ずるものとする。

### (2) 研究開発の進捗把握・管理

NEDOは、研究開発の実施者と緊密に連携し、各開発テーマの研究開発の進捗状況を把握する。また、外部有識者等で構成する委員会を組織し、定期的(年1回程度)に評価を実施し、開発目標の達成見通しを常に把握するとともに、予算の必要性や実施体制の妥当性を精査する。また、各開発テーマの研究開発の進捗状況、開発目標の達成見通し、成果の事業化の見通し等について、定期的に商務情報政策局に報告し、商務情報政策局からの指示に従い、必要に応じて、開発テーマ毎の予算配分の増加や縮小、実施体制の再構築等を行う。

また、研究開発を効率的かつ効果的に実施するため、商務情報政策局からの指示に従い、各開発テーマの研究開発開始から終了までの中間時点(研究開発項目①:研究開発開始時点から1.5年後(ただし(f1)および(f2)については、2.5年後)、研究開発項目②:研究開発開始時点から2.5年後、研究開発項目③:研究開発開始時点から1年後~1.5年後)を目途に、ステージゲート審査を実施する。なお、採択審査段階等における外部有識者の審査で認められた場合には、ステージゲート審査時期の目途よりも前に実施することも可能とする。

当該審査を通過しなかった開発テーマについては、審査後3か月を目途に研究開発を終了する。当該審査を通過した開発テーマについても、審査結果を踏まえ、必要に応じ、研究開発の加速、縮小、実施体制の変更(例:再構築、統合 等)、実施形態の変更(研究開発項目①から③への変更 等)等を行う。なお、当該審査等の委員会での評価に当たっては、研究開発の進捗や成果、情勢変化を踏まえた最新の事業化見通しとこれに向けた取組状況、費用対効果等に係る総合的な評価を行う。

#### (3) 調査・広報

NEDOは、本事業で取り組む技術分野について、国内外の技術動向、政策動向、市場動向等について調査(本事業において委託事業として実施)を行い、研究開発成果の最大化に向けた方策を分析・検討する。また、NEDOは、シンポジウムの開催等を通じて、本事業の研究開発成果の普及に向けた広報に取り組む。

#### 7. その他

### (1) 研究開発成果の取り扱い

実施者は、研究成果の普及に努め、NEDOは、実施者による研究成果の広範な普及の促

進に努める。

本事業の成果に依る知的財産や研究開発データの取り扱いについては、経済産業省が定める「委託研究開発における知的財産マネジメントに関する運用ガイドライン」及びその別冊である「委託研究開発におけるデータマネジメントに関する運用ガイドライン」に従うことを原則する。NEDOが委託を行って実施する開発テーマについては、開発テーマ又は開発テーマを構成する研究項目ごとに知財委員会を委託先に設置し、知財委員会において、研究開発成果に関する論文発表及び特許等(以下、「知財権」)の出願・維持等の方針決定等のほか、必要に応じて、知財権の実施許諾に関する調整等がなされるよう、NEDOが助言・指導を行う。

### (2) 実施期間

本事業を終了する時期は未定とし、5年に1回、見直しを行う。

### (3) 中間評価·事後評価

中間評価は、本事業開始後、3年程度おきに経済産業省が行う。 事後評価は、本事業の終了後に経済産業省が行う。

### (4) 研究開発計画の見直し

商務情報政策局は、研究開発の進捗や技術動向・市場動向等を踏まえ、必要に応じて、研究開発計画(研究開発項目、研究開発期間、開発目標、実施体制 等)を見直す。

<研究開発計画の策定・見直しの履歴>

| • | 2 | O | 2 | 0年  | 4  | 月 | 1 | 3 | 日 | 策  | 定 |

|---|---|---|---|-----|----|---|---|---|---|----|---|

| • | 4 | U | 4 | 0 + | 4, | 刀 | T | J | Н | W) | Œ |

•2020年8月6日 改定(先導研究の開発テーマの設定)

•2021年1月7日 改定(先端半導体製造技術の開発テーマの設定)

• 2021年2月4日 改定(ポスト5G情報通信システムの開発、先端半導体製造技術の開発、先導研究の開発テーマの設定)

•2021年3月9日 改定(収益納付額の計算方法の追記)

2021年6月30日 改定(ポスト5G情報通信システムの開発テーマの設定)

• 2022年4月22日 改定(ポスト5G情報通信システムの開発、先端半導体製造 技術の開発テーマの設定)

•2022年8月31日 改定(先端半導体製造技術の開発テーマの設定)

●2022年10月28日 改定(先端半導体製造技術の開発テーマの設定)

• 2 0 2 3 年 1 月 2 0 日 改定 (ポスト 5 G情報通信システムの開発テーマの設定)

•2023年3月27日 改定(先端半導体製造技術の開発(d1)の予算規模の変更)

◆2023年6月19日 改定(ポスト5G情報通信システムの開発テーマの設定)

•2023年6月28日 改定(アウトプット目標の変更、先端半導体製造技術の開発テ

ーマの設定、「GX」の開発テーマの追記)

• 2023年7月11日 改定(ポスト5G情報通信システムの開発テーマの設定)

以上

### 収益納付額の計算方法

収益納付額=  $(A-B) \times C/D - E$

- A:収益額(補助事業に係る製品・部品等における営業損益等(売上高ー製造原価ー販売管理費等)の各年度の累計)

- B:控除額(補助対象経費)

- C:補助金確定額

- D:補助事業に係る支出額(補助事業に要した経費と補助事業終了後に追加的に要した経費 の合計)

- E:納付額(前年度までの収益納付を行っている場合の当該納付額)

- (注1) 相当の収益が生じた場合とは、収益 [A] -控除額 [B] > 0 となる場合をいう。

- (注2) 収益 [A] の計算にあたって、製品・サービス等に対する補助事業の寄与が一部である場合は、公正妥当な寄与率を収益に乗じた額を用いる。例えば、寄与率には当該収益を得るために要した投資総額(当該製品・サービス等の生産・実現に寄与した産業財産権やノウハウ等を生み出すために当該時点までに要した開発等経費を含む)に当該補助事業に要した経費総額が占める割合を用いる。

- (注3) 販売管理費等には、必要に応じ、補助事業に係る借入金の利息等金融費用を含むことができる(当該補助金に係る分として厳格に区分経理できる場合に限る)

- (注4) 補助事業が複数年度に渡る場合は、補助対象経費、補助金確定額、補助事業に要した経費は、各年度の累計とする。

- (注5)中小企業等において、補助事業に係る製品・部品等についての区分経理が難しい場合は、収益「A」は企業全体の収益ベースに算出したみなし額を用いることも認める。