ポスト5G情報通信システム基盤強化研究開発事業

研究開発計画

令和7年12月4日

イノベーション・環境局

製造産業局

商務情報政策局

## 目次

|                                   |    |

|-----------------------------------|----|

| 1. 目的・概要 .....                    | 2  |

| 2. 目標 .....                       | 2  |

| 3. 研究開発内容 .....                   | 2  |

| (1) 研究開発項目 .....                  | 2  |

| (2) 研究開発期間 .....                  | 51 |

| 4. 成果最大化に向けた仕組み .....             | 51 |

| (1) ユーザーのニーズ把握 .....              | 52 |

| (2) 研究開発期間中の製品化 .....             | 52 |

| (3) 民間企業等による市場展開を促す仕組み .....      | 52 |

| (4) 民間企業等による負担 .....              | 54 |

| (5) 「GX」の開発テーマにおける社会実装のコミット ..... | 54 |

| 5. 実施者の採択 .....                   | 55 |

| (1) 予算規模 .....                    | 55 |

| (2) 採択方法 .....                    | 59 |

| 6. 実施体制等 .....                    | 59 |

| (1) 役割分担 .....                    | 59 |

| (2) 研究開発の進捗把握・管理 .....            | 60 |

| (3) 調査・広報 .....                   | 61 |

| 7. その他 .....                      | 61 |

| (1) 研究開発成果の取り扱い .....             | 61 |

| (2) 実施期間 .....                    | 61 |

| (3) 中間評価・事後評価 .....               | 61 |

| (4) 研究開発計画の見直し .....              | 61 |

| (別紙1) 収益納付額の計算方法 .....            | 62 |

| (別紙2) 調査テーマ一覧 .....               | 63 |

| (別紙3) 技術情報流出防止への取組 .....          | 69 |

## 1. 目的・概要

第4世代移動通信システム（4G）と比べてより高度な第5世代移動通信システム（5G）は、現在各国で商用サービスが始まりつつあるが、更に超低遅延や多数同時接続といった機能が強化された5G（以下、「ポスト5G」）は、今後、工場や自動車といった多様な産業用途への活用が見込まれており、我が国の競争力の核となり得る技術と期待される。

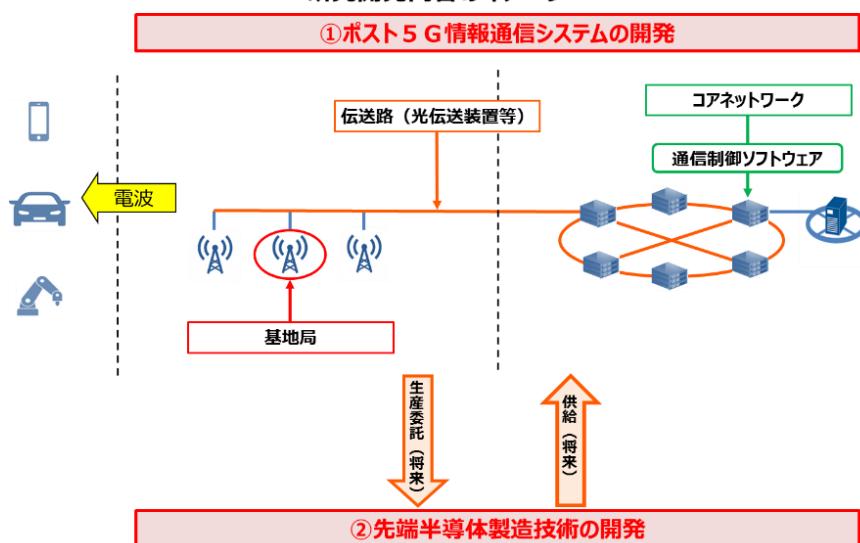

本事業では、ポスト5Gに対応した情報通信システム（以下、「ポスト5G情報通信システム」）の中核となる技術を開発することで、我が国のポスト5G情報通信システムの開発・製造基盤強化及びデジタル社会と脱炭素化の両立の実現を目指す。

具体的には、ポスト5G情報通信システムや当該システムで用いられる半導体等の関連技術を開発するとともに、ポスト5Gで必要となる先端的な半導体を将来的に国内で製造できる技術を確保するため、先端半導体の製造技術の開発に取り組む。加えて、これらを推進する上で重要な人材育成に取り組む。

## 2. 目標

本研究開発事業全体の目標として、以下の通り、アウトプット目標及びアウトカム目標を定める。なお、研究開発内容に変更が生じた場合には、必要に応じて、本目標を見直す。

### ＜アウトプット目標＞

#### ・中間目標

テーマごとに設定した最終目標の達成に向けた中間的マイルストーンを達成すること。

※研究開発項目①のテーマ「(g3) 競争力ある生成AI基盤モデルの開発(GENIAC)（助成）」については、事業期間が短期間であることから、④人材育成については研究開発自体の項目ではないことから、中間目標の対象外とする。

#### ・最終目標

ポスト5G情報通信システムを構成する各要素及び、ポスト5G情報通信システムに必要となる先端半導体の製造技術や材料技術等について、有識者の意見に基づき開発テーマごとに設定した目標を達成したテーマの割合（※）：80%以上

※開発テーマごとに設定した目標を達成したテーマ数／当該時点までに研究開発を完了したテーマ数（先導研究、人材育成は除く）

### ＜アウトカム目標＞

本事業で開発した技術の実用化率（※）：50%以上（各採択テーマ終了後概ね3年時点）

※開発した技術が実用化に至ったテーマ数／先導研究及び人材育成以外の採択テーマ数

## 3. 研究開発内容

### （1）研究開発項目

以下①～③の項目について、研究開発を実施する。研究開発項目は、技術動向や市場動向等を踏まえ、必要に応じて柔軟に追加・変更する。

また、研究開発項目毎もしくは個々の開発テーマ毎に開発目標を設定し、研究開発の進捗状況管理の一環として、当該目標の達成状況を国立研究開発法人新エネルギー・産業技術総合開発機構（NEDO）が評価する。必要な場合には、開発目標の見直しを行う。なお、【GX】は、対応する開発テーマの類型が「グリーントランسفォーメーション」（以下「GX」）であることを表す。

加えて、④の項目で、これらの推進に重要な人材育成を実施する。

## ①ポスト5G情報通信システムの開発（委託、助成）

情報通信ネットワーク全体やそれを構成する各要素（コアネットワーク、伝送路、基地局、モバイルエッジコンピューティング（M E C）、端末）、情報通信システムにおける情報処理を加速する計算基盤について、以下の技術開発に取り組む。なお、【システム技術開発】は、対応する開発テーマの類型が「システム技術開発」であることを表す。また、開発テーマが助成事業である場合は（助成）で表し、（助成）表記がない開発テーマは委託事業であることを表す。

### （a）コアネットワーク

ポスト5Gのコアネットワークには、多様なサービスの要求に対応しつつ、膨大なトラフィックを可能な限り省電力かつ低コストで効率的に処理するため、仮想化や計算リソース管理等に関する高度な技術が求められる。また、低遅延や高信頼といった要求に対応するため、将来的には、巨大な単一のデータセンタで処理を行う形から、地理的に分散した複数の計算リソースを活用し、クラウドベースでコアネットワークを実現する形へと形態が大きく変化する可能性がある。このため、多様なサービスの要求に対応する上で適切なシステム構造とすることに留意しつつ、仮想化や計算リソース管理等に関する高度な技術を備えるとともに、クラウドベースでも動作が可能なコアネットワークのソフトウェア技術等を開発する。

具体的な開発テーマは、以下の通りとする。

#### （a1）クラウド型コアの高度化技術の開発【システム技術開発】

##### ＜開発対象＞

- 3GPPの仕様（リリース15～17）に準拠し、クラウド基盤上で動作する5Gコアを実現するソフトウェア技術

##### ＜開発目標＞

- U-planeにおける単位計算リソース当たりのユーザデータの処理性能（※）：研究開発開始時点での普及している製品（クラウド基盤上の動作を前提としているもの）と比較して同等以上

※例えば、「Gbps/CPUコア」で表される処理性能。

- C-planeにおける単位計算リソース当たりの制御信号の処理性能（※）：研究開発開始時点での普及している製品（クラウド基盤上の動作を前提としているもの）と比較して同等以上

※例えば、「TPS/CPUコア」で表される処理性能。TPSは、Transaction Per Secondを表す。

#### （a2）クラウド型ネットワーク統合管理・自動最適化技術の開発【システム技術開発】

##### ＜開発対象＞

- 情報通信ネットワークの機能がクラウド基盤を利用して提供されることを前提として、OSS（Operation Support System）及びMANO（Management and Network Orchestration）に、アプリケーションの要求に応じたネットワークスライスを無線アクセスネットワーク（RAN：Radio Access Network）からコアまでエンドツーエンドで生成・管理する機能や、情報通信ネットワークから収集した情報を基にリアルタイムで品質の監視・劣化予測等を行う機能及び当該予測等に基づきリアルタイムで計算リソースの最適配置を行う機能等を搭載するためのソフトウェア技術

※OSSは、情報通信事業者等による情報通信ネットワークの運用を支援するシステムを表す。

※MANOは、NFV（Network Functions Virtualization）において、NFVI（NFV Infrastructure）、やVNFM（Virtual Network Function）、OSS等に指示を出しながら、ネットワークサービスやそれに必要な計算リソースの統合的な管理・制

御を担うシステムを表す。

※N F Vは、従来は専用装置により提供されていた情報通信ネットワークの機能を汎用サーバによる仮想化基盤上でソフトウェアとして実現する方式を表す。N F V Iは、物理的な計算リソースを仮想化された計算リソースとして扱うための仮想化基盤を表す。V N Fは、N F V I上で動作する仮想化された情報通信ネットワークの機能を表す。

＜開発目標＞

- 5 G情報通信ネットワークの構築及び運用に関する自動化率（※）：研究開発開始時点の自動化率と比較して30%以上向上

※構築及び運用に必要な全作業量（例えば、「工数（人日）」で表される作業量）のうち、自動化可能な作業量の割合を表す。

(b) 伝送路

ポスト5 Gの伝送路には、データ伝送の遅延を短く保つつ、膨大なトライフィックの増加に対応するため、光伝送装置の大幅な性能向上が求められる。また、機能分割された各基地局機能間の信号やM E Cで処理されたデータなど、容量や経路が異なる光信号を柔軟に制御する必要がある。加えて、ビル壁面や街路灯へのアンテナ設置やビル間伝送などにおいて光ファイバ伝送より効率的な無線伝送や、遠隔医療等の産業用途サービスを島しょ部等の条件不利地域でも展開するために効率的に伝送路を構築する技術が必要となる。

このため、伝送路上の光信号を高速で電気信号に変換（及びその逆変換）することが可能な光伝送装置、光伝送装置内においてデジタル信号の高速処理を担うD S P（デジタル・シグナル・プロセッサ）、膨大な情報を高速かつ省電力で書込み・読み出し可能な不揮発性メモリ等に関する技術、M F H（M o b i l e F r o n t H a u l）や基地局～M E Cサーバー間等比較的短距離のイーサネット伝送リンクにおいて利用される超高速光デバイス、大容量固定無線伝送装置、柔軟に経路制御可能な光スイッチ技術、島しょ部等に効率的にM B H（M o b i l e B a c k H a u l）回線を整備する技術を開発する。

具体的な開発テーマは、以下の通りとする。

(b1) 光伝送システムの高速化技術の開発【システム技術開発】

＜開発対象＞

- 1波長当たり最大伝送速度1 T b p s以上の光伝送装置を実現する技術（当該装置を実現するためのデバイス・ソフトウェア等を含む）

- 伝送路運用（伝送品質、伝送リソース、消費電力等）の自動最適化技術

＜開発目標＞

- 光伝送装置における1ポート（1 T b p s以上）の消費電力性能：120 mW/G b p s以下

(b2) 光伝送用D S Pの高速化技術の開発

＜開発対象＞

- デジタルコヒーレント光伝送で用いる最大伝送速度1 T b p s以上のD S Pを実現する技術

＜開発目標＞

- D S Pの消費電力性能（W/b p s）：研究開発開始時点で普及している製品と比較して1/5以下

(b3) 微細化の進展に対応した高速不揮発性メモリ技術の開発

＜開発対象＞

- 5 n m以降のロジック半導体製造プロセスに対応した不揮発性メモリアレイを実現する技術（当該メモリアレイを実現するための素子を含む）

※当該メモリアレイを用いることにより実現可能な新たな光伝送技術についても、必要に応じて、開発対象に含めることが可能。

＜開発目標＞

- ・メモリアレイの1ビット当たり書き込み時間：10n s以下

- ・メモリアレイの1ビット当たり書き込みエネルギー：1f J以下

- ・メモリアレイの書き換え可能回数：10<sup>15</sup>回以上

(b4) 固定無線伝送システム大容量化技術の開発【システム技術開発】

＜開発対象＞

- ・最大伝送速度25Gbps以上のミリ波帯固定無線伝送装置を実現する技術（当該装置を実現するためのデバイス・ソフトウェア等を含む）

＜開発目標＞

- ・伝送速度：25Gbps以上

- ・送信パワー：10dBm以上（25Gbps伝送時に達成すること）

(b5) バス型伝送高度化技術の開発【システム技術開発】

＜開発対象＞

- ・ケーブル分岐機能を備えたバス型伝送トポジにより島しょ部等において効率的に伝送路（基地局～モバイルコア区間のMBH）を構築する技術

- ・給電装置をブランチ部に設置しないバス型伝送システムにおいて、ブランチケーブル長を延伸する技術

- ・トランクからブランチへの給電電力の高出力化を実現する技術

※トランクとはバス型伝送路において共有区間となる幹線部分を指す。

※ブランチとはトランクからケーブル分岐機能により枝分かれする支線部分を指す。

＜開発目標＞

- ・トランクからブランチへの給電電力：400W以上

- ・ブランチ区間長：200km以上

- ・光中継装置の消費電力：研究開発開始時の普及品に対し20%減

(b6) 超高速光リンク技術の開発

＜開発対象＞

- ・超高速イーサネット用光デバイスを実現する技術

＜開発目標＞

- ・変調方式：強度変調

- ・伝送速度：200Gbps／波長以上

- ・ON/OFF比：5dB以上

- ・伝送距離：1km以上

(b7) 光スイッチ高度化技術の開発

＜開発対象＞

- ・フレックスグリッド用光スイッチの光学特性向上、入出力ポート数拡大を実現する技術

＜開発目標＞

- ・挿入損失：8dB以下

- ・周波数分解能：6.25GHz以下

- ・スイッチ規模：1xN型で1x20が4並列以上、MxN型で8x16以上

※MxN型はMが入力ポート数、Nが出力ポート数を表す。1xN型、MxN型の目標値をそれぞれ実現すること。

- ・消費電力：研究開発開始時点の普及品に対しポート当たり50%以上削減

(c) 基地局

ポスト5Gの基地局には、広帯域である高周波数帯の無線リソースを有効利用するため、多数の端末との同時接続を実現する高度なビーム制御が求められるとともに、利用周波数

帶が上がるにつれアンテナ間隔が狭まるため放熱効率の向上が求められる。また、基地局内で膨大な信号を低遅延で処理するため、基地局内部においても高い伝送速度を確保することが求められる。加えて、遠方まで届きにくい高周波数帯の電波の利用により基地局の設置数が増加するため、基地局の無線ユニットやそこで用いられる高周波デバイス等の高出力化・小型化による省電力化、またソフトウェア化の進展によるコスト低減等が求められる。

このため、高度なビーム制御機能を備え、省電力性能等に優れた基地局、基地局のソフトウェア化、基地局に搭載される高出力・小型の高周波デバイスや基地局内部の光配線化等に関する技術、高効率アンプ一体型アレイアンテナ実装技術を開発する。

また、近年、基地局を構成する装置間の接続インターフェイスをオープンにすることにより、複数のベンダーの装置で基地局を構成し、調達の多様化を実現するための取組（O-RAN）が進められており、基地局を構成する一部装置やインテグレーション技術で競争力を有する日本のベンダー・オペレーターが世界シェアを獲得する千載一遇の機会であるが、実際に多様なベンダーの多様な装置間での相互接続性を確保する上では、検証に必要なプロセスやツールが整備されていない等、技術的なハンドルが存在している。このため、装置間の相互接続性の評価・検証等を行うための技術を開発する。加えて、O-RANの国際的な普及拡大にあたっては、各国・オペレーター毎の周波数や利用する通信方式、現地オペレーターが保有する伝送路やコアネットワークとの接続等を考慮した莫大な数のインテグレーション・品質保証が必要となる。そこで、O-RANインテグレーションを抜本的に簡易化する技術を開発する。また、基地局をオペレーター間で共有することによって抜本的な効率化を図る基地局シェアリングが一部の国では必須となっているため、O-RAN基地局のシェアリングを可能とする技術を開発する。

さらに基地局において、今後通信データ量の増大に伴い、消費電力の削減が求められている。O-RAN対応の基地局の優位性を高めるため、O-RAN対応の基地局に対して徹底的な省エネ化のための技術を開発する。併せてローカル5Gの普及拡大を図るため、ローカル5G基地局における省エネ化及び可搬性能向上を目的とした自立ネットワーク稼働が可能なオールインワン構成を達成する技術を開発する。加えて、ポスト5Gで実現が期待されるスマート工場や自動運転等の産業用途サービスでは、高い信頼性や用途に応じた通信品質の保証が必要になる。そこで、RANの安定動作やアプリケーション要求に応じた品質制御に資する技術を開発する。

具体的な開発テーマは、以下の通りとする。

#### (c1) 仮想化基地局制御部の高性能化技術の開発【システム技術開発】

##### ＜開発対象＞

- 3GPPの仕様（リリース15～17）に準拠し、ネットワークスライシングに対応した5G基地局制御部を汎用ハードウェア上で実現するソフトウェア技術

※5G基地局制御部は、「CU（Central Unit）及びDU（Distributed Unit）」を表す。

##### ＜開発目標＞

- 5G基地局制御部に関する単位伝送速度当たりのCAPEX（設備投資コスト）及びOPEX（運用コスト）（円／bps）：研究開発開始時点での普及している製品（専用ハードウェアで機能を実現するもの）と比較して30%以上削減

- 多数同時接続もしくは超低遅延の実現に寄与する5G基地局制御部の中核技術に関する性能：研究開発開始時点での普及している製品（専用ハードウェアで機能を実現するもの）と比較して3倍以上（※）

※例えば、「5G基地局への端末の同時接続数：研究開発開始時点での普及している製品（専用ハードウェアで機能を実現するもの）と比較して3倍」といった形で設定。

#### (c2) 基地局無線部の高性能化技術の開発【システム技術開発】

##### ＜開発対象＞

- 3GPPの仕様（リリース15～17）に準拠し、ビームフォーミング機能を備えた

5 G 基地局無線部を実現する技術（当該装置を実現するためのデバイス・ソフトウェア等を含む）

※ 5 G 基地局無線部は、R A Nの機能を低いレイヤ（L o w e r L a y e r）で分割する場合には「R U（R a d i o U n i t）」、高いレイヤ（H i g h e r L a y e r）で分割する場合には「R U及びD U」を表す。

＜開発目標＞

- 5 G 基地局無線部の単位システム容量当たり装置サイズ（ $m^3 / (b p s / Hz / km^2)$ ）及び消費電力（ $W / (b p s / Hz / km^2)$ ）：

- (A) 研究開発開始時点で普及している製品と比較して装置サイズ1／2以下かつ消費電力同等以下

又は

- (B) 研究開発開始時点で普及している製品と比較して装置サイズ同等以下かつ消費電力70%以下

※システム容量は、単位面積当たり・単位周波数帯域当たりの伝送速度（ $b p s / Hz / km^2$ ）を表す。

- 多数同時接続もしくは超低遅延の実現に寄与する5 G 基地局無線部の中核技術に関する性能：研究開発終了時点で想定される世界最高水準の性能（※）

※例えば、「5 G 基地局への端末の同時接続数：X台／ $km^2$ 」といった形で設定。

(c3) 基地局装置間の相互接続性等の評価・検証技術の開発

＜開発対象＞

- O-R A Nのインターフェイス仕様に準拠した装置について、異なるベンダーの装置間の相互接続性及び当該接続が情報通信ネットワーク全体に与える影響を評価・検証するための技術（評価・検証等に必要なプロセス、ツール、ソフトウェア等を含む）

- 当該技術を開発するための評価・検証環境の設置

※複数のベンダーの装置で基地局を構成する取組を、国際的に普及させる観点から、当該評価・検証環境は、原則として海外に設置し、海外のユーザーのニーズを取り込みながら開発を実施する。

＜開発目標＞

- 海外における評価・検証環境の設置件数：1件以上

- 開発した技術を用いて相互接続性等の評価・検証を行った装置の組み合せ：10通り以上

(c4) 高周波デバイスの高出力・小型化技術の開発

＜開発対象＞

- 高出力の基地局向け高周波G a Nデバイスの製造に用いる基板の結晶成長技術

- 当該技術を用いて製造する基地局向け高周波G a Nデバイス（S u b-6 G H z帯向けデバイス及びミリ波帯（28 G H z以上）向けデバイス）を実現する技術

※当該デバイスを利用した増幅器や、基地局への当該増幅器の搭載を効率化する上で有効なモジュール化技術等についても、必要に応じて、開発対象に含めることが可能。

＜開発目標＞

- S u b-6 G H z帯向け高周波G a Nデバイスの出力電力密度：25 W／mm以上

- ミリ波帯向け高周波G a Nデバイスの出力電力密度：12 W／mm以上

■継続研究開発（助成）

＜開発対象＞

- c4 で開発した結晶及び素子の信頼性向上に向けた、結晶の高抵抗化技術及び絶縁膜物性に立脚した素子作製技術

- c4 で開発したG a Nデバイスの広帯域増幅器を実現する技術

- 高周波に対応した集積回路の積層化等に伴うピーク温度低減のための放熱技術

＜開発目標＞

- $V_p$  変動量 ( $V_p$ : 閾値電圧) : 20%以内

- 帯域幅 (Sub-6 GHz) : 400 MHz 以上

- 熱抵抗値 : 5. 3 °C/W 以下

(c5) 高温動作可能な光接続技術の開発

＜開発対象＞

- 基地局 (RU) のアレイアンテナシステム内に搭載可能なシリコンフォトニクス光トランシーバを実現する技術

- 当該トランシーバをRUのアレイアンテナシステム内に搭載し、アレイアンテナとその制御回路等を光配線により接続するための実装技術（実装に必要なモジュール化を含む）

※アレイアンテナシステムとは、アンテナアレイとその制御回路等から成るシステムを表す。

＜開発目標＞

- 光トランシーバの消費電力性能 : 4 mW/Gbps 以下

- 光トランシーバの最大伝送速度 : 1 Tbps/cm² 以上

- 光トランシーバが正常動作可能な環境温度 : 100 °C 以上

(c6) 高周波帯アンプ一体型アレイアンテナ実装技術の開発

＜開発対象＞

- ミリ波帯 (40 GHz 以上) で動作しビーム制御が可能なアンプ一体型アレイアンテナモジュールにおいて、高い放熱効率を実現する実装技術の開発

- スモールセルやインドア用途を想定した高効率なアンプを実現する技術の開発

＜開発目標＞

- アレイアンテナ素子数 : 4 x 4 以上

- 熱源 (アンプ) からヒートシンクまでの熱抵抗 : 1. 0 K/W 以下

- 出力パワー : 5 mw/アンテナ素子以上 (40~50 GHz の場合)

※出力パワーは、他の周波数帯の場合はスモールセル・インドア用途で必要と認められる値を設定するものとする

(c7) RAN制御高度化技術の開発【システム技術開発】

＜開発対象＞

- O-RAN標準のRIC (RAN Intelligent Controller) により産業用途アプリケーションに応じたRAN制御を実現する技術

＜開発目標＞

- Non-RT RICのRapp機能もしくはNear-RT RICのXapp機能のいずれか、あるいは両方を用いた、産業アプリケーションに応じたRAN制御の有効性検証：合計2件以上

※有効性検証として、例えばアプリケーションに応じた制御モデル構築と動作検証、アプリケーションに応じたRAN制御とQoE (Quality of Experience) の関係明確化等、産業用途のRIC活用・製品競争力向上に資すると認められるものを実施する。

※有効性検証において少なくとも1件は対象とするアプリケーションで必要な実機を用いたものとする。

- 開発したRappまたはXappまたはその両方が動作するRICと、O-RANのインターフェイス仕様に準拠した基地局装置との相互接続性の評価／検証：異なるベンダーの基地局装置を用いて2通り以上

※評価／検証のうち1通りは自社開発の基地局装置を含めることが可能。また、自社開発品ではない基地局装置を用いた検証が困難な場合は、O-RAN準拠製品を模擬できることが確認されたシミュレータや試験装置等を用いてもよい。

(c8) O-RANインテグレーション基盤技術の開発（助成）

＜開発対象＞

- ・様々な周波数帯、無線・有線区間の通信方式、ハードウェアやソフトウェア等の莫大な組み合わせに対し代表的なパターンとして多くの国・オペレーターで共通利用可能なO-RAN基地局インテグレーションパターンのモデル化技術、および各モデルで共通に利用可能なソフトウェアの開発

- ・O-RAN基地局を構成する個々のコンポーネント、および端末～O-RAN基地局～コアネットワーク～検証サーバー間のエンドツーエンドでの接続検証、解析、改修や品質保証等に関わる検証作業を自動化する技術

＜開発目標＞

- ・PoCモデル作成数：3以上

※グローバル展開において十分な数のオペレーターに適用可能と認められるモデルを作成するものとする。

- ・作成したモデル間でのソフトウェア共用割合：70%以上

※ソフトウェアスタックの共通化やソースコードの流用度等、ソフトウェアの共用としてインテグレーションの効率化に資すると認められるものを設定するものとする。

- ・検証業務の自動化率：50%以上

※作成したPoCモデルおよび共通ソフトウェアを用いるものとする。また、自動化技術の検証に必要な設備等の構築を含んでもよい。

- ・作成したPoCモデルの実環境での検証：3件以上

※都市部・ルーラルといった地域特性や、伝送路やコアネットワーク等のオペレーター設備との接続を考慮した実環境でのデータ取得、および、O-RANを国際的に普及させる観点から、原則として適切な環境を有する海外オペレーターと協力して検証を行うこととし、候補となる海外オペレーターを提案に含むものとする。

(c9) O-RAN基地局シェアリング技術の開発（助成）

＜開発対象＞

- ・O-RAN基地局無線部を複数のオペレーターで共有（シェアリング）する構成において、オペレーターごとに必要な処理能力や周波数等を割り当てる技術

- ・シェアリングしたO-RAN基地局を保守・監視する技術

＜開発目標＞

- ・O-RAN基地局無線部の処理能力や周波数等をオペレーターごとに柔軟に割り当てる可能とする機能を具備すること

※例えば、オペレーターが利用する周波数と周波数帯域幅の組み合わせを、複数オペレーター分収容可能とする機能等、基地局無線部のシェアリングで必要と考えられる機能を開発目標として設定。

- ・2以上のベンダーの基地局無線部、および2以上のベンダーの基地局制御部を用いたマルチベンダー接続により構成したO-RAN基地局において、2以上のオペレーターを収容可能とすること

- ・基地局シェアリング時に保守・監視可能なオペレーター数：2以上

※保守・監視項目は基地局シェアリングの運用にあたって必要と考えられるものを設定するものとする

- ・実環境での検証：2件以上

※都市部・ルーラルといった地域特性や、伝送路やコアネットワーク等のオペレーター設備との接続を考慮した実環境でのデータ取得、および、O-RANを国際的に普及させる観点から、原則として適切な環境を有する海外オペレーターと協力して検証を行うこととし、候補となる海外オペレーターを提案に含むものとする。

- ※実環境での検証のそれぞれについて、1以上は実在のオペレーターを収容するものとし、他の1以上のオペレーター相当として測定器等を用いて複数オペレーターでの基地局シェアリングを模擬してもよいものとする。

(c10) O-RAN基地局の省エネ化技術の開発（助成）

＜開発対象＞

- O-RAN基地局のRU及びDU／CUの各パートにおける省エネ化のための技術

※例として、RUにおける最適Sleep制御など

＜開発目標＞

- 省エネ目標：基地局1サイトあたり15MWh／年以下かつ、研究開発開始時点で普及している製品に比べて50%以上の消費電力削減

※1サイトの定義として、5G基地局の無線部と制御部を含む

(c11) ユーザ品質と省エネの両立を目指した最適通信制御装置の開発（助成）

＜開発対象＞

- 基地局以外の場所（伝送路、コアネットワークなど）から得られるデータを用いて基地局の消費電力を削減するための技術

＜開発目標＞

- 省エネ目標：研究開発終了時点で基地局1サイトあたり5MWh／年以上の削減かつ、本開発システム導入直前の基地局の消費電力に対して10%以上の削減

- ユーザ品質保証目標：端末～サーバー間のエンドツーエンドで50ミリ秒遅延以下かつ、パケットロス目標1%以下

※トラヒックの効率的な制御に対する評価が必要になるため、実際に利用が想定されるMNO又はMVNOとの合同評価を実施すること

(c12) ローカル5G基地局の省エネ化及び可搬性向上に向けた開発（助成）

＜開発対象＞

- 超小型・超軽量・超低消費電力のローカル5G基地局を開発

- RAN、5Gコア、MEC等が一体型となった、自立ネットワーク稼働が可能なオールインワン構成のローカル5G基地局を開発

＜開発目標＞

- 省エネ目標：ローカル5G基地局の消費電力70W以下

- 稼働時間目標：外部電源が得られない状況下においても連続4時間以上稼働

- 可搬性能：人力で容易に持ち運び可能な一体型ローカル5G基地局

※形状／重量など考慮の上、可搬性能の検証を行うこと

(d) MEC

ポスト5Gネットワークの低遅延性・多数同時接続とIoT、AI等の活用により多様な産業活動や国民生活のスマート化が期待されている。また、エッジの端末やセンサーで生み出される大量なデータの蓄積や解析の高度化、AI学習の高性能化の進展が予想されている。しかし、全てのデータをデータセンタ等のクラウドサーバーに送信し、解析、AI学習等をした場合、情報伝送に大量エネルギーとコストがかかり、ネットワーク負荷も多大になるとともに、ポスト5Gの特徴である低遅延性の実現が困難となる。このため、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理を可能とするMECサーバーの普及が求められる。また、低遅延ネットワークを実現するためには、MEC、ネットワーク構成機器、MECと情報通信するエッジデバイス自体の高性能化も求められる。これらMECサーバーやネットワーク機器、エッジデバイスのコンピューティング性能を決定づける重要な役割を担っているのが、大規模・高性能・低消費電力な先端ロジック半導体や、広帯域化で低遅延な大容量メモリモジュールである。

そこで、MECを用いた低遅延処理の実現に向けて、最先端のプロセスノードを適用した大規模先端ロジック半導体の設計技術を開発するとともに、大容量・広帯域なメモリシステムを開発する。

#### (d1) MEC向け大規模先端ロジックチップ設計技術の開発

##### ＜開発対象＞

- ・先端ロジック世代（3nm ノード以降※）のAI処理可能なSoC設計技術、スケーラブルなマルチチップシステム（2・5次元・3次元実装、チップレットパッケージ等のSiP(System in package)モジュール）を実現するための設計技術、システムアーキテクチャ技術、テスティング手法を含むその他の関連する設計環境の開発。

※IEEEのIRDS (International Roadmap for Devices and Systems<sup>TM</sup>) 2020中の「Logic industry “Node Range” labeling (nm)」における「3」以降を意味する。

##### ＜開発目標＞

- ・チップレット※<sup>1</sup>間インターフェース性能 (FOM<sup>※2</sup>) : 3(Tbps/mm)/(pJ/bit)以上

- ・SiPモジュール間の帯域 : 400Gbps 以上

- ・AI処理性能 (チップレット単体) : 20TOPS/W 以上

- ・AI処理性能 (SiPモジュール) : 300TOPS 以上

※1 SiP内の単体チップを意味する。

※2 Figure of Meritの略。1ビットのデータ伝送に必要なエネルギー(pJ/bit)で規格化した1mm当たりのデータ伝送量(Tbps/mm)。FOM値が大きいほど高効率なシステムを意味する。

#### (d2) MECサーバー向け広帯域・大容量メモリモジュール設計技術の開発

##### ＜開発対象＞

- ・ビッグデータ処理向けの低消費電力かつ広帯域、大容量なメモリモジュールの設計技術

##### ＜開発目標＞

- ・メモリモジュールの消費電力 : 40W以下

- ・メモリモジュールの容量 : 2TB以上

- ・メモリモジュールの帯域 : 64GB/s 以上

#### (e) 端末

ポスト5G情報通信システムにおいては、スマート工場や自動運転など用途に応じた多種多様な端末開発が行われることが想定されるため、さまざまな端末に汎用的に利用可能な端末通信チップ・モジュール等を開発する。

また、ポスト5Gネットワークの超低遅延性・多数同時接続とIoT、AI等の活用により、生成・処理されるデータ量が爆発的に増大することが予測されており、これまでのデータ集約・処理型のクラウドサーバーに加えて、端末でデータ処理を行うエッジコンピューティング技術が必要となる。一方、端末では利用可能な電力量が制限されるため、低消費電力でのAI処理が求められる。そこで、端末での効率的なデータ処理を実現するコンピューティング技術の研究開発を行う。

加えて、ポスト5G情報通信システム活用のキラーユースケース端末として期待されるロボットに関して、その導入分野を拡大するためには、ソフトウェア起点で多様なロボットシステムを創出することが重要である。多様な開発者の参入を促しつつも産業応用が可能なソフトウェア品質等を担保できるオープンな開発環境を構築する。

さらに、高速大容量・超低遅延性・多数同時接続といった特性を有するポスト5G情報通信システムをローカル5Gで利用することにより、様々な産業で安定した通信環境の整備や、業務効率化等によるシステムの省エネ化が期待される。一方で、ローカル5G情報通信システムの更なる普及促進に向けては、投資対効果の高いユースケースの創出が依然として課題となっており、省エネ・収益性の両面において優れたユースケースの開拓が求められている。こうした背景を踏まえ、ポスト5G情報通信システムの更なる普及を目指し、産業での省エネ効果・投資対効果のあるローカル5Gのユースケースを開発する。

(e1) 端末通信機能構成技術の開発

＜開発対象＞

- 3GPPの仕様（リリース15～17）に準拠し、超低遅延通信を実現する通信機能部を構成する技術

- 通信設定を柔軟に変更し様々な用途／端末に対応可能な通信制御技術

＜開発目標＞

- 超低遅延の実現に寄与する5G端末通信機能部の中核技術に関する性能：研究開発終了時点で想定される世界最高水準の性能

※例えば、「端末内処理遅延：X msec以下」といった形で設定。

- 通信設定をユーザーが変更できる機能を具備すること

※変更可能な通信設定とは、例えば大容量通信モードと超低遅延通信モードの切り替え、上下の帯域割り当て比率等、産業用途で必要と考えられるものを開発目標として設定。

- 開発した端末通信機能を備えた通信チップ・モジュールと、基地局装置との相互接続性の評価／検証：異なるベンダーの基地局装置を用いて2通り以上

※相互接続性の評価／検証は少なくとも1通りはローカル5G基地局を用いての実施を必須とする。評価／検証のうち1通りは、接続性評価／検証に必要な機能を備えたシミュレータや試験装置等を用いてもよい。

(e2) 端末向け低消費電力コンピューティング技術の開発

＜開発対象＞

- 端末でのAI処理を想定した低消費電力コンピューティング技術※1※2

※1 半導体関連技術を利用した低消費電力化技術であること。また、AIチップ単独の研究開発による低消費電力化の技術は対象外とする。

※2 ロジック及びメモリ等を搭載したモジュールを試作し、動作実証をすること。

＜開発目標＞

- 端末でのAI処理※1における、従来技術※2と比較した消費電力の削減※3割合：50%以上

※1 実施者が提案時に端末でのAI処理のユースケースを設定し、複数のモデルで検証すること。

※2 研究開発開始時点で普及している技術。

※3 半導体の微細化等による削減は除く。

(e3) ロボティクス分野におけるソフトウェア開発基盤構築（委託、助成）

ロボットは、ポスト5G情報通信システム活用のキラーユースケース端末として期待されるところ、現状において導入分野や用途が限定的である。導入が進んでいない産業分野においては、既に導入が進んでいる自動車や電機製造と比べて、多品種少量生産やロボット周辺の環境が不安定といった、ロボット化の難易度が高いケースが多い。また、操作者のロボット活用に係る熟練度も踏まえると、円滑にロボットを運用できるまでに相当の期間を要する点等の課題もある。こうした中で、ロボットの導入を拡大し、新市場を加速的に創出していく上では、ソフトウェア起点で多様なロボットシステムを創出することが重要となる。従来型のロボットシステムにおいては、システムの信頼性は高いものの、ソフトウェアのプログラミング言語が各々のハードウェア毎に異なる等、新規の開発者が参入しづらく、汎用性や拡張性が求められる産業分野に対応できるロボットシステムが生まれにくい環境にある。

本開発テーマでは、ロボティクス分野において、スタートアップ等の多様な開発者の参入を促し、多彩なロボットシステムを創出することを可能とするソフトウェア開発基盤の構築に取り組む。具体的には、オープンかつ共通言語でのソフトウェアを活用しつつ、産業用途で活用可能なソフトウェア品質であることを検証・スクリーニング機能により担保する基盤技術を開発するとともに、それら技術をソフトウェアやハードウェアの流通基盤に統合することで、ロボティクス分野におけるソフトウェア開発基盤を実装させる。これ

により、人手不足解消や生産性向上に資するとともに、ポスト5G情報通信システムの活用拡大を通じたデジタル社会の実現につなげる。本事業で開発する基盤技術は、ロボティクス分野における多様なプレイヤーが共通することでその価値を最大限に創出することができる公共財的な性質を持つため、委託事業として実施する必要がある。

以下、(e3-1)～(e3-3)の実施においては、事業者の合議体を設置し、経済産業省やNEDO等も含めて議論した上で(e3)全体の開発方針を決定し、各開発テーマが密に連携しながら取り組むこととする。なお、ソフトウェア開発基盤のミドルウェアとして、Robot Operating System 2 (ROS2)の活用を推奨する。

#### (e3-1) ソフトウェア等検証基盤技術の開発（委託）

##### ＜開発対象＞

- ・ミドルウェア及びモジュール化されたソフトウェア・ハードウェアを活用したロボットシステムの基本アーキテクチャ<sup>※1</sup>及び当該アーキテクチャを前提とした際のソフトウェア品質を自動的に検証・スクリーニングするエコシステム<sup>※2</sup>の全体設計に係る技術

※1 モジュール間インターフェースやユーザーインターフェースの設計等を含む。また、ロボット向けのAI技術との親和性も考慮した設計とすることに加えて、大容量・低遅延・多接続通信を必要とする際の端末間連携（ローカル5Gの活用等）を念頭とした設計とする（これらの技術を前提とした際の課題や解決アプローチの提案を含む）こと。

※2 ロボットソフトウェア流通基盤への統合のあり方を含む。

- ・オープンソース活用も念頭においていたソフトウェアモジュール及びそれらを組み合わせたサブシステムにおける品質・セキュリティ・安全性・ライセンス管理の自動検証・スクリーニングを可能とする技術

※検証・スクリーニングの指針となる基準の開発を含む。また、開発過程においては、特定のユースケース（具体的なユーザーニーズがあり、同一業界内または業界横断で波及効果が期待されるもの）を念頭に置いた上で検証・スクリーニングの基準となるレファレンスマジュールやレファレンスサブシステム（以下、レファレンスシステムと言う）を開発することとする。当該レファレンスシステムは、(e3-2)で開発するロボットソフトウェア流通基盤に提供する。

- ・ソフトウェアモジュールの開発の促進、システムインテグレーション及びシステムオペレーションの効率化に資するための各種ツール（開発支援ツール、品質管理ツール、運用支援ツール）に係る以下の技術

- ・モジュールやサブシステムを用いてシステムインテグレーションを効率化する技術

- ・日々変化する環境下においてロボットシステム（特に移動系ロボットシステム）同士またはロボットシステムと工程管理システム等との通信を安定化する技術

- ・ロボットシステムの遠隔操作や遠隔保守、ソフトウェアの自動アップデートを可能にする技術 等

##### ＜開発目標＞

- ・開発したソフトウェア等検証基盤技術や各種ツール等に関して、現行の一般的なロボット開発工程に比して効率性が十分に向上することを検証

※提案者にて、「現行比でN%以上の効率性向上を達成できる」といった指標や目標値を提案時に設定すること。

##### ＜応募条件＞

- ・開発成果について、ロボットシステムインテグレーター等が広く参照・活用することができるドキュメントを用意すること。

- ・オープンソースソフトウェアのコミュニティとの連携を行うことができる体制であること。

- ・可能な範囲でオープンイノベーションを推進するとともに、成果報告会やワークショップの開催等を行うこと。

- ・開発したソフトウェア・ツール等について、事業終了後5年間は保守サポートできる

体制であること。

(e3-2) ロボットソフトウェア流通基盤技術の開発（委託）

＜開発対象＞

- ロボットソフトウェア流通基盤の課金手法・製品評価基準・公開基準に係る技術

- (e3-1) で開発したソフトウェア等検証基盤技術や各種ツール等のロボットソフトウェア流通基盤への統合に係る技術

＜開発目標＞

- 開発したロボットソフトウェア流通基盤技術が国際的に比較して十分な優位性を有することを検証

※提案者にて、「現行比で N% 以上の性能を達成できる」といった指標や目標値を提案時に設定すること。

＜応募条件＞

- (e3-1) で開発したロボットソフトウェア流通基盤への統合のあり方を含むエコシステムの全体設計に準拠すること。

- オープンソースソフトウェアのコミュニティとの連携を行うことができる体制であること。

- 可能な範囲でオープンイノベーションを推進するとともに、成果報告会やワークショップの開催等を行うこと。

- 開発したソフトウェア・ツール等について、事業終了後 5 年間は保守サポートできる体制であること。

- 事業成果の最大化のため、必要に応じ、本事業で構築するソフトウェア開発基盤はユーザー企業等にも利用してもらい、そのフィードバックを得て更なる改善を行うこと。

(e3-3) ロボットソフトウェア流通基盤技術の開発（助成）

＜開発対象＞

- (e3-2) で開発したロボットソフトウェア流通基盤の実証

＜開発目標＞

- 本流通基盤が、技術的・経済的に有効であることを検証

※技術的・経済的な有効性を検証する上でのユースケース数やユーザー数といった目標値を提案時に示すこと。

＜応募条件＞

- (e3-1) で開発したロボットソフトウェア流通基盤への統合のあり方を含むエコシステムの全体設計に準拠すること。

- オープンソースソフトウェアのコミュニティとの連携を行うことができる体制であること。

- 可能な範囲でオープンイノベーションを推進するとともに、成果報告会やワークショップの開催等を行うこと。

- 開発したソフトウェア・ツール等について、事業終了後 5 年間は保守サポートできる体制であること。

- 事業成果の最大化のため、必要に応じ、本事業で構築するソフトウェア開発基盤はユーザー企業等にも利用してもらい、そのフィードバックを得て更なる改善を行うこと。

(e4) 省エネに資するローカル 5 G の革新的なユースケース創出事業（助成）

＜開発対象＞

- 省エネに資するローカル 5 G を使用する革新的なユースケース開発

※ (e3)の研究開発対象は除く（本事業への公募不可）

＜開発目標＞

- 開発したローカル5Gユースケースのローカル5G親和性、省エネ効果、経済性および事業性があることを検証

※提案者にて、以下の各項目に対して目標を提案時に設定すること。

- ローカル5G親和性目標：提案するユースケースの環境・技術要件としてローカル5Gを必要とすることを提案時に説明し、本事業で検証すること。

- 経済性目標：システム全体の導入の想定コストおよび、「本ユースケースを○○に適用する事により、投資収益率がXを超える」といった目標を提案時に示し、本事業で想定コストおよび経済性目標を検証すること。

※投資収益率として、5年程度の使用で得られる利益（省エネ効果や省人効果を含む）を同期間内の総コストで除したものを使用する。

- 事業性目標：ユースケースが対象とする市場の国内外での規模を提案時に示し、提案者がその市場にリーチしてユースケースが市場に適合することを本事業で検証すること。

- 省エネ目標：「本ユースケースを○○に適用する事により、従来システムと比較して使用エネルギーのN%以上の削減が達成可能」といった目標を提案時に設定し、本事業で検証すること。

#### ＜応募条件＞

技術的優位性の説明：適用するサービスやアプリケーションが、開発するユースケースに対して他の手法よりも優れている点を提案時に示すこと。また、ユースケースの導入に必要な研究開発要素およびその解決可能性を説明すること。

※ローカル5G以外の通信手段を組み合わせたユースケースを公募対象から排除するものではない

#### ＜特記事項＞

- 本研究開発テーマにおいては、ユースケースの開発および検証の計画を行う計画フェーズと特定の事業者でユースケースの検証を行う実証フェーズの二つのフェーズに分けて事業を行う。これらのフェーズの移行に際しては、ステージゲート審査を実施することとし、審査の際に、実証フェーズの取り組み内容および費用について審査を行う。このステージゲート審査は事業開始後、9ヶ月経過時を目安に行われる。

- ステージゲート審査時に、応募事業者はユースケース導入事業者の MoU または LoI またはそれに類する証跡（応募事業者の社内利用の方針書類などを想定）を用意すること。

- 事業終了時に検証結果を整理し、当初目標との差分とその要因分析を確実に行うこと。

#### (f) 超分散コンピューティング

ポスト5Gの特徴である低遅延性の実現のためには、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理が求められている。他方、現状ではネットワークを介したデータ処理の多くは、特定の場所に集中した巨大なデータセンタで行われており、現在の集中型を前提としたデータ処理技術では低遅延性の実現が困難となる。低遅延ネットワークを実現するためには、データセンタやMEC、ネットワーク構成機器、エッジデバイスなど、地理的に分散した計算資源を最適に活用してデータ処理を行うことが求められる。また、ポスト5Gによる広帯域・多数同時接続の結果、より多数のステークホルダーが大量のデータを保有することが想定される中、こうしたデータをステークホルダー間で円滑・安全に利活用する仕組みや技術も求められている。

このため、地理的に分散したデータセンタからコアネットワーク、伝送路、基地局、MECに至るまで、全体を仮想的な一つのシステム（以下、「超分散コンピューティング環境」という。）と見なして、地理的条件や動的な処理負荷も踏まえて処理需要をデータ処理拠点に割り振り、低遅延性などの制約を満たしつつ最適に実行するアプリケーション実行技術や、複数の計算資源やステークホルダー間での円滑で安全なデータ利活用を実現するデータ利活用技術、これらを統合しシステム化するシステム統合技術を開発する。加えて、超

分散コンピューティング環境において、特にプライバシーの保護や機密性を要するデータ処理を可能にするデータ流通技術を開発する。

さらに、超分散コンピューティング環境の整備により、データ処理だけではなく RAN などの通信処理もデータセンタを含めた様々な環境で分散実行されることが期待される。また、基地局では通信処理の増減に合わせて AI 学習・推論等のデータ処理を実行し、通信処理も AI を活用することが期待される。このような期待に応えるためには、基地局の仮想化技術を用いて、地理的に分散した多様な環境で通信処理とデータ処理を同時に効率化する技術が必要となる。それに加え、基地局に AI 処理を担う計算資源を配置する場合、設置面積や電力容量の制約、温度変動などの課題が顕在化する。これらの制約に対応するため、動作温度範囲の拡大や装置小型化を可能にする高効率冷却技術、ハードウェアを考慮した負荷低減策、効率改善およびセキュリティ対策も必要となる。これらの必要性を満たし、ソフトウェア・ハードウェアの両面で最適化を実現する技術を開発する。

#### (f1) 超分散コンピューティング技術の開発【システム技術開発】

##### ＜開発対象＞

- 超分散コンピューティング環境におけるアプリケーション実行技術

※地理的に分散した計算資源の状態把握・制御を担う資源管理技術、応答時間や消費電力等の制約に応じて最適に複数アプリを配置・実行可能にする最適化実行技術、ユーザーの要求やイベントの発生を起点に一定の時間内に処理結果を応答する低遅延実行を可能にする低遅延実行技術、アプリの開発・導入を簡便化するフレームワーク技術など。

- 超分散コンピューティング環境におけるデータ利活用技術

※地理的に分散した計算資源で取得・管理される膨大なデータを利活用するためのデータ基盤技術およびデータ処理効率化技術、動的なアクセス制御・データ漏洩等に対する包括的な防御・データ取得から利用までのトレーサビリティを実現するセキュリティ基盤技術など。

- 超分散コンピューティング環境を実現するシステム統合技術

※アプリケーション実行技術およびデータ利活用技術を統合したシステム化技術、サービスモデル設計・検証など。

##### ＜開発目標＞

- ポスト 5G で実現が期待される産業用途の実応用サービスを用いた評価／検証：2 件以上

※うち 1 件はポスト 5G の特徴である低遅延性を活用した実応用サービスでの実施、1 件は超分散コンピューティング環境の特徴である地理的に分散した計算資源を活用した実応用サービスでの実施、を必須とする。

- 研究開発終了時点で想定される規模の超分散コンピューティング環境において、開発した超分散コンピューティング技術の有効性を検証

※例えば、管理者が異なる国内 10箇所以上のデータセンタと 5G ネットワークに接続された N 台以上の 5G 端末等から構成される規模の環境において、アプリに応じた遅延制約を満たす実行やデータ処理性能等を検証。ただし端末数 N は、世界の IoT 端末数の研究開発終了時点での予測値等から定めることとし、有効性検証にあたってはシミュレーションなどによる外挿を認める。

実施に際しては、事業成果の最大化のため、プラットフォーム事業者を実施体制に加えるとともに、本事業と並行して開発した成果の積極的な社会実装を推進できる体制をとることとする。また、データセンタ事業者、通信事業者、学術機関等との共同開発やその他の連携を推進する等、可能な範囲でオープンイノベーションを推進するとともに、必要に応じ、本事業で構築するパイロットプラットフォーム等の活用による評価・検証、ユーザー企業・機関との連携、国際連携の推進、オープンアーキテクチャ化・API 等の標準化の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。また、必要に応じて隨時、研究開発項目① (f2) とも連携を行う。

(f2) 高機密データ流通技術の開発【システム技術開発】

＜開発対象＞

- ・超分散コンピューティング環境におけるデータおよびアルゴリズムの秘匿化流通・実行技術

※データおよびアルゴリズムの提供者、利用者、プラットフォーム事業者間でデータやアルゴリズムの機密性を担保したまま処理を行う秘匿化実行技術など。

- ・超分散コンピューティング環境におけるデータおよびアルゴリズムの可搬性技術

※計算資源の物理的な配置や秘匿化処理の有無等によらず、透過的にアルゴリズムの実行やデータアクセスを可能にする可搬実行技術など。

＜開発目標＞

- ・ポスト5Gで実現が期待されるカーボントレースや電力データ流通・制御など横串の社会課題解決を見据えた実応用サービスを用いた評価／検証：2件以上

※うち1件は地理的に分散した計算資源を活用したサービスでの実施、を必須とする。

- ・超分散コンピューティング環境における実応用サービスに即して、開発した高機密データ流通技術の有効性を検証

※例えば、実応用サービスに即して「秒間N万レコード以上の秘匿化データ処理性能を、通常のデータ処理と同等程度の計算資源で達成」といった形で設定。

実施に際しては、事業成果の最大化のため、プラットフォーム事業者を実施体制に加えるとともに、本事業と並行して開発した成果の積極的な社会実装を推進できる体制をとることとする。また、可能な範囲でオープンノベーション等の推進を行うとともに、必要に応じて隨時、研究開発項目① (f1) とも連携を行う。

(f3) 仮想化基地局と計算基盤の同時最適化技術の開発（助成）【GX】

＜開発対象＞

- ・O-RAN及び仮想化技術を用いた情報処理リソースの省エネまたは最適化に資する装置および機能の開発

※移動通信システムのエンドツーエンド（RAN～トランスポートネットワーク～コアネットワーク）を鑑み、汎用データセンタでの適用可能性を含めて一体的に研究開発できること

- ・TDP3000W級のGPUに対応した液浸冷却装置等の冷却装置の開発

＜開発目標＞

- ・省エネ目標：研究開発開始時点で普及している製品を用いた場合と比べて、本成果を導入した際に、40%以上の消費電力削減されること

- ・冷却装置目標：研究開発開始時点の同種の冷却装置製品と比べて20%以上の小型化及び軽量化すること

- ・権利化及び標準化目標：本成果における技術に関して、権利化及び標準化に盛り込むこと

※標準化団体の例としては3GPP/O-RAN Allianceなど。標準化の際には本事業者を含む複数社の連名となっていることが望ましい

※標準化の前提となる本事業においても、密に研究開発を進められる複数の通信事業者で体制を成す事が望ましい

(g) 計算可能領域拡大のための計算基盤技術開発（委託、助成）

デジタル化の進展により大量のデータ処理への需要が高まっており、自動運転、スマートファクトリ、物流などポスト5G時代で導入が進む生成AIを含むアプリケーションの導入によってさらなる計算需要の拡大が予想される。

こうした計算需要に応えるためには、従来のクラウドサーバー等では処理能力が不十分なため、ポスト5G情報通信システムの一部として計算可能領域を拡大する計算基盤が必要であり、その計算基盤はスーパーコンピュータやAIコンピュータなど、いわゆる古典コンピュータだけでなく、量子コンピュータなどの様々な計算資源をネットワークでつなぎ、情報処理を進化させたものになると考えられる。

他方、生成AIは、従来のAIでは不可能だった、様々な創造的な作業を人間に代わって行える可能性があることから、産業活動・国民生活に大きなインパクトを与えると考えられており、ポスト5G時代のキラーアプリケーションとも位置づけられる。こうした技術を確保するためには、上記計算基盤のみならず、生成AIの中核的技術基盤である基盤モデルの開発（基盤モデルの開発に向けたデータプラットフォームの開発も含む）を進めていく必要がある。

#### (g1) 量子・スペコンの統合利用技術の開発（委託）

量子コンピュータは、従来のコンピュータとは全く異なる原理で動作し、特定の領域の問題に対しては情報処理を劇的に高速化できることから、従来のコンピュータでは事実上計算不可能な問題を処理できる特徴をもつ。このような領域の問題として、創薬・素材開発等における量子化学シミュレーション、金融・交通分野等における組み合わせ最適化、暗号解読等における素因数分解等の計算が挙げられており、ポスト5G情報通信システムを活用したユースケースとしては、スマートグリッドやサプライチェーン等の最適化などが期待される。こうした量子コンピュータの応用可能性については、様々な期待が寄せられつつも、日本では依然として未来の技術と見なされ十分な理解が進んでいない。結果として、企業等による投資や開発が停滞しており、特にゲート式量子コンピュータの開発では日本企業の国際競争力は見劣りする状況にある。

現在稼働中、あるいは提案されている量子コンピュータの多くは、周囲の熱や電磁気などによるノイズに弱く単体では実用的な計算が困難であり、そのため、古典コンピュータによる適切な制御、ノイズによるエラーの修正・補正、回路分割・最適化を行い、その上で量子と古典で得意な計算を分担しながら全体として計算能力を高める、いわゆる量子・古典ハイブリッド計算が注目されている。こうした中、量子コンピュータの性能向上に伴い、ハイブリッド計算に要求される古典コンピュータ側の処理も急速に高度化しており、従来の30量子ビット程度までは通常のサーバーでも処理できていたものが、最先端の100量子ビット級、さらにその先の大規模システムではスペコン超級の処理能力が不可欠になると予想される。このため、今後の量子コンピュータの早期の実用化による計算可能領域の拡大には、量子・スペコンの有機的な統合利用技術の確立が必須である。

本開発テーマでは、最先端の量子コンピュータに関わる技術や知見を活用しつつ、量子・スペコン連携ソフトウェア技術の開発に取り組む。具体的には、量子・スペコン連携のためのシステムソフトウェア、最適化ソフトウェア等を開発するとともに、これらを統合したパイロットプラットフォームを開発し、量子・古典ハイブリッド計算の有効性を実証する。なお、本テーマで開発する技術は、スペコン技術において世界最先端の一角を担う我が国において、特に量子コンピュータを支えるチョークポイント技術として育成すべきものでもあり重要性が高い。本開発テーマは、極めて先端的な技術開発を要し、外国政府による貿易管理規制の域外適用等の外部要因によって市場の有無が大きく左右され得るため、委託事業として実施する必要がある。

#### ＜開発対象＞

- ・ 量子・スペコン連携システムソフトウェア、スペコン向け量子プログラム最適化ソフトウェア、その他関連するソフトウェアに関わる技術

- ・ パイロットプラットフォームの構築ならびに運用に関わる技術

- ※パイロットプラットフォーム構築にあたっての注意事項を参照。

- ・ 実証に必要となる、量子ソフトウェア（アルゴリズム、アプリケーション）、性能指標に関わる技術

- ・ 開発した上記技術、アプリケーション等をクラウドサービスとして提供するための技

## 術

※パイロットプラットフォーム構築にあたっての注意事項：

- 現に保有するスーパーコンピュータ等に加え、技術開発に必要な機器（ゲート式量子コンピュータ実機、量子回路シミュレーション加速環境など）を利用すること。

- 量子コンピュータ実機は、量子ビット数100以上など、今日のスパコンではエミュレートが困難な性能・容量仕様を満たす、最先端機器とすること。複数基利用する場合は異なる特性のものとすること。

- 利用する機器は、量子・古典ハイブリッド計算の可能性を最大限追求できるように、現に保有するスパコン等と同一建屋内に設置され、高速・低遅延なネットワークで相互に接続されること。

- 産官学の利用者が当該プラットフォームを利用するための枠組みを整備すること。

### <開発目標>

- 本開発テーマで開発した量子・スパコン連携パイロットプラットフォームによる量子・古典ハイブリッド計算が有効になるアプリケーションドメインを明らかにし、計算可能領域の拡大および有効性を実証すること。: 1件以上

※例えば、「実応用において、開発したプラットフォームが、スパコン単体より処理速度や消費電力の点で優位であることを示す」といった形で設定し、その際、提案者にて具体的な指標、目標値を提案時に設定すること。

### <応募条件>

- 5年以上のスパコン運用の経験を有し、量子・スパコン連携プラットフォームの一部として利用可能なスパコンを現に保有し、事業期間終了時まで運用可能な企業等による応募、または、当該企業等との連携による応募であること。なお、ここでいうスパコンとは、「スーパーコンピューター導入手続」に定める理論的最高性能(※)以上のシステムに限る。

### ※「政府調達の自主的措置に関する関係省庁等会議」

(<https://www.cas.go.jp/seisaku/chotatsu/index.html>) 別紙2を参照

- 開発した成果の社会実装を担う企業等と共同で研究開発事業を実施すること。当該企業等は、開発した成果のクラウドサービスとしての提供等を担うものとする。

- 事業成果の最大化のため、必要に応じ、本事業で構築するパイロットプラットフォームはユーザー企業等にも利用してもらい、そのフィードバックを得て更なる改善を行うなど、可能な範囲でオープンイノベーションを推進するとともに、ユーザー企業等との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等を行うこと。

### (g2) 超省電力・高密度AI計算基盤技術の開発（委託）

AI技術は、自動車やロボットの自立型システム、医療診断や医療画像解析、自然言語処理による会話エージェントや顧客サポートなど、多岐にわたる利活用が進んでおり、こうした利用はポスト5Gによってさらなる拡大が見込まれる。また、計算機による物理シミュレーションをAIに代替させるサロゲートモデルのように、従来は現実的な時間で計算できなかった問題を処理する目的でもAIの活用が始まっている。

しかしながら、近年のAI技術の開発・利用に必要な計算能力は指数関数的に増加しており、IDC Japanの国内AIシステム市場予測(生成AIによる需要増含む)では2022~2027年のCAGRは23.2%で推移するとしており、5年後には現在の約3倍に達することが見込まれる。こうした需要増に応えるべくAIアクセラレータをはじめとするプロセッサの性能改善は続いているものの、半導体プロセスの微細化のペースや微細化に伴う電力効率の改善は鈍化傾向、プロセッサあたりの消費電力の増加に伴い商用データセンタにおける面積あたりの実装密度は低下傾向にあり、このままでは計算能力拡大の障害となることが予想される。

このため、AI技術が社会基盤・産業基盤の一部として持続的に発展し、計算可能領域を

引き続き拡大していくには、情報通信システムの一部として省電力かつ高密度な計算基盤技術の確立が必須であるため、本開発テーマでは、超省電力・高密度 AI 計算基盤技術の開発に取り組む。具体的には、超省電力 AI アクセラレーラチップ、当該チップを活用した AI サーバーシステムおよびその制御技術、商用運用の要件を満たす高密度データセンタ技術およびその制御技術を開発するとともに、これらを垂直統合した超省電力・高密度 AI 計算基盤とその最適運用技術を開発する。

本開発テーマは、極めて先端的な技術開発を要し、国際約束等の外部要因によって市場の有無が大きく左右されるものであることから、委託事業として実施する必要がある。

#### ＜開発対象＞

- ・ 超省電力 AI アクセラレーラチップ、当該チップを活用した AI サーバーシステムおよびその制御技術

- ・ 商用運用の要件を満たす高密度データセンタ技術およびその制御技術

- ・ 超省電力・高密度 AI 計算基盤およびその最適運用技術

#### ＜開発目標＞

- ・ 開発した AI サーバーシステムの電力あたりの実効計算性能：

研究開発開始時点で普及している製品（AI サーバーシステム）と比較して十分な優位性があることを検証

※提案者にて「電力あたりの実効計算性能 X TFLOPS/W 以上、かつ普及している製品と比較して N 倍以上」といった目標値を提案時に設定すること。

- ・ 開発した高密度データセンタのラックあたりの定格設計密度：

研究開発開始時点で普及している製品（商用データセンタ）と比較して十分な優勢があることを検証

※提案者にて「ラックあたりの定格設計密度 N kVA 以上」といった目標値を提案時に設定すること。

- ・ 開発した AI 計算基盤の面積あたりの実効計算性能および実効スループット性能：

研究開発開始時点で普及している製品（商用データセンタ、AI 計算基盤）と比較して十分な優位性があることを検証

※提案者にて「面積あたりの実効計算性能 X PFLOPS 以上、かつ普及している製品と比較して実効スループット性能 N 倍以上」といった目標値を提案時に設定すること。

#### ＜応募条件＞

- ・ AI 計算基盤の一部を開発・供給する海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として当該企業等が参画すること。

※「海外企業等」として、提案者の親会社、子会社は対象外とする。

- ・ 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等も踏まえて、追加で条件が付される可能性がある。

#### (g3) 競争力ある生成 AI 基盤モデルの開発 (GENIAC) (助成)

生成 AI は、従来の AI では不可能だった、様々な創造的な作業を人間に代わって行える可能性があることから、産業活動・国民生活に大きなインパクトを与えると考えられており、ポスト 5G 時代のキラーアプリケーションとしても位置づけられる。

2023 年 5 月に AI 戦略会議で取りまとめられた「AI に関する暫定的な論点整理」においては、「いま生成 AI によって世界の変革がもたらされようとしている中、可及的速やかに生成 AI に関する基盤的な研究力・開発力を国内に醸成することが重要」とされており、政府として取組の一層の加速が求められている。加えて、「生成 AI の技術革新のスピードや予見可能性の低さを踏まえると、従来の政府による開発促進策では対応が難しい」、「市場原理を最大限尊重し、迅速、柔軟かつ集約的にプレイヤーの取組を加速するような支援を政府としても行っていくことが期待される」と明記されているところ。

その生成 AI の鍵を握るのは、基盤モデル開発である。基盤モデルは、生成 AI を活用した様々なサービスを支える個別モデルを生み出すコアの技術基盤であり、基盤モデルの開発力の有無は、我が国における生成 AI の利用可能性や創出するイノベーションの幅を決し得る。このため、日本として基盤モデルの持続的な開発力を強化していく必要があり、それに向けて、基盤モデルの開発力の底上げを図りつつ、企業等の創意工夫を促すことが重要である。

他方、生成 AI は黎明期であり、あらかじめ開発すべき基盤モデルや開発体制を特定することは困難でもある。そのため、本テーマでは開発アイデアを広く募集した上で、支援対象を絞り込む形で基盤モデルの開発に取り組むこととする。

なお、本テーマの実施にあたっては、基盤モデル開発の加速にあたって重要である、知見の共有や客観的な性能評価の実施、良質のデータを確保する観点から、データホルダーとのマッチング支援、グローバルテック企業との連携支援やコミュニティイベントの開催、開発される基盤モデルの性能評価等を実施する者（開発加速支援者）を別途選定することとする。

#### ＜開発対象＞

本事業で開発対象となるのは、以下の基盤モデル開発。提案者にて、提案時に開発内容を提案すること。

- ・ フルスクラッチで開発するモデル

- ・ 既存の基盤モデル（国内で開発された基盤モデルに限らない）を事前追加学習するモデル

- ・ 国内で開発された基盤モデルをファインチューニングするモデル

- ※上記より、提案者にて提案時に開発内容を提案すること。

- ※「国内で開発された基盤モデル」とは、日本国内で登記され、かつ、日本国内に開発拠点を有する企業・大学等が開発した基盤モデルのことを指す。

- ※なお、本基盤モデル開発に併せて、社会実装を見据え、当該基盤モデルを元にした個別モデルやアプリケーションの開発を行うことは妨げない。

#### ＜実施目標＞

- ・ 開発した生成 AI の基盤モデルが国際的に比較して十分な優位性があることを検証

- ※提案者にて、ベンチマークや、「機械翻訳の最先端レベルに対して N% 以上の性能を達成できる」といった目標を提案時に設定すること。

#### ＜応募条件＞

- ・ 本基盤モデル開発においては、基盤モデルの評価で利用するベンチマークのデータセットは利用しないこと。この他、利用できないデータセットについて、経済産業省、NEDO、開発加速支援者と調整の上、指示に従うこと。

- ・ 定期的に性能評価を実施し、経済産業省、NEDO、開発加速支援者に評価結果を提出することを条件とする。基盤モデルについては、既存のベンチマークもしくは基盤モデル開発者等が策定したベンチマークで適正に評価すること。基盤モデル開発者等が策定するベンチマークの詳細については、経済産業省、NEDO、開発加速支援者と調整の上、指示に従うこと。研究開発期間終了後に、既存のベンチマークもしくは基盤モデル開発者等が策定したベンチマークで評価を実施した結果を公表することを条件とする。

- ・ 開発加速支援者が運営するコミュニティに積極的に参加すること。

- ・ データセットの生成や事前追加学習等にあたって使用する外部の AI モデルについて、経済産業省、NEDO、開発加速支援者から情報提供の依頼があった場合には、それに応じること。また、使用する外部の AI モデルについては、必要に応じて、経済産業省、NEDO、開発加速支援者と調整の上、その指示に従うこととする。

- ・ 経済産業省から開発するモデル等について情報提供の依頼があった場合には、最大

- 限協力すること。

- 開発を進めるにあたっての詳細は、必要に応じて、経済産業省、NEDO、開発加速支援者と調整の上、決定することとする。

(g4) ロボティクス分野の生成 AI 基盤モデルの開発に向けたデータプラットフォームに係る開発（委託）

生成 AI は、様々な創造的な作業を人間に代わって行える可能性があることから、今後の我が国産業における生産性向上やイノベーション創出のカギとなる技術である。また、産業活動・国民生活に大きなインパクトを与えると考えられており、ポスト 5G 時代のキラーアプリケーションとしても位置づけられる。

我が国産業の生産性向上に向けて、サービス業等へのロボットの導入を進めていくことが期待されるが、幅広く多様な動作、予測が難しい事象、人との接近を伴う業務への対応が求められることから、こうした分野へのロボット導入に向けては、ロボティクス分野における生成 AI 基盤モデルの開発・実装が不可欠。他方、言語・画像等の分野と異なり、ロボティクス分野の生成 AI 基盤モデルの開発に向けては、汎用的なモデル開発に必要なデータが特定されていないことや、インターネット上に蓄積されたテキストや画像等のデータと異なり、現実空間の認識や物理的な稼働に関するデータが収集されていないことなどの課題が存在する。

こうした状況を踏まえ、本テーマでは、データ収集、基盤モデルの開発、実現場における実証を通じて、ロボティクス分野の生成 AI 基盤モデルの開発に有効なデータプラットフォームの研究開発に取り組む。また、その成果は最大限オープンにし、我が国のロボティクス分野の生成 AI 基盤モデルの開発に広く還元する。

本テーマは、ロボティクス分野における生成 AI 基盤モデルの開発を行うために不可欠なデータプラットフォーム構築に係る研究開発であり、その成果が広く我が国の生成 AI 開発者等に裨益することから、委託事業として実施する必要がある。

＜開発対象＞

- ロボティクス分野の生成 AI 基盤モデルの開発に有効なデータプラットフォーム

- ※上記の開発に向けて必要となる生成 AI 基盤モデルの開発や実証（個別モデルの開発等を含む）も実施すること。

＜開発目標＞

- データプラットフォームの開発に向けて収集するデータの種類と量：

提案者にて、提案時点で収集されているデータセットと比較して質的・量的な観点で十分な優位性を示すような、具体的な目標を設定すること。

- データプラットフォームのデータを用いて開発した生成 AI 基盤モデルの性能：

提案者にて、開発する生成 AI 基盤モデルが十分な優位性を有することを示すような、具体的な目標を設定すること。

- データプラットフォームのデータを用いて開発した生成 AI 基盤モデルの実環境における評価／検証：

- 1 件以上

＜応募条件＞

- 本テーマで開発したデータプラットフォームのデータや生成 AI 基盤モデル等の成果やナレッジを広く公表すること（可能な限りオープンにすること）。産業界と学術界が広く参加する形で提案すること。

- 他のデータプラットフォームとの連携に関して、経済産業省からの指示があった場合は、協議の上、その指示に従うこと。

- 本テーマで構築するデータの保管や提供を実施する者（以下、データ管理者）は、

事業期間終了以降もデータの保管や提供にかかる経費を継続的に支出できる事業者であること（事業期間終了後の保管費用を NEDO から支出できないことに留意すること）。

- データについては、データ利用条件を明文化し、その条件を満たす利用者に対して公平に提供すること。利用者の種別に応じて提供するデータを制約しないこと。

- そのデータ利用条件では、過去の実績を含め、日本の法令や国際的に受け入れられた基準等を遵守していない、又はサイバーセキュリティの確保について外国の法的環境等により影響を受ける者（以下、国際基準不遵守等事業者）に対するデータの提供は行わないこと。

- 事業期間終了後、データ管理者を国際基準不遵守等事業者に変更しないこと。

- ロボティクス分野の生成 AI 開発に向けた人材育成やナレッジの涵養の観点から、例えば、海外のトップ企業やトップエンジニアとの交流等に取り組むことが望ましい。

- 開発を進めるにあたっての詳細は、必要に応じて、経済産業省と調整の上、決定することとする。

- 経済産業省が指定するコミュニティに積極的に参加すること。

#### (g5) 量子コンピュータの産業化に向けた開発の加速（委託、助成）

量子コンピュータは従来技術では不可能な計算問題を解決でき、産業革命を起こし得るものであり、ポスト 5G に対応した情報通信システムにおいても重要な新規の計算基盤技術である。新規の材料・薬剤開発、輸送・交通の最適化、暗号解読等の非常に多岐にわたる産業分野での活用が期待される。世界各国で政府が量子コンピュータに関する大型投資を進めていることに加え、論理量子ビットの生成含む誤り訂正技術の向上等の画期的な発表やスタートアップの創業が相次ぐなど、基礎学理の研究だけでなく産業化に向けた国際競争は激化している。

各国の量子コンピュータ企業において、2030 年頃に産業利用可能な性能を有する量子コンピュータを開発するという野心的なロードマップが示されている。また我が国においても、「量子技術イノベーション戦略」、「量子未来社会ビジョン」、「量子未来産業創出戦略」の 3 つの国家戦略の中で、「量子技術による生産額を 50 兆円規模」といった壮大な目標を掲げている。

このような世界的な開発競争の中で、我が国の量子コンピュータ分野におけるプレゼンスを獲得するとともに、量子コンピュータの産業化を我が国がいち早く実現することが、国富の獲得やデジタル赤字の解消等に不可欠である。量子コンピュータの産業化を我が国だけで実現することは困難であるが、現在の我が国技術の成熟度等を勘案して、次世代の量子コンピュータ業界において、戦略的不可欠性と自立性を獲得・維持・強化するための技術開発を現時点から開始する必要がある。

量子コンピュータの発展によって最も大きな寄与を受けるのはユースケースであるが、そのための計算環境の高度化・整備と計算時間の確保には外国製ハードウェアの導入やクラウド利用だけでは不十分である。ユースケース創出において先行するには、国産の次世代ハードウェアが不可欠であり、この開発を更に加速させる必要がある。そのための部素材開発が必要なのは勿論であるが、部素材は国内市場だけでなく、世界市場を獲得できうるもののが開発を中心に支援する。これにより国産の部素材が他国の量子コンピュータにおいても必ず使われている状況を作り出していく。また実際の計算は量子コンピュータだけでなく、CPU・GPU の古典コンピュータとのハイブリッド利用によってなされる。このような計算をユーザーが容易に可能にするためのミドルウェア開発も産業化には不可欠である。

そこで本テーマでは、超伝導方式、中性原子方式、光方式の量子コンピュータシステムの民間による開発、関連する部素材やミドルウェア開発への重点支援を実施し、開発を加速させる。これにより、世界に先駆けて量子コンピュータの産業化の実現を目指す。以下に、その開発対象と開発目標を開発要素毎に記すとともに、後段において (g5) 共通の応募における推奨事項ならびに応募条件等を記す。

### (g5-1) 産業化に向けた量子コンピュータシステムに関する技術開発（助成）

以下のゲート型量子コンピュータの方式において、2030年頃における産業化が可能な量子コンピュータシステムを実現するために必要な技術開発を行う。例えば本事業期間内で量子ビット数をスケール可能な技術等を開発し、本技術を元にして2030年頃に実用化に必要な量子ビット数を持つ量子コンピュータシステムを構築する提案などが挙げられる。また提案者は可能な限り、ユースケース創出に不可欠な量子古典ハイブリッド計算環境の構築を念頭において開発をすること。

#### (g5-1-1) 超伝導方式量子コンピュータシステム

##### ＜開発対象＞

- 量子チップ間の量子接続や高密度実装などスケーラブルに物理量子ビット数を増加できる技術、高精度・高スループットな物理量子ビットの製作技術、デコーディング技術など計算操作時等のエラー率低減や論理量子ビット作成・高度化、コヒーレンス時間の延長などによるゲート数増加に関する技術、小型化・低コスト化・低消費電力化など、量子コンピュータの産業化のために必要な要素技術やそれらを統合したシステムなどの開発及び評価等を行う。

##### ＜開発目標＞

- 開発した技術・システムによって将来達成される量子コンピュータの性能（物理・論理量子ビット数、物理・論理エラー率、物理・論理ゲート数、物理・論理動作速度、コスト、消費電力、安定性、計算可能なアルゴリズムなど）が、2030年頃に予想・提案されている性能と比較して、競争力がある（もしくは優位性がある）ことを検証すること、もしくは産業利用可能な性能を有すること等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

#### (g5-1-2) 中性原子方式量子コンピュータシステム

##### ＜開発対象＞

- 高強度レーザーなどを活用したスケーラブルに物理量子ビット数を増加できる技術、計算操作時等のエラー率低減や論理量子ビット作成・高度化などによるゲート数増加に関する技術、量子計算の安定化技術、アプリ特化量子計算・制御技術など量子コンピュータの産業化のために必要な技術開発、これらの達成に不可欠な要素技術（評価技術含む）の開発、それらを統合したシステムなどの開発及び評価等を行う。

##### ＜開発目標＞

- 開発した技術・システムによって将来達成される量子コンピュータの性能（物理・論理量子ビット数、物理・論理エラー率、物理・論理ゲート数、物理・論理動作速度、コスト、消費電力、安定性、計算可能なアルゴリズムなど）が、2030年頃に予想・提案されている性能と比較して、競争力がある（もしくは優位性がある）ことを検証すること、もしくは産業利用可能な性能を有すること等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

#### (g5-1-3) 光方式量子コンピュータシステム

##### ＜開発対象＞

- 光学系や検出システムの最適化などスケーラブルに量子モード数もしくは物理量子ビット数を増加できる技術、計算操作時等のエラー率低減や論理量子ビット作成・高度化、光学システムの安定化等によるゲート数増加に関する技術、クラウド化など開発システムの利用のための技術、小型化・低コスト化・低消費電力化など、量子コンピュータの産業化のために必要な要素技術やそれらを統合したシステムなどの開発及び評価等を行う。

＜開発目標＞

- 開発した技術・システムによって将来達成される量子コンピュータの性能（物理・論理量子ビット数、物理・論理エラー率、物理・論理ゲート数、物理・論理動作速度、コスト、消費電力、安定性、計算可能なアルゴリズムなど）が、2030年頃で予想・提案されている性能と比較して、競争力がある（もしくは優位性がある）ことを検証すること、もしくは産業利用可能な性能を有すること等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2) 産業化に向けた量子コンピュータの部素材の高度化に関する技術開発

((g5-2-1) ~ (g5-2-6) : 助成、(g5-2-7) ~ (g5-2-9) : 1、2年目委託、3年目助成)

次世代の大規模量子コンピュータの実現に重要な部素材の高度化、実用化や産業化のための技術開発を行う。

(g5-2-1) 低温環境動作可能な小型ケーブル及びコネクタ

＜開発対象＞

- 超伝導方式やシリコン半導体方式など極低温環境下で動作する量子コンピュータにおいて利用される、低温環境動作が可能な高周波信号ケーブルの高度化（断熱性能、高周波信号透過率、実装密度、小型化など）、その接続コネクタ（断熱性能、高周波信号透過率、実装密度、小型化、接続容易化など）の高度化に関する技術（特性評価技術含む）及び他の低温コンポーネントとの統合・一体モジュール化技術等を開発する。

＜開発目標＞

- 利用される量子コンピュータの方式を明示した上で、開発した部素材及びそのシステムの性能（低温環境下での断熱性能・高周波信号透過率、実装密度、サイズ、コストなど）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材及びそのシステムが量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2-2) 連続波発振型レーザーシステム

＜開発対象＞

- レーザー光を用いて動作する量子コンピュータにおいて利用される、連続波発振型の単一波長レーザーシステムの高強度化もしくは高強度化レーザーシステムの強度、周波数など各種パラメータの安定化・低ノイズ化などの高度化に関する技術（特性評価技術含む）等を開発する。

＜開発目標＞

- 利用される量子コンピュータの方式（必要な場合は原子種等も）を明示した上で、開発した機器の性能（強度、波長安定性、位相ノイズレベル、コストなど）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材が量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2-3) 量子コンピュータインターフェイス装置

＜開発対象＞

- レーザー光を用いて動作する量子コンピュータにおいて利用される、量子コンピュータシステム間を量子的かつコヒーレントに接続できるインターフェイス装置の実証や高度化（高速化、低エラー化、量子もつれ生成率、小型化など）に関する技術（特

性評価技術含む）等を開発する。

＜開発目標＞

- 利用される量子コンピュータの方式（中性原子方式やイオントラップ方式では原子種もしくはイオン種も）を明示した上で、開発した機器を実装したことによる量子コンピュータシステム全体の性能（量子ビット数、接続速度、接続精度、コストなど）目標を明確にしたうえで、研究開発開始時点で普及している同方式の機器と比較して十分な優位性があること、もしくは開発した機器が量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2-4) 非線形光学デバイス

＜開発対象＞

- レーザー光を用いて動作する量子コンピュータにおいて利用される、量子もつれ光（スクイーズド光）の発生・検出や光ピンセット・量子ビット状態の観測等に用いるレーザー光の強度、周波数など各種パラメータの制御のための光学デバイスの高度化に関する技術（特性評価技術含む）等を開発する。

- 例えば、光方式量子コンピュータシステムに利用される量子もつれ光（スクイーズド光）の発生に用いる光学デバイスの場合、スクイーズド光の高レベル化・広帯域化、低ノイズ化、低消費電力化（駆動に必要なレーザーパワーの減少などによる）、光ファイバーとの高効率な接続技術などのデバイスの開発・実装に関する高度化技術だけでなく、材料に用いる光学結晶（ニオブ酸リチウムなど）の大型化・高品質化、厚さが均一な大型ウェハー、大型均質複合ウェハー作製技術、基板・薄膜接合技術、高品質導波路作成技術、光電融合デバイス加工技術など原材料とその加工技術の高度化に関する基盤技術も必要に応じて開発する。これに限定せず、量子コンピュータに利用される非線形光学デバイスの開発・高度化技術に関して提案すること。

＜開発目標＞

- 利用される量子コンピュータの方式を明示した上で、開発した機器の性能（スクイーズドレベル、ノイズレベル、サイズ、コストなど）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材が量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2-5) 量子ビット制御・検出用光学システム

＜開発対象＞

- レーザー光を用いて動作する量子コンピュータにおいて利用される、量子ビットからの発光を検出する高感度カメラや高速・高感度光センサ、光ピンセット等の量子ビットの作製・制御に利用する空間光変調器など光学システムの高度化に関する技術（特性評価技術含む）等を開発する。

- 主な開発技術の対象としては、高感度カメラは多画素化・低ノイズ化・高速撮像化など、高速・高感度光センサは高感度化・高速化・複数素子化など、空間光変調器は多画素化・高耐光性などが挙げられるが、これらに限らない。

＜開発目標＞

- 利用される量子コンピュータの方式を明示した上で、開発した機器の性能（高感度化、高速化、多画素化、複数素子化など）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材が量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビ

ットとの連結動作評価・実証等) 等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

#### (g5-2-6) 量子コンピュータ制御システム

##### <開発対象>

- 超伝導方式などの様々な方式の量子コンピュータの制御システムに関して、将来的に最大100万物理量子ビット規模の大規模化量子コンピュータへの実現を可能とするスケーラブルな制御システム（量子ビット・量子集積回路の評価やキャリブレーションの高速化、エラー訂正のための制御技術など）、複数方式への対応・応用、低コスト化、高機能化、量産化（歩留まりの向上等）などの高度化に関する技術（特性評価技術含む）等を開発する。

##### <開発目標>

- 応用可能な量子コンピュータの方式、量子エラー訂正手法、量子ビットの規模等を明示した上で、開発したシステムの性能（低コスト化、制御可能な物理・論理量子ビット数、対応可能な量子エラー訂正符号、サイズ、消費電力、コンピュータとのレイテンシー、物理及び論理量子ビットの処理速度など）が、研究開発開始時点で普及している同方式のものと比較して十分な優位性があること、もしくは開発したシステムが量子コンピュータの性能を向上させること（例えは量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

#### (g5-2-7) クライオ電子回路システム

##### <開発対象>

- 超伝導方式やシリコン半導体方式など極低温環境下で動作する量子ビットの制御や検出を行うため、超伝導素子やCMOS素子等を用いて高周波信号の倍化や増幅、制御信号のアナログデジタル変換、デジタルアナログ変換、量子エラー訂正符号化・復号化処理などの量子ビットの制御や信号変換などを行うための極低温環境下（10mKや4Kなど）で動作する電子集積回路システムの実用化のための技術開発（設計、製造、実証技術など）及び他の低温コンポーネントとの統合・一体モジュール化技術等を開発する。

##### <開発目標>

- 開発した部素材の性能（回路システム等の機能、制御可能な量子ビット数、対応可能な量子エラー訂正符号化・復号化方式、発熱性、エネルギー効率、サイズ、コストなど）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材が量子コンピュータの性能を向上させること（例えは量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

#### (g5-2-8) 高冷凍能力な極低温対応冷凍機システム

##### <開発対象>

- 現在の超伝導方式量子コンピュータに用いられている冷凍機は特に4K程度の温度領域における冷却性能に限界があり、(g5-2-7) で開発するクライオ電子回路システム等を十分に設置することが困難である。そのため現在の量子コンピュータ用冷凍機とは異なる冷却方式などを活用することで、次世代の大規模量子コンピュータにおいて4K付近及び10mK付近において十分な冷却性能を有する冷凍システムの開発や、そのための要素技術（特性評価技術含む）等を開発する。

##### <開発目標>

- 開発したシステムの性能（冷凍性能、エネルギー効率、コスト、サイズ、消費電力、冷却可能な物理量子ビット数など）が、研究開発開始時点で普及している同方式のものと比較して十分な優位性があること、もしくは開発したシステムが量子コンピュータの性能を向上させること等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-2-9) 超伝導転移端光センサシステム

<開発対象>

- 産業利用可能な光量子コンピュータの開発には、光子数識別が可能な光検出システムの高度化が不可欠である。そのため、光量子コンピュータのための超伝導転移端光センサシステムの高度化（高速応答化、光子数識別能力、高精度化など）及びそのための要素技術（特性評価技術含む）等を開発する。

<開発目標>

- 開発した部素材の性能（計測速度、光子数識別能力、精度、感度、コストなど）が、研究開発開始時点で普及している同方式の部材と比較して十分な優位性があること、もしくは開発した部素材が量子コンピュータの性能を向上させること（例えば量子コンピュータ実機もしくは量子ビットとの連結動作評価・実証等）等を検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

(g5-3) 量子コンピュータの産業化のためのミドルウェア開発（助成）

<開発対象>

- 産業利用可能な量子コンピュータを将来的に容易にユーザーが利用できる環境を整備するために、シミュレーテッドアニーリングや量子回路シミュレーションを含む複数方式の量子コンピュータや古典コンピュータのハイブリッド利用を可能にするミドルウェア及びそのために必要な要素技術（計算資源最適化技術など）、これらを実装した計算環境等を開発する。

- 例えば量子コンピュータが進化した場合でも共通利用可能なA P Iなどを開発・実装することで、将来的な量子コンピュータの進化・産業利用化に伴い、計算を行うコンピュータの種類（古典、量子含む）が変化した場合でも、これまでのプログラム技術を継続して利用できるミドルウェア・計算環境を開発する。

- 必要に応じて、開発ミドルウェアや環境等のビジネス利用に向けた評価のための計算環境等を開発する。

<開発目標>

- 開発したミドルウェア等により可能になる機能（量子コンピュータの進化に対する追従能力等）が研究開発開始時点で普及している類似の製品と比較して十分な優位性があること、もしくは2030年頃の量子コンピュータ性能を仮定した時に開発したミドルウェア等による計算性能が産業化に十分なものであること等を量子コンピュータ実機や大型GPUコンピュータへの接続などを通じて検証すること。

※提案者にて評価すべき性能やその目標値を提案時に設定すること。

<応募における推奨事項等> \*記載が無い限り、(g5) 共通

- 各開発要素の単独提案だけでなく、複数の要素をまとめた提案の応募も歓迎する。

- プロジェクトの効率的かつ効果的な実施の観点から、国立研究開発法人産業技術総合研究所に設置した量子・AI融合技術ビジネス開発グローバル研究センター（G-QuAT）に整備している関連施設・装置等を可能な限り活用することを推奨する。活用する場合、提案時にその内容・調整状況等を記載すること。

- (g5-2) に関して、開発した部素材等の量子コンピュータ以外の応用先が想定され

る場合、その応用やビジネス化に必要な内容を、提案の一部に含めても良い。ただし量子コンピュータへの応用は必須であることに留意すること。

＜応募条件＞ \*記載が無い限り、(g5) 共通

- 提案内容は3年間分を記載し、事業開始2年後（令和7年度末時点）及び3年後（令和8年度末時点）における目標値を提案時に設定すること。

- 開発内容に関する知財化や国際標準化の戦略及びこれらに関連する活動（調査含む）の内容を提案時に記載すること。なお、国際標準化活動の場となる国際標準化委員会はISO/IEC JTC3に限定しない。

- 本提案の開発に用いる重要な部品・材料・装置等のサプライチェーンの強靭化及び安定性確保の観点から、上記の調達等における事業リスク分析（例えば調達物品の製造元国や外注予定国のリスト化など）及びその対応策について提案すること。ただし採択段階では、研究が進展しなければ判明しないリスクも想定されることから、リスク分析及び対応策立案に関する今後の方針の提案でも可とする。研究開発段階が進むにつれて、より具体的な分析及び対応策を要することとする。

- 複数の事業者や研究開発拠点において本事業を行う場合、各事業者・拠点における実施内容を明確に記載すること。特に国外の事業者、拠点において活動を行う場合、国外で行うことの必要性を明記すること。

- 「5. 実施体制等」に記載の通り、研究開発能力を最大限に活用し、効率的かつ効果的に研究開発を推進する観点から、NEDOは研究開発責任者（プロジェクトリーダー）を選定する。各実施者はプロジェクトリーダーの下で研究開発を実施することをあらかじめ了解すること。なお、必要に応じてプロジェクトリーダーの下に、SPL（サブプロジェクトリーダー）を設置することがあり、その場合も同様である。

(g6) AI用計算資源の高度化に向けた研究開発（委託・助成）【GX】

生成AIは、あらゆる分野で利用され、その開発や利活用等のイノベーションが社会課題の解決や国際的な競争力に直結する可能性があると考えられている。今後、生成AIの利活用が拡大するにともない、計算需要が一層高まると予想されている。そのような状況のなか、国内の計算資源の量的拡大を継続するだけでなく、省エネなどの観点も踏まえて、学習や推論など用途に応じた最適なAI半導体の選択と、その効率性や利便性の向上に資するソフトウェアの開発を進めることで、ポスト5G情報通信システムの一部としてのAI用計算資源の高度化を実現することが重要である。そして、これらのソフトウェアを、日本国内で登記され、かつ、日本国内で計算資源を提供する事業者（以下、計算資源提供者）に広く提供することで、競争力を底上げするとともに、AIの開発力・供給力の強化を図る。

令和6年6月に閣議決定された統合イノベーション戦略2024においては、この生成AIのイノベーションを加速する好循環の形成を図っていくために、「計算資源等のインフラの高度化とともに、AI利活用の推進と研究開発力の強化を一体的に官民が連携して進めていく。」と明記されており、政府として取組の一層の加速が求められている。

これまで、生成AIの開発においては、基盤モデルの学習に計算資源の需要が集中していたが、今後はアプリケーション実行時の推論への計算資源の需要も加わり、需給の逼迫が不可避な状況である。AI半導体は、高性能化と低消費電力化を両立すべく、学習・推論など用途に応じて必要な機能を組み合わせた専用半導体の開発が進められており、今後、市場投入される多様なAI半導体を高効率に利用するニーズが見込まれている。また、国内の一部の計算資源提供者においては、計算資源の利便性を向上させるソフトウェアの実装が不十分な場合、AI基盤モデルの構築やAIサービスの提供を行う事業者（以下、AIサービス提供者）によっては、その計算資源を十分に活用できない可能性がある。

このため、本テーマでは、多様なAI半導体で構成されるAI用計算資源の利用・普及および利便性の向上のために、①計算資源提供者が各種AI半導体の特性を活かしながら

高効率に資源提供し利用できるようにするソフトウェアの研究・開発、そして、②A I サービス提供者が多様なA I 半導体を利用できるテストベッド環境の構築とその運用技術やA I 半導体の評価技術に関するソフトウェアの開発、③A I サービス提供者による計算資源利用の利便性を向上するソフトウェアの開発に取り組むものとする。このテーマで開発されたソフトウェアと評価結果は国内の計算資源提供者の事業に資するものとする。

本テーマの実施においては、参加事業者はテストベッド環境を共用するものとする。また、単に個社がソフトウェアを開発する取組とのではなく、参加事業者同士で、人的交流や知識共有、技術仕様の標準化など、技術連携を進めることで事業成果の最大化を図る。更に事業成果を利用する計算資源提供者とも連携して研究開発を実施することで、開発・利活用のエコシステムを構築するなどの点に配慮するものとする。

本テーマは、各種A I 半導体を活用したテストベット環境を構築・運営する事業者（以下、テストベット提供者）が、従来広く使用されているG P Uだけでなく、商業利用の見通しが不透明な国産をはじめとする新興A I 半導体を幅広くかつ重点的にテストベッド環境に整備して、他の事業者と共同で、その高効率利用性や利便性向上に資するソフトウェアの開発、システム性能評価データの取得、そして性能評価データの計算資源事業者への提供を実施することにより、多様なA I 半導体の利用・普及、利便性の促進に寄与するものである。テストベッド環境構築には国産のA I 半導体も含まれるが、多くは外国から輸入したA I 半導体を対象としたソフトウェアの研究開発を要し、外国政府による貿易管理規制の域外適用等の外部要因によって市場の有無が大きく左右され得る。またこれに加え、初期投資が膨大であり、民間企業単独や民間団体・コンソーシアム等では整備が困難であることが懸念される。このため、本事業は初年度の基礎的研究開発については、委託事業として実施する。また、本開発テーマは計算資源の利用を高度化する基盤的な研究開発事業であるが、同時に計算資源提供者の自社事業に裨益する内容でもあるが懸念される。こうしたことから、民間事業者に対しては、初年度は委託事業としてはじめるが、2年目以降は、助成事業に切り替え、その補助率も段階的に引き下げるものとする。具体的には、本事業は5年間の研究開発計画として実施し、初年度は委託契約により、N E D O が全額（100%）を負担する。2年目以降は助成金事業に移行し、2～4年目は助成対象経費の2/3、5年目は1/2をN E D O が助成する。但し、テストベット整備及び本事業期間中のテストベッド運用については、その運用のための環境整備も含め民間企業／学術機関等の種別によらず、委託事業として実施する。

#### ＜開発対象＞

- ・ 多様なA I 半導体から成るテストベッド構築とその運用、性能評価のためのソフトウェアの研究・開発

- ・ 各種A I 用半導体の特性を活かし、学習や推論などの用途に応じてその高効率な利用を可能にするソフトウェアの研究・開発

- ・ テストベッドなどの計算資源利用の利便性を向上するソフトウェアの研究・開発

#### ＜開発目標＞

- ・ 各種A I 半導体を使い分けるための評価指標（電力あたりの計算性能など）を定め、基準となるA I 半導体と比較しその優位性をテストベッド上で定量的または定性的に比較し示すこと。

- ・ 提案時にソフトウェアによる改善期待効果を各種指標（学習や推論の処理時間、レイテンシーやスループット、電力消費量、必要な計算資源、G P U稼働率、作業コスト、作業時間など）において、従来技術と比較しN倍以上といった定量的目標または定性的目標を設定し、本事業で検証すること。

#### ＜応募条件＞

- ・ 本事業は、テストベット構築・運用のみの提案は認められない。また、研究機関単独

での応募は認められない。事業者は日本国内で登記された事業者であること。

- ・ 個社単独でソフトウェアを開発するのではなく、他の本事業参画事業者との人的交流や知識共有、技術仕様の標準化など、技術連携を進めることで事業成果の最大化を図ることを推奨する。

- ・ 事業開始時点で普及しているAI半導体以外のAI半導体を含む2種以上のAI半導体上で動作するソフトウェアの研究・開発を推奨する。

- ・ ソフトウェアの初期バージョンを、事業開始から2年以内に、テストベッド環境で使用可能な状態にすること。また本研究開発事業の趣旨に則り、事業期間中はAI半導体の技術動向に応じてソフトウェアの更新を推奨する。

- ・ テストベッドは、(a)研究開発時点で普及しているGPU、(b)HPC分野で実績があり今後AI分野でも普及が期待される汎用的な半導体、(c)推論や学習性能が期待できる専用半導体、(d)今後の成長を期待する国産のAI半導体などに分類し、(a)(b)(c)(d)のそれぞれから1機種以上を選択することで、できるだけ多様なAI半導体をテストベッド環境に整備すること。また、学習や推論などの用途毎に、AI半導体の現実的な性能評価の実施に必要となる前提条件や数量を設定すること。事業期間中はテストベッドの運用・更新・提供を続けること。

※提案者にて、現実的な性能評価に必要な前提条件を設定した上で、それに対応するAI半導体の詳細リストを添付すること

## ②先端半導体製造技術の開発（助成、委託）

情報通信システムにおいては、装置内で信号の処理を行う半導体が極めて重要な役割を担う。また、デジタル化の進展により大量のデータ処理への需要が高まっており、自動運転、スマートファクトリ、物流などポスト5G時代で導入が進むアプリケーションによってさらに計算需要が増えると予想される。こうした計算需要に応えるためには高性能かつ高効率な計算基盤の構築が必要であり、その計算基盤はスーパーコンピュータやAIコンピュータ、高性能コンピュータだけでなく、量子コンピュータなどの様々な計算資源をネットワークでつなぎ、情報処理を最適化したものであると考えられる。

現在、日本国内には、ポスト5Gを含む情報通信システムや計算基盤において必要となる先端的なロジック半導体等（以下、「先端半導体」）の製造能力が無く、供給安定性等の観点で脆弱な状況にある一方で、ポスト5G以降の情報通信システムや計算基盤においては、先端半導体の重要性が更に増していくと考えられる。

このため、将来的に、情報通信システムや計算基盤で用いられる先端半導体を国内で製造できる技術を確保するため、先端半導体の製造技術の開発に取り組む。具体的には、パイロットライン（一部の製造工程から成るリサーチライン、ウェハーを国内で相互に移送することにより一繋ぎのラインとして機能するものを含む。）の構築等を通じて、国内に無い先端半導体及びその周辺デバイスの製造技術（ロジック半導体と組み合わせて動作するメモリや光デバイス等に関する技術、ロジック半導体を含む複数の半導体の実装技術等を含む。）を開発する。さらに、国際連携により、最先端ロジック半導体の製造技術を確立する。

先端半導体は更なる微細化が進展しつつあり、2020年において最先端のロジック半導体は5nmノードに達するとともに、前工程の製造・プロセス技術は今後も微細化(More Moore)が継続し、高性能化・低消費電力化することが想定されている。

また、後工程のMore than Moore技術においても、2次元高密度実装や3次元(2.xD、3D)実装の進展、パッケージ基板の大面積化により、SiP (System in Package)としての高性能化やチップ間インターフェクトの帯域幅拡大が進みつつある。

加えて、ロジック半導体が十分に機能を発揮するためには、メモリ(SRAM、DRAM等)、ストレージクラスメモリ(MRAM、PCRAM等)、ストレージ(NAND Flash等)、センサー(イメージセンサー等)等の周辺デバイスとの高速なインターフェクトの確保も不可欠であり、その帯域幅拡大やこれら周辺デバイス自体の性能向上(高速化・低消費電力化)によって、SiP全体の性能向上が期待できる。

さらに、先端半導体の製造において今後重要性が増すと考えられる分野の材料・部材に関する技術を開発する。

具体的な開発テーマは、以下の通りとする。

(a) 先端半導体の前工程技術 (More Moore 技術) の開発 (助成)

先端半導体は更なる微細化が進展し、IEEE の IRDS<sup>TM</sup>2020 によると、プロセスノードは 2022 年に 3nm ノード、2025 年に 2.1nm、さらにその先では 2028 年、2031 年、2034 年にそれぞれ 1.5nm、1.0nm、0.7nm へと進むことが予想されている。そして、微細化の進展に伴い、トランジスタ構造は FinFET からナノシートを活用した三次元構造や GAA (Gate All Around) 構造へと変化、チャネル材料はシリコンゲルマニウム (SiGe) やゲルマニウム (Ge)、2 次元材料が多用されるようになり、配線材料も銅 (Cu) からルテニウム (Ru) へ変化する等、新構造と新材料を用いたトランジスタへと変化していく。このため、半導体製造・プロセス技術全般について新規技術開発や抜本的な性能向上が必要となる。

そこで、2nm 以降のプロセスノードの先端半導体において求められる高性能な露光・微細加工技術、成膜技術、アニール技術、エッチング技術、洗浄技術等のうち、特に新規開発や大幅な性能向上が必要となる製造・プロセス技術等（以下の開発対象技術全てを含める必要は無い。）を開発するとともに、パイロットラインの構築等を通じて、微細加工を施した実ウェハーによる製造装置の評価・検証を実施し、国内に無い先端性を持つロジック半導体の製造技術を確立する。

＜開発対象<sup>※1</sup>＞

- 露光・微細加工技術（微細な三次元構造の加工・形成技術等）

- 成膜技術（新材料チャネル、新材料配線、極薄膜／多層積層技術等）

- 配線技術（微細孔への埋め込み、裏面配線等）

- アニール技術（極薄膜対応技術、低熱履歴化技術等）

- エッチング技術（新材料、新構造のエッチング技術等）

- 洗浄技術（微粒子／メタル濃度の極低濃度化等）

- 革新的な高生産性プロセス技術

- 先端半導体と一体として機能するメモリ（キャッシュ用途等）の製造技術

- その他の重要な製造・プロセス技術

＜開発目標＞

- 次世代（2.1nm や 1.5nm ノード<sup>※2</sup>）の先端半導体製造・プロセスにおいて求められる基本性能を具備する製造・プロセス技術を開発し、評価・検証すること。（製造装置としての検証であり、先端半導体の実工場ラインでの検証までは必須としない。）

なお、さらに先端的な次々世代（1.0nm ノード以降<sup>※3</sup>）の先端半導体において求められる技術開発を含める場合は、要素技術開発あるいは初期的な試作機の開発まで終えること。

※1 括弧内は開発対象の技術例。

※2 IRDS<sup>TM</sup>2020 中の「Logic industry “Node Range” labeling (nm)」における「2.1」及び「1.5」を意味する。

※3 IRDS<sup>TM</sup>2020 中の「Logic industry “Node Range” labeling (nm)」における「1.0 eq」以降を意味する。

実施に際しては、事業成果の最大化のため、必要に応じ、本事業で構築するパイロットライン等は半導体の装置・部材メーカー等にも利用してもらい、そのフィードバックを得て更なる改善を行う等、可能な範囲でオープンイノベーションを推進するとともに、ユーザー企業・機関との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。

なお、開発の実施に当たっては、個々の製造技術単体の開発に留まらず、先端半導体製造工場へ高い適用性を確保するため、開発期間全体を通じて、技術の将来的なユーザーにあたるファウンドリー企業や半導体デバイスメーカー等との連携体制を積極的に構築し、最

新のユーザーニーズを踏まえ、必要に応じて、研究開発内容を柔軟に見直す等、成果の最大化に取り組むこととする。

(b) 先端半導体の後工程技術 (More than Moore 技術) の開発 (助成)

ポスト 5G 情報通信システムにおけるクラウド・MEC サーバー等の高性能コンピューティング、及びエッジコンピューティングでは、多様なアプリケーションに対応するためには、ロジック半導体の微細化の進展による高性能化はもとより、ロジック半導体と周辺デバイス（メモリ、センサー、AI チップ、RF 等）とを单一パッケージに統合する、2 次元高密度実装や 3 次元（2. xD、3D<sup>※</sup>）実装技術の進展が不可欠である。特に、高性能コンピューティング向け実装技術ではパッケージ基板の大面積化や 3 次元・高密度実装向けの新規の材料、製造・プロセス技術、アセンブリー・パッケージング技術等が求められ、エッジコンピューティング向け実装技術では、小型・低実装面積での高性能化、高機能化、低消費電力化を実現可能な製造・プロセス技術が求められるとともに、合わせてこれらの実装技術を支える共通基盤技術が求められる。

そこで、先端半導体において求められる、(b1) 高性能コンピューティング向け実装技術、(b2) エッジコンピューティング向け実装技術、(b3) 実装共通基盤技術（開発にあたり以下の開発対象に記載の技術全てを含めることは必須では無い。）、及び (b4) 有機 RDL インターポーラの微細化製造技術の開発を実施し、これにより国内に無い先端性を持つ半導体の後工程技術 (More than Moore 技術) を確立する。

※ 3D とは、ロジック・オン・ロジックやメモリ・オン・ロジックなどダイ同士の積層を意味する。

(b1) 高性能コンピューティング向け実装技術

＜開発対象＞

- 先端半導体の実装に必要となるパッケージ基板の大面積化、3 次元（2. xD、3D）・高密度実装向け材料技術、製造装置等の開発とこれらに対応するアセンブリー・パッケージング技術、その他の関連する重要技術。

＜開発目標＞

- 高性能コンピューティング向けの先端半導体（5nm ノード以降<sup>※1</sup>）の実装・パッケージング工程において求められる基本性能を具備する材料、製造プロセス技術、実装技術等を開発し、パイロットラインの構築等を通じて、評価・検証すること。開発に当たっては、先端半導体の実工場ラインへの適用を見据えて、歩留まり向上やシステムとしての性能向上等を実現すること。

※ IRDS<sup>TM</sup>2020 中の「Logic industry “Node Range” labeling (nm)」における「5」以降を意味する。

(b2) エッジコンピューティング向け実装技術

＜開発対象＞

- 大きさや技術ノードが異なる複数の半導体（ロジック、AI チップ、メモリ、センサー、RF 等）を 3 次元積層する革新的な貼り合わせ技術、微細化が進んだ半導体間を接続する狭ピッチ接続技術、広帯域・低損失インターフェクト技術、積層対象の半導体の高性能化、その他の関連する重要技術。

＜開発目標＞

- エッジコンピューティング向けの先端半導体の 3 次元実装技術において求められる基本性能（小型・低背化、低消費電力、高集積、多機能等）を具備する 3 次元実装技術を開発し、パイロットラインの構築等を通じて、評価・検証すること。開発に当たっては、3 次元実装に係る実工場ラインへの適用を見据えて、歩留まり向上やシステムとしての性能向上等を実現すること。

(b3) 実装共通基盤技術

＜開発対象＞

- ・高性能コンピューティングやエッジコンピューティング向けの先端半導体実装技術の実装技術を支える共通的な基盤技術のうち、特に新規開発や大幅な性能向上が必要となる以下の技術。

- 実装部材（例：パッケージ基板、封止材、放熱材、研磨剤等）

- 実装部材を構成する材料（例：コア材、絶縁材料・フィルム、接合材料等）

- 実装部材の製造・アセンブリー技術（例：パッケージ基板製造技術等）

- ＜開発目標＞

- ・先端半導体実装技術（5nm ノード以降）において求められる基本性能を具備する基盤技術を開発し、3次元実装に係る実工場ラインへの適用を見据えて、実用性の評価・検証をすること。（部材・材料、製造装置としての検証であり、先端半導体の実工場ラインでの検証までは必須としない。）

実施に際しては、事業成果の最大化のため、半導体装置・部材メーカー、学術機関等との共同開発やその他の連携を推進する等、可能な範囲でオープンイノベーションを推進するとともに、必要に応じ、本事業で構築するパイロットライン等の活用による評価・検証、ユーザー企業・機関との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。

#### （b4）有機 RDL インターポーラの微細化製造技術開発【GX】

＜開発対象＞

先端半導体の後工程における高密度実装を実現する有機 RDL（Redistribution Layer）インターポーラの微細化製造技術開発

＜開発目標＞

以下の性能を満たす有機インターポーラを開発する。

- ・製造時の基板面積：250000mm<sup>2</sup>以上

- ・再配線層ピッチ（Line & Space）：0.5um/0.5um 以下

- ・インターポーラ上の伝送における消費電力が研究開発開始時点の技術と比較して 50% 以下

#### （c）露光周辺技術開発（助成）

先端半導体の更なる微細化が進展する中で、特に微細化において重要な露光工程においては、EUV（極端紫外線）光を用いた EUV 露光装置が注目されている。EUV 露光装置においては、光源の波長が 13.5nm と従来の露光装置と比較して短いことから、その周辺材料・部材もそれに対応した技術が必要となる。

ペリクルは、異物がフォトマスクに直接付着することを防ぐために使用される保護膜であるが、これまで EUV 光に対して十分な透過率を有するペリクルは開発されていない。現時点で EUV 露光装置を用いた先端半導体の製造はペリクル無しで行われる場合があり、これがフォトマスクの寿命に影響を与え、高コストの一因となっていると考えられる。そこで、EUV 露光装置向けのペリクルを開発する。

また、微細化はマルチパターニングによっても実現が可能である一方、マルチパターニングは露光時間やマスク枚数の増加により高コスト化の要因となるため、可能な限り少ない露光回数であることが望ましい。そのため、EUV 露光装置では、より微細なパターニングを行うため開口数（NA）を向上させる等の研究開発が行われており、フォトレジストもそれに対応した高い分解能が求められている。そこで、微細化に対応した次世代フォトレジストの開発を行う。

#### （c1）高出力 EUV 露光装置向けペリクル開発【GX】

＜開発対象＞

- ・高い EUV 透過率や耐久性を有し、次世代 EUV 露光装置に適用可能なペリクル

＜開発目標＞

- 以下の性能を両立するペリクルを開発すること。

- －EUV 光透過率：95%以上

- －耐久性：EUV 露光出力 1000W 下において、露光寿命 ウェハー換算 1 万枚以上

(露光量：ウェハー 1 枚当たり 30mJ/cm<sup>2</sup>、96fields)

- 上記によって露光にかかる電力消費量を 15%以上削減すること。

(c2) EUV 露光装置向け次世代フォトトレジスト技術開発

<開発対象>

- EUV 露光プロセス向けの次世代フォトトレジスト。

<開発目標>

- 1.5nm ノード※以降の先端半導体製造に適用される高 NA EUV 露光プロセスにおいて必要となる基本的な性能を有すること。

※ IRDS<sup>TM</sup>2020 中の「Logic industry “Node Range” labeling (nm)」における「1.5」を意味する。

(d) 国際連携による次世代半導体製造技術開発（委託、助成）

次世代半導体製造技術の確立のためには、国内にない技術や知見を活用することが必要であり、国際連携が不可欠である。

2025 年以降に最先端になると予想されている 2nm ノードでは、GAA (Gate All Around) 構造や新材料の導入などが必要である。こうした次世代半導体の生産能力を確保するためには、各プロセス技術開発や製造装置の評価検証に加えて、所望のデバイス特性や歩留まり・コストを達成する必要がある。そのためには、微細構造を実現するために必須となる最先端の露光技術によって GAA 構造を実現するための製造技術や、それら技術で実現するデバイスの検証・評価技術等が不可欠である。一方で、これらの技術のうち、一部が現在国内には無い。そこで、2nm ノードの最先端半導体で求められる基盤的な技術を国際連携により確保した上で、2nm ノードで実現しうるトランジスタ集積度と信頼性を達成する製造技術を開発し、現在国内に無い最先端ロジック半導体の製造技術を確立する。

エレクトロニクス技術とフォトニクス技術を組み合わせた光電融合技術は、高速性・低損失性を有し、高性能かつ省エネな計算基盤の実現に重要な技術である。光電変換デバイスで接続された CPU/GPU/メモリ等複数の回路チップを半導体パッケージ内へ実装する光チップレット実装技術によって、CPU やメモリ、xPU 等の計算資源を、電気配線を介さずに、直接・遠距離まで高速・低損失に接続できる。本開発では光チップレット実装技術を開発すると共に、本技術によりパッケージ内で複数の回路チップが光で接続された半導体デバイスの開発を行い、光ディスアグリゲーテッドコンピューティング等、新規なアーキテクチャに基づくサーバー等の実現に向けた技術を確立する。

このような光電融合技術がもたらす高速性・低遅延性をソフトから有効活用するには、計算基盤技術による支援が不可欠である。本開発では、エッジ拠点や地域クラウド拠点に設置されたサーバー間のデータ転送やデータ処理を、確定遅延で最適に処理可能にするとともに、サーバー内ではプロセッサ群とメモリを分離し、プロセッサ間でメモリプールを共有することでプロセッサ間のデータ転送を削減するなど、低遅延化と遅延確定性の向上を可能とする、計算基盤技術を開発する。これにより、リソース量及びデータ転送量を削減することで計算基盤全体の省電力化を実現する。その際、光電融合デバイスや共有メモリ等と相互に連携して上記システムをくみ上げる必要があるが、光電融合デバイスと同一パッケージ内に実装する高性能 CPU 等の先端半導体メーカーは現在国内には無いため、国際連携により必要な仕様等の知見を確保しながら、本技術における共通基盤技術の開発を進める。

半導体チップの高性能化のためには微細化は有効な手段であるが、同時にパッケージング製造技術の高度化も重要。特に、高性能化の実現に向けて大型化する半導体チップを、機能毎に分割をして、微細配線で再接続をするチップレット実装技術は、高性能化と低消費電力化、さらには高歩留まりの実現に向けて必須となる技術。こうしたパッケージング製造を実現するためには、3 次元 (2. xD, 3D) 実装技術やそうした実装技術のさらなる高度

化に加えて、その周辺材料の高度化も必要。また、チップレット実装においては、アプリケーション毎に構成チップが変わるため、アプリケーション毎に最適化したチップレット実装を実現する必要があり、ウェハー工程における PDK と同様の概念の設計環境構築が必要。こうした要求を満たすための高度なパッケージング設計・製造技術を確立する。

なお、助成事業については国際連携を必ずしも要件としない。

(d1) 高集積最先端ロジック半導体の製造技術開発

＜開発対象＞

- 最先端半導体に必要なトランジスタ集積度と信頼性を達成するロジック半導体製造技術。

＜開発目標＞

- テストチップにおいて、以下の SRAM を GAA 構造により作り、動作を実証すること。また、動作寿命予測に資する高温動作寿命試験<sup>※1</sup>を実施すること。

- ビットセル面積 :  $0.0187 \mu\text{m}^2$  以下<sup>※2</sup>

- アレイ記憶容量 : 128 Mbit 以上

- ※1 IEC 等に準拠すること。また、ターゲットとする用途に応じた測定条件・目標値を提案時に設定すること。

- ※2 IRDS™ 2022 UPDATE MORE MOORE に記載の 2nm ノードに準拠。

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

- ※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(d2) 光電融合に係る実装技術および確定遅延コンピューティング基盤技術開発【GX】

以下、(d2-1)～(d2-3) の実施においては、双方連携しながら取り組むこと。

(d2-1) 光チップレット実装技術

＜開発対象＞

- パッケージ内で、CPU/GPU/メモリ等複数の回路チップ間が、光電変換デバイスと導波路等で接続された、光チップレット実装技術による半導体デバイス

＜開発目標＞

- 帯域密度として 1Tbps/mm 以上であること。また、光チップレット実装技術を適用して開発した、半導体デバイスの単位通信量あたりの電力が、研究開発開始時点での普及している同等の技術、あるいは製品に比べて 40% 以上削減されていること。

- ※ 必要に応じて提案者にて具体的な目標値を提案時に併せて設定すること。

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

- ※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(d2-2) 光電融合インターフェイスメモリモジュール技術

＜開発対象＞

- 光ディスアグリゲーテッドコンピューティングを実現する、光電変換デバイスをインターフェイスとした、メモリモジュール。

＜開発目標＞

- 光電変換デバイスをインターフェイスとしたメモリモジュールの光通信速度が 512Gbps 以上（物理速度）の帯域であること。また、消費電力が研究開発開始時点で普及している同等の技術あるいは製品に比べて 30%以上削減されていること。

- ※ 光通信速度の目標は、PCIe Gen6 に基づく CXL メモリを想定した。なお、必要に応じてディスアグリゲーテッドコンピューティングを実現するための具体的な目標値を上記に併せて提案時に設定すること。

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

- ※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(d2-3) 確定遅延コンピューティング基盤技術

＜開発対象＞

- 光電融合技術および光ネットワーク技術の高速性・低遅延性を活用した確定遅延コンピューティング基盤技術。

＜開発目標＞

- 研究開発終了時点で想定されるユースケースの遅延要件を基に、開発技術の有効性を検証：1 件以上

- ※ 提案者にて具体的なユースケース、電力削減を含む目標値を提案時に設定すること。

(d3) Beyond 2nm 世代向け半導体技術開発

＜開発対象<sup>※1</sup>＞

- Beyond 2nm 半導体製造に向けた技術開発

- 短 TAT 半導体製造に向けた技術開発

- ※ 対象例：露光・微細加工技術、成膜技術、配線技術、アニール技術、エッチング技術、洗浄技術、革新的な高生産性プロセス技術

＜開発目標＞

- Beyond 2nm 半導体製造に向けた技術開発については、Beyond 2nm 世代半導体に必要な製造技術及び材料技術等に関して、背景とともに示した上で、本研究開発で実現する目標を定量的に定め、実証すること。

- 短 TAT 半導体製造に向けた技術開発については、短 TAT 化に向けたボトルネック製造工程に関して、背景とともに示した上で、本研究開発で実現する目標を定量的に定め、実証すること。

＜応募条件＞

- 開発対象の両方を含むこと。

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

- ※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(d4) 2nm 世代半導体のチップレット・パッケージ設計・製造技術開発

＜開発対象＞

- 2nm 世代半導体を含む 3 次元（2. xD, 3D）パッケージ製造技術開発

- アプリケーション毎に最適な高効率・高性能チップレット・パッケージを実現するた

## めの設計技術開発

### ＜開発目標＞

- ・高性能化・省エネ化のために以下の製造技術を確立すること

- ・インターポーラ面積 : 6640mm<sup>2</sup>

- ・インターポーラの端子ピッチ : 25um

- ・再配線層のピッチ (Line & Space) : 2um/2um

- ・ハイブリッドボンディング (チップ・オン・ウェハー) の端子ピッチ : 3um

※提案時に開発終了時点での省エネ化見通し及び根拠を示すこと

- ・Known Good Die (KGD) 選別手法の提案

- ・信頼性実証

※提案時に標準規格並びにその根拠を示すこと

- ・アプリケーション毎に最適なチップレット・パッケージを設計するためのデザインキットを構築

※少なくとも、HBM 並びに UCIe に準拠したライブラリを整備すること

### ＜応募条件＞

- ・海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

※「海外企業等」として、提案者の親会社、子会社は対象外とする。

- ・上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

### (d5) 先端パッケージング等を含む後工程高度化プラットフォームの構築

#### (d5-1) 先端パッケージング等を含む後工程の自動化にかかる技術開発

### ＜開発対象＞

- ・先端パッケージング製造の自動化にかかる技術開発

- ・製造自動化に伴う生産効率改善の実証

### ＜開発目標＞

- ・実装工程の製造自動化に向けた製造装置及び搬送装置の標準化

- ・製造自動化による生産効率の 30%改善

### ＜応募条件＞

標準化に取り組むにあたり、グローバルに連携をして進めること。

### (d6) 先端半導体の後工程における光実装を可能とするパッケージング技術開発【GX】

#### ＜開発対象＞

- ・有機 RDL インターポーラへの光配線導入を含む後工程における光実装技術及びそれに必要なハイブリッドボンディング技術

#### ＜開発目標＞

- ・以下の性能を満たす技術を開発し、後工程における光実装に係る実工場ラインへの適用を見据えて、実用性の評価・検証を実施すること。

- －帯域密度 : 10Tbps/mm 以上

- －有機 RDL インターポーラとチップレット接合 (ハイブリッドボンディング) における端子ピッチ : 6um 以下

- －光電変換デバイスと導波路等における伝送量あたりの消費電力の削減割合 : 研究開発開始時点の技術と比較して 40%以上

実施に際しては、事業成果の最大化のため、半導体装置・部材メーカー、学術機関等と

の共同開発やその他の連携を推進する等、可能な範囲でオープンイノベーションを推進すること。また、半導体装置・部材メーカー等が評価・検証に活用可能なパイロットライン等を本事業で構築した上で、その利用を促進するとともに、ユーザー企業・機関との連携、国際連携の推進、他の政府予算事業との連携によるシナジー効果の創出、成果報告会・ワークショップの開催等も行う。

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

※「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(e) 次世代メモリ技術開発（助成）

ポスト5G情報通信システムにおいては、生成されるデータが極めて大量になることが見込まれている。それに伴い、データセンタにおいてはデータ処理量が増加し、電力消費量が増大することが予想されている。また、近年導入が進んでいるAI処理に必要な大量の計算処理を短時間で実行するため、プロセッサの高性能化と共に、プロセッサとの間で高速にデータ転送を行う広帯域メモリ（HBM）の重要性が高まっている。今後さらにAIの需要は増大していくと考えられ、これに伴いメモリにはさらなる広帯域化が求められると共にメモリ転送に伴う電力消費が膨大になると考えられるため低消費電力でこれを実現する技術が求められる。

そこで、広帯域かつ低消費電力なHBM製造技術や革新メモリの製造技術の開発及び今後拡大していくことが想定されるエッジ領域におけるAI半導体向けメモリ技術の開発を行う。

(e1) 次世代広帯域・低消費電力HBMの製造技術開発【GX】

＜開発対象＞

- 次世代広帯域・低消費電力HBMの製造技術。

＜開発目標＞

- 以下の性能要件を満たした上で、一般的なメモリに求められる信頼性要件を満たすこと。

- メモリ密度 : 0.5Gbit/mm<sup>2</sup>以上

- ダイあたり容量 : 32Gbit 以上

- 積層数 : 12層以上

- 帯域 : 2TB/s 以上

- 伝送量あたりの消費電力の削減割合 : 研究開発開始時点の製品と比較して 30%以上

(e2) 革新メモリの製造技術開発【GX】

＜開発対象＞

- DRAMとNANDの中間的性質を有する革新メモリの製造技術

＜開発目標＞

- 以下の性能要件を満たすメモリ製造技術の開発及び開発したメモリにおいて一般的なメモリに求められる信頼性要件を満たすこと。

- 読み出し速度 : 50nsec から 1usec の間

- メモリ密度 : 0.6Gbit/mm<sup>2</sup>以上

- 消費電力 : DRAMと比較して平均消費電力量/bit を 10%以上低減

- インターフェイス速度 : 4.8Gbps 以上

### (e3) エッジ向け AI メモリ設計・製造技術開発【GX】

#### ＜開発対象＞

- エッジ向け AI メモリの設計及び製造技術

#### ＜開発目標＞ ※なお、比較対象はいずれも本プロジェクト提案時点の最新製品

- コンピューティングの省エネ化、エッジ領域での AI 計算を実施するために、以下の性能要件を満たすことが出来る技術開発を実施すること。

- 以下の性能を実現するとともに、一般的なメモリに求められる信頼性要件を満たすこと。

—メモリ密度 : 0.75Gbit/mm<sup>2</sup> 以上

—メモリ用 CMOS の遅延時間短縮 : 35% 以上

- エッジ領域では用途が多岐にわたり、PC やエッジサーバーなど、比較的のサイズに余裕があり性能を重視する用途や、モバイルなどサイズ制約があり熱的な制約がある用途なども想定される。

そこで、主に以下二つのケースを想定して、上記メモリを用いて、それぞれに適したメモリの設計・製造技術の開発を実施する。

- (1) エッジ端末において最大ピーク時の帯域を重視するメモリ

(ア) プロセッサーメモリ間のデータ転送時のエネルギー効率 (pJ/bit) を 15 倍以上改善

(イ) メモリのエネルギー効率 (pJ/Byte) が同等以上改善

(ウ) ピーク時の帯域が 500GB/s 以上

- (2) エッジ端末において常時の帯域を重視するメモリ

(ア) プロセッサーメモリ間のデータ転送時のエネルギー効率 (pJ/bit) が同等以上改善

(イ) メモリのエネルギー効率 (pJ/Byte) を 40% 改善

(ウ) 高温時 (85°C 程度) を含む動作時の帯域が 200GB/s 以上

### (e4) 高メモリ密度・広帯域・低消費電力な革新的メモリの製造技術開発【GX】

#### ＜開発対象＞

- 高い放熱性を有することにより、高メモリ密度・広帯域・低消費電力の実現を可能とする革新的メモリの製造技術

#### ＜開発目標＞

- 以下の性能要件を満たした上で、一般的なメモリに求められる信頼性要件を満たすこと。

—メモリ密度 : 10Gbit/mm<sup>2</sup> 以上

—帯域密度 (xPU に対応する辺の長さで規格化) : 450GB/s/mm 以上

—メモリ温度 : AI 性能を評価するための業界標準ベンチマーク (MLPerf 等) を実行したときに 95°C を超えないこと

—伝送量あたりの消費電力の削減割合 : 提案時点の製品 (HBM) と比較して 30% 以上

- UCIe 等の標準規格に準拠したライブラリを開発すること。

### (f) 次世代半導体設計技術開発（委託、助成）

次世代半導体産業基盤の整備のためには、製造技術の開発を進めると同時に、次世代半導体を使う側の取組、いわゆる設計技術の開発も進める必要がある。

これまで、汎用の CPU、GPU の上でソフトウェアによる差別化が主流であったが、性能と消費電力の両立に向けて、用途毎に最適化した専用半導体と専用ソフトの組み合わせが今後の主流になると想定される。

こうした変化はクラウド側でも起きつつあるが、用途が多岐にわたるエッジ側においてより顕著であると想定されるため、我が国が強みを有するエッジ側の用途である自動車、ロボティクスなど産業機器等を中心として、次世代半導体設計基盤の構築を進めることが

重要。

そこで、ユースケースを見据えた次世代半導体チップ設計等に関して、国際連携なども活用しながら技術開発を進める。

(f1) 2nm 世代半導体チップ設計技術開発

＜開発対象＞

- 2nm 世代半導体の製造技術を活用した AI 半導体設計

＜開発目標＞

- 提案時点で主に使用されている GPU と比較して、開発する半導体の性能／電力が 5 倍以上向上していること。

- 推論を対象とする業界標準ベンチマーク (MLPerf Inference Benchmark 等) を実行できること。

- 業界標準の AI 開発環境フレームワーク (TensorFlow、Pytorch、ONNX 等) に連携し、自動的にコード最適化を行う環境を提供すること。

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

(f2) 自動車用高性能コンピュータ向け最先端 SoC 技術開発

＜開発対象＞

- 2030 年頃の車両搭載に求められる自動車用最先端 SoC の設計・開発・実証

＜開発目標＞

- 2030 年頃の車両搭載に想定される車両の電子プラットフォーム、ECU 統合機能、ソフトウェア階層構造に基づいた半導体の仕様策定

- 上記仕様に基づいた最先端 SoC の設計・開発

- プロトタイプを用いた性能実証

- 車載グレード (AEC 規格等) の信頼性検証

＜応募条件＞

- 海外企業等と共同で研究開発事業を実施する、または、研究開発内容に対するアドバイザ等として海外企業等が参画すること。

※ 「海外企業等」として、提案者の親会社、子会社は対象外とする。

- 上記のほか、「海外企業等」の属する国・地域と、日本政府との政府間交渉により、同国・地域の法令等を踏まえて、追加で条件が付される可能性がある。

＜特記事項＞

- 本研究開発テーマにおいては、ステージゲート審査は少なくとも 2 回実施することとし、1 回目のステージゲート審査は電子プラットフォーム、ECU 統合機能、ソフトウェア階層構造の要件定義について報告・審議を行う。

- 1 回目のステージゲート審査の際に、後年度の取り組み内容および開発費について審議を行う。

(f3) 通信用 AI 半導体設計技術開発【GX】

＜開発対象＞

- 通信用 AI 半導体設計技術開発

＜開発目標＞

- AI 处理性能/電力消費量が現在汎用的に用いられている半導体と比べて 5 倍以上であること

- 上記半導体について DU 機器に組み込んで性能実証を行うこと

(f4) チップレット設計プラットフォーム構築に向けた技術開発【GX】(委託)

(f4-1) プラットフォーム構築に向けた要素チップ及び実装技術開発【GX】

＜開発対象＞

- SoC チップレット、FPGA チップレット、専用チップレット向け基盤回路等を有するチップレット型カスタム SoC 設計プラットフォームの開発

＜開発目標＞

- カスタム SoC の設計期間を 30% 以上削減すること

- 協力機関等の専用チップレットを搭載したカスタム SoC を構築し動作を実証すること

(f5) 低遅延・超低消費電力 AI アクセラレータ開発【GX】

＜開発対象＞

- 2nm 世代の半導体製造技術を活用した低遅延・低消費電力の推論用 AI アクセラレータの開発

＜開発目標＞

- 開発した半導体をシステムに搭載し、以下のシステム性能の検証を行うこと

※数十 B 以上のパラメータを有する大規模言語モデルにおいて、現在利用可能な GPU と比較して、トークン間遅延を極小化しつつ、電力あたりの処理性能 10 倍以上を実現すること

- 比較対象の半導体については提案書で根拠も含めて明記すること

- 業界標準の AI 開発フレームワーク (PyTorch、ONNX など) と互換性のあるソフトウェアスタックが整備されていること

(f6) 画像処理用半導体の設計技術開発【GX】

＜開発対象＞

- 2nm 世代の製造技術を活用した画像処理用半導体の設計技術開発

- 上記チップは、異種ノードの半導体チップを 1 つのパッケージ内に集積したチップレット技術を適用した半導体の設計技術開発

＜開発目標＞

- 以下の条件のすべてを同時に満たすシステムを開発すること

- ソフトウェアを開発し、システムで動作確認が出来ること

- 現行世代品に対して 5 倍以上の電力効率 (TOPS/W) を持つ AI 処理性能を有すること

- ※比較対象の半導体、試験条件については提案書で根拠も含めて明記すること

(g) 先端半導体周辺デバイス設計・製造技術 (助成)

先端半導体を自動車、通信機、ロボット、IoT システム等さまざまな機器に組み込んで活用するには、先端半導体チップ以外の周辺デバイスにも、高度なデータ処理能力に対応した性能と、それぞれの機器の使用環境に耐えうる信頼性が要求される。

自動車の電動化や自動運転、生成 AI 等の活用が見込まれる中、統合車載制御システムの車載半導体にも、先端半導体の活用が必要になりつつある。このため、統合車載制御システムにおいては、車載半導体間のデータ伝送量と伝送速度の増大が予想される。現在の電気配線を通じたデータ伝送では、消費電力の増大、信号強度の劣化、電磁ノイズによる信号の乱れが問題となってくる。そこで、上述の問題を解決可能な、低消費電力、高速、高

信頼性データ伝送デバイスを開発すると共に、開発デバイスを車載制御システムに実装してデータ伝送の実証、及び信頼性評価までを行う。

(g1) 車載半導体間データ伝送技術【GX】

＜開発対象＞

- ・ 統合車載制御システムにおいて、車載半導体間を接続する、低消費電力、高速、高信頼性データ伝送デバイスの開発と信頼性試験

- ・ 開発したデバイスを実装した、統合車載制御システム上での実証試験、及び信頼性試験（自動車企業あるいはTier1の自動車部品企業と協力のもと実施）

＜開発目標＞

- ・ 統合車載制御システムに搭載され、車載半導体間のデータを伝送するための、以下の性能を満たす、低消費電力、高速、高信頼性データ伝送デバイスを開発すること。

- － 伝送速度：32Gbps、4ch以上（PCIe5.0以降）

- － 伝送の消費電力：車載半導体間距離0.3m以上において、現状の電気配線と比較して、70%以上削減

- ・ 開発デバイスに対応した、車載部品向けの信頼性試験（AEC規格等）、車載EMC試験（CISPR規格等）を実施し、下記の性能を満たすことを示すこと。

- － 温度環境耐性：温度範囲-40°C～105°Cで動作、かつコールドスタート動作

- － 湿度・耐水環境耐性：水滴下で動作、かつ80%、85°Cの環境で1000h動作

- － 耐振動性：60Gの振動に耐性を示す

- － 電磁ノイズ耐性：過渡電圧、電磁ノイズ耐性を示す

- ・ 開発デバイスを統合車載制御システムに搭載し、車載部品向けの長期信頼性試験（AEC規格等）を実施し、下記の性能を満たすことを示すこと。

- － 長期信頼性：10万時間、10～40万km

(h) 先端半導体計測・分析技術開発（助成）

先端半導体では新しい材料やプロセスが導入され、3次元化など構造の複雑化も進展していくと考えられている。例えば、先端ロジック半導体においては、チャネルを取り囲むようにゲート電極を形成したGAA構造、P型FETとN型FETが縦に積層されたCFET、裏面電源供給網（Backside Power Delivery Network）など、複雑な3次元構造の素子が研究開発されている。このような先端半導体において性能実証や歩留まり向上を達成するためには、製造技術だけでなく素子の計測・分析技術も併せて必要となる。

新規の先端ロジック半導体の開発を迅速に行うためには、3次元構造に関する様々なデータを高精度かつ高速に計測し、高度なシミュレーションと統合した分析技術の構築が求められる。そこで本テーマでは、新しいプロセスや材料を用いて製造された複雑な3次元ロジックデバイスを開発するための半導体層の結晶歪み、ゲート絶縁膜の状態、微細配線の形状や組成等を計測・分析することができる技術を開発する。

(h1) 先端ロジック半導体向け3次元非破壊計測技術開発

＜開発対象＞

先端半導体の微細かつ複雑な構造を高精度かつ高速に測定可能な非破壊計測※・分析技術開発

※ 集束イオンビーム装置などにより分析面を露出させずに行う計測・分析のこと（計測・分析前にウエハをチップ単位に分割することは妨げない。）

＜開発目標＞

1.0nmノード※1の先端ロジック半導体におけるチャネル結晶の歪み、ゲート絶縁膜の品質、微細配線の形状・組成に係る非破壊計測・分析技術を開発する。

#### (チャネル結晶歪みの分析)

トランジスタ毎に独立に歪み量を分析するため、以下を同時に満たす非破壊計測・分析技術を開発する。

- ・面内分解能がチャネルピッチ※2の半分以下

- ・歪み分解能が0.1%以下

#### (ゲート絶縁膜品質の分析)

複数の絶縁膜が積層された構造において、元素組成やポテンシャルといった膜品質情報を深さ方向で取得することが重要であるが、従来の一般的な分析手法では表層の情報しか取得できず、積層膜の下層からの情報を取得するためにはエッチング処理が必要であり、膜品質の変質が懸念されることから、以下を満たす非破壊計測・分析技術を開発する。

- ・複数の絶縁膜を積層した構造において、膜品質情報の深さ分解能が1nm以下

#### (微細配線の形状・組成の分析)

従来の方法では走査型電子顕微鏡(SEM)や透過型電子顕微鏡(TEM)を使用するが、広範囲の中から不良個所を特定した上での分析は不可能であることから、以下2種の非破壊計測・分析技術((1)及び(2))を開発する。

##### (1) 以下を同時に満たす、配線故障のため形状分析技術：

- ・空間分解能は最小配線ピッチの1/4以下

- ・裏面電源供給網(BSPDN)を含む全配線層の配線分析を行うため、測定領域10um x 10um x 30um(厚さ)以上

##### (2) 以下を同時に満たす、微細領域に形成した配線金属の組成分析技術：

- ・空間分解能は最小配線ピッチ以下

- ・BSPDNを含む全配線層の配線分析を行うため、測定領域10um x 10um x 30um(厚さ)以上

※1 IRDS<sup>TM</sup>2024 More Moore中の「Logic industry “Node Range” Labeling」における“A10 eq”を意味する。

※2 IRDS<sup>TM</sup>2024 More Moore中の「Device lateral pitch」を意味する。

### ③先導研究(委託、助成)

研究開発項目①②に関係するものであって、ポスト5Gでは実用化に至らない可能性があるものの、ポスト5Gの後半から5Gの次の通信世代(以下、「ポスト5G後半以降」)にかけて有望と考えられる技術課題について、先導的な研究開発に取り組む。研究開発項目①に関係する技術課題は委託事業、研究開発項目②に関係する技術課題は助成事業として実施する。

本研究開発項目では、研究開発終了時点において、実用化を前提とした研究開発への移行に向けた根拠データの取得等により、技術の確立の見通しを付けることを開発目標とする。また、開発対象は、ポスト5G後半以降にかけて情報通信システムに適用され、一定の市場シェア獲得のポテンシャルを有し、我が国の国民生活や経済、産業等への波及効果が期待される技術とする。

研究開発項目①に関係する具体的な開発テーマとして想定する開発技術は、(a)～(e)についてそれぞれ以下の通りとし、これら開発テーマ毎に記載の開発対象の全てあるいは一部について研究開発を行う。

得られた研究開発成果については、5G将来仕様となる3GPP等の標準化団体との連携を図ることとし、評価手法の提案、データの提供、標準化活動等を積極的に行う。

#### (a) ネットワーク関連技術

ポスト5G後半以降のネットワークにおいては、5Gの10倍あるいは100倍の高速化・大容量化・低遅延化・多数同時接続等に加え、超低消費電力化、高信頼性、自律性、拡

張性、などの新たな性能が求められるとともに、多種多様の新たなサービスの要求に応じたQoS (Quality of Service) が求められるため、仮想化技術やAI技術の高度化等による高速、高機能、柔軟かつ信頼性の高いネットワークのリソース分配制御技術や管理、運用技術、高精度な同期技術、クラウドサーバーやMECサーバーの低消費電力化技術が重要となる。また、今後、量子コンピュータ等の新原理に基づく高速計算機の登場が予想され、社会基盤の通信システムについても堅牢性が高くセキュアな通信が求められる。

これらに対応すべく、本開発項目では、多種多様なサービスに対応可能なコアネットワークからアクセスネットワーク、MEC、基地局、端末まで、ネットワーク全体（あるいは一部）を統合的に管理する技術や、エンドツーエンドでのデータ到達時間の超低遅延を実現する技術、安全性の担保されたオープンソースのソフトウェア基盤技術、サーバーの超低消費電力化技術の開発等を行う。さらに、今後、新原理に基づく高速計算機等でも破ることができない、堅牢性の高いセキュアな通信を実現する暗号通信技術等についても開発を行う。

| 開発対象                               | 開発技術例                                                                                                                                                                                            |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ネットワーク統合管理技術（超高信頼性）                | 様々な不確実性を伴う状況下においても高信頼のネットワークやアプリケーションを実現するため、クラウド、NW、MEC、端末・エッジに至るまで、各機器のリソース情報を把握し、処理の細分化、動的な処理の移行や最適配置、タスク・リソースの最適分配等を可能とする統合管理技術の開発、AI技術の高度な利用によるSDN (Software Defined Network) 制御、運用自動化技術の開発 |

| リアルタイム制御技術（超低遅延性）                  | 多種多様なリアルタイム性が求められる用途における要求を満たすため、有線区間、無線区間あるいはその変換部分、インターフェイス部分での低遅延化を通じて、超低遅延性をエンドツーエンドで実現するための技術の開発                                                                                            |

| オープンソースソフトウェア技術（柔軟性・低コスト）          | アプリケーション毎のスライシング、低消費電力化、完全SDN化、MEC統合などの柔軟な制御の実現とポスト5G後半におけるローカル5Gの更なる普及や次の世代に向けて、安価に構築可能なオープンソースをベースとしたコアネットワークソフトウェア技術等の開発                                                                      |

| セキュア通信技術（超安全性）                     | 量子コンピュータ等の新原理の高速計算機でも破ることができない、堅牢性が高くセキュアな大容量通信を実現可能な量子暗号通信に資する小型チップ技術の開発、機密度の高い情報やプライバシー情報等を端末・エッジ、MEC等に留めながら求められる各種計算処理（例えばAIモデル学習）を可能とするデータの最適配置やエッジ処理によるセキュリティ技術の開発                          |

| クラウドサーバーやMECサーバーの低消費電力化技術（超低消費電力性） | クラウドやMECサーバーにおけるビット当たりのエネルギー効率を飛躍的に向上するコンピューティングアーキテクチャの開発、当該アーキテクチャを利用してAI主導のオペレーションを実現する高度な知性ネットワークの開発                                                                                         |

#### (b) 伝送路関連技術

ポスト5G後半以降の伝送路において、5Gの10倍あるいは100倍の高速化・大容量化・低遅延化・多数同時接続等を実現するためには、必然的に更なる大容量かつ高速な伝送技術が求められる。データ容量が増加するだけでなく、産業用途向けの低遅延性もミリ秒からマイクロ秒オーダーの精度が求められ、エンドツーエンドでの性能要求を担保するには伝送路における高速大容量かつ低遅延の通信の実現が重要となる。このため光伝送の更なる高速化、あるいは高速無線リンクの活用などの新たな伝送技術の開発が望まれる。

これらに対応すべく、本開発項目では、フロントホールに対応した大容量かつ低消費電力な光リンク技術、M E Cの情報処理性能を飛躍的に向上する光インターフェクト技術、メトロ・長距離網向け光伝送ネットワークの広帯域化技術の開発を行う。

| 開発対象                           | 開発技術例                                                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| フロントホール<br>(R U、D U間) 向け光リンク技術 | 大容量 (1アレイ・1波長あたり 1 T b p s 級以上) ・低消費電力・低コストなレーザー素子と素子のアレイ化技術の開発、並びにそのフロントホール向け光ファイバ伝送性能の検証                                                                                   |

| M E C内通信向け光インターフェクト技術          | M E Cの情報処理性能を飛躍的に向上させるためにプロセッサが実装される電子基板に光インターフェクトを一体的に集積し、M E Cに搭載される光トランシーバとプロセッサ間等の通信の光化及び大容量化 (10 T b p s 級) を省電力で実現可能とする光電子融合型集積技術の開発                                   |

| メトロ・長距離網向け光伝送ネットワークの大容量化技術     | 既存の波長帯域用の光送受信機や波長合分波器をそのまま活用しつつ光伝送の大容量化を実現するための波長の一括変換技術や先端的な波長、空間多重技術、システム技術等により伝送容量を低消費電力、低コストで数倍に拡大するメトロ・長距離網の大容量化技術の開発                                                   |

| 光アクセスネットワークの仮想化技術              | R A Nの基地局装置 (無線部、制御部) と仮想化対応の光伝送装置が連動してスライスを構築し、サービス利用状況の変動に追従して動的に資源連携制御する技術や、多用なサービス毎に求められる品質レベル (大容量、低遅延、多数接続) を踏まえ、トラフィック状況の学習と最適な資源予測により多様なサービスの品質の維持を可能とする動的スライス構築制御技術 |

### (c) 基地局関連技術

ポスト 5 G後半以降の基地局においては、さらなる高速大容量通信が加速され、ミリ波のみならずテラヘルツ波を含む高周波かつ広帯域の電波利用が検討されている。しかし、その高周波の特性による直進性や伝搬損失の大きさなどの課題が存在し、基地局においては集積回路等のデバイス・材料レベルでの革新的な技術が求められる。これと並行し、コアネットワークにおいて先行している仮想化技術は、無線アクセスネットワークのC U、D UのみならずR Uへと拡張することが予想される。

これらに対応すべく、本開発項目では、ミリ波・テラヘルツ帯の基地局に搭載可能な新規のアンテナ技術やビームフォーミング技術、高周波や高速大容量伝送時に低損失な新規基板材料、R F - I C等の集積回路技術、信号増幅器技術、多数同時接続時の通信品質向上技術の開発を行う。また、ソフトウェア基地局の自動最適化技術、C U・D U・R Uを含めた基地局の仮想化、柔軟化に関する研究開発も実施する。

| 開発対象               | 開発技術例                                                                                                                      |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| 新規アンテナ技術           | 高周波 (ミリ波・テラヘルツ帯) の高精度計測に基づく、メタマテリアル等新規材料を用いたミリ波・テラヘルツ帯向けのアレイアンテナや反射板の設計・製造技術の開発及び新規アンテナの性能検証、ビームフォーミングアンテナの小型化・低消費電力化技術の開発 |

| ミリ波・テラヘルツ帯向け集積回路技術 | ミリ波・テラヘルツ帯向けシリコン集積回路の高精度設計・評価技術の開発と動作検証、超低ノイズの広帯域発振器、超高速送受信機、評価技術の開発                                                       |

| 新規基板材料等の高機能材料技術    | ミリ波・テラヘルツ帯の情報通信機器向けの低誘電率かつ低損失な次世代電子基板材料等、高機能材料技術の開発                                                                        |

| 基地局増幅器のための広帯域化回路技術 | 4 G、5 G、さらには5 Gの次の通信世代で想定される広い周波数帯域をカバーすることが可能な基地局信号増幅器の広帯域化技術 (従来比で数十倍) の開発、及び多数同時接続時の通信品質向上技術の開発                         |

| ソフトウェア基地局の自動最適化技術  | 基地局ソフトウェアの一部機能のHWアクセラレータ化に際して、各アクセラレータの種別や用途に最適となるようソフトウェア等を自                                                              |

|               |                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| 術             | 動的に変更する技術、異種ハードウェア混合システム（C P U、D S P、F P G A、A S S P等）において各HW要素に最適な機能分割を実現する自動最適化技術、基地局システムの能力を可視化する技術          |

| 基地局の仮想化、柔軟化技術 | 仮想化ソフトウェア基地局設備についてキャリア5 Gとローカル5 Gとで共用すること等により低コスト化を可能とする技術、ローカル5 Gにおいて単一のコアで異なるベンダーの基地局を管理・制御する技術やR Uの広帯域化技術の開発 |

(d) 革新的応用システム技術

ポスト5 G後半以降、産業のスマート化、物流、建築、農業、健康・医療、教育、遠隔オフィス等、様々な分野で5 Gや5 Gの次の通信世代の利用を広げ、有効性を実感してもらうためには、新しく独創性に富む応用システム（アプリケーション）のユースケース開拓・拡大を進めることが重要となる。産業用途を鑑みると、低遅延・多数同時接続及び複数情報の同期技術などの性能要求がさらに高まり、ポスト5 Gや5 Gの次の通信世代の通信システムのインフラのみならず、そのシステム上でエンドツーエンド通信を行うエッジ端末や応用システムも含めて開発し性能を担保する必要がある。一方、ポスト5 Gや5 Gの次の通信世代をさまざまな産業に普及させるためには、教師無し学習など新たなA I技術を適用した自律的なネットワークの保守・運用技術の開発により、導入の敷居を下げる必要がある。

これらに対応すべく、本開発項目では、ポスト5 G後半以降の情報通信システムを活用することにより新規に創出されるユースケースを特定し、エンドツーエンドで求められるエッジ端末や応用システム等における課題を明確化し、その課題を解決する技術を開発する。

| 開発対象                           | 開発技術例                                                                                                                                                     |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| デジタルツイン実現のための高精度測位・同期制御技術      | 無線電波の到達時間差解析や画像等の高速解析による工場内での多数の機器・モノ・人等の3次元センチメートル単位測位や各種モビリティ（自動車、鉄道、ドローン等）の位置測位によりデジタルツインを実現する技術及びミリ秒単位での高精度なリアルタイム機器制御技術の開発                           |

| ME C利用によるアダプティブロボット群リアルタイム制御技術 | ロボットにセンサ・アクチュエータ等の機能のみを残し、それ以外の機能をME Cへ集約し、大容量・高速通信を介してロボットの位置・状態の認識、各ロボット及びロボット群の最適化制御を行う等、無線によりロボット群をリアルタイムに遠隔制御する技術の開発                                 |

| その他の革新的応用システム技術                | 産業のスマート化、物流、建築、農業、健康・医療、教育、娯楽、遠隔オフィス等の分野において、ポスト5 G後半以降の情報通信システムにより新規のユースケースを創出するための基盤となる革新的な応用システム技術の開発（現状技術の組み合わせや実証のみの開発は対象外。広範なシステムに応用可能な技術開発を対象とする。） |

(e) ME C関連技術

ポスト5 Gネットワークの低遅延性・多数同時接続とI o T、A I等の活用により多様な産業活動や国民生活のスマート化が期待されている。このうち、低遅延性を実現するためには、これまでのデータ集約・処理型のクラウドサーバーに加えて、基地局制御部や5 Gコアネットワークの設置場所等、よりユーザーに近いエリアでのデータ処理を可能とするME Cサーバーの普及が求められる。また、低遅延ネットワークを実現するためには、ME C、ネットワーク構成機器、ME Cと情報通信するエッジデバイス自体の高性能化も求められる。これらの取組を進めることによりデータの伝送距離の短縮、伝送量削減による低消費電力化が期待される。

このため、本開発項目では、ポスト5 G後半以降のさらなる低遅延かつ低消費電力な情報通信システムを実現するため、ME Cのみならず、ネットワーク構成機器、M

ECと情報通信するエッジデバイス自体の低遅延化、高性能・低消費電力化に係る技術について以下の開発を行う。

| 開発対象                                   | 開発技術例                                                                                                                           |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| MECを構成する半導体、周辺デバイス等の高性能化・低遅延化          | MEC向け半導体、周辺デバイス等の高性能化・低遅延化に係る設計技術、MEC・クラウドサーバー向け高速な読み出し書き込みを実現する広帯域、低遅延、大容量なメモリモジュール設計技術                                        |

| MEC内通信向け光インターフェクト技術【再掲】                | MECの情報処理性能を飛躍的に向上させるためにプロセッサが実装される電子基板に光インターフェクトを一体的に集積し、MECに搭載される光トランシーバとプロセッサ間等の通信の光化及び大容量化(10Tbps級)を省電力で実現可能とする光電子融合型集積技術の開発 |

| クラウドサーバーやMECサーバーの低消費電力化技術(超低消費電力性)【再掲】 | クラウドやMECサーバーにおけるビット当たりのエネルギー効率を飛躍的に向上するコンピューティングアーキテクチャの開発、当該アーキテクチャを利用してAI主導のオペレーションを実現する高度な知性ネットワークの開発                        |

| MEC利用によるアダプティブロボット群リアルタイム制御技術【再掲】      | ロボットにセンサ・アクチュエータ等の機能のみを残し、それ以外の機能をMECへ集約し、大容量・高速通信を介してロボットの位置・状態の認識、各ロボット及びロボット群の最適化制御を行う等、無線によりロボット群をリアルタイムに遠隔制御する技術の開発        |

上記(a)～(e)とともに付随する周辺技術を合わせて開発することや、上記と同等レベル以上に重要な技術の開発があれば、追加的に実施可能とする。

研究開発項目②(助成)に関係する具体的な開発テーマとして想定する開発技術は、ポスト5Gの後半以降に有望と考えられる(a)～(b)の技術のうち、特に新規開発や大幅な性能向上が必要となる技術に関する先導的な研究開発やの探索型開発に取り組む。これら開発テーマ毎に記載の開発対象及び開発技術例の全てあるいは一部について研究開発を行う。本研究開発項目では、研究開発終了時点において、実用化を前提とした研究開発への移行に向けた根拠データの取得等により、技術の確立の見通しを付けることを開発目標とする。また、開発対象はポスト5G後半以降にかけて先端半導体製造技術に適用され、一定の市場シェアを獲得するポテンシャルを有し、我が国の国民生活や経済、産業等への波及効果が期待される技術とする。

#### (a) 先端半導体製造技術(前工程技術)