## 本ワーキンググループでの技術・人材ロードマップの策定において留意すべき事項

東京工業大学大学院イノベーションマネジメント研究科 梶川裕矢

### 1. 國際的な視点に基づくロードマッピング

技術・人材ロードマップの策定にあたっては、学術的注目度を出発点に構成するのではなく、社会的課題を出発点とすべきであるものの、当該分野における国際的な研究開発の動向、叡知の営みとしての学術に対する国際的な貢献、産業界における動向や事業展開戦略に留意しながらロードマップを策定すべきである。

### 2. 手段の正当化でなく、目標の提示

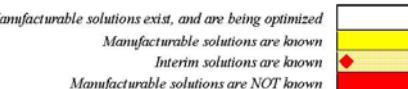

社会的課題を出発点とするのであれば、策定されるロードマップの項目は、「△△炉の開発」や「××の実施」といった「手段」ならびにそれらへの公的投資の正当化や政策的実現を志向するのではなく、社会的課題に対する認識に基づいた研究開発目標を提示することですることで、原子力の自主的・継続的な安全性向上という政策目標の実現を図るべきである。ロードマップの成功例としてしばしば言及される国際半導体技術ロードマップ(ITRS)では、技術的な難易度に応じて、技術ロードマップ上に「白」(既存技術の延長上で実現可能である)、「黄色」(産業技術としての解決策は知られているが現在最適化の途上にある)、「赤色」(産業技術として有効な解決手法が知られていない)という色分けが成されている。ITRSは目標を明示化することで、技術開発・研究開発投資の誘因として機能し、結果として、ITRSが提示した数値目標が前倒で実現出来ている。

### 3. 原子炉の導入主体のコミットメントまたはロードマップの策定主体の明確化

策定したロードマップを形式的なものに留まらせるのではなく、実質的に機能させるためには、導入主体として想定される企業や、地方政府や各國政府のコミットメント、開発主体となる企業や大学、公的研究機関や規制官庁といった適切なステークホルダーの参加が有効である。ITRSでは、目標値を達成した装置をインテルが調達することにより、ロードマップが現実性のあるものとして機能した。技術ロードマップの策定にあたってはこのような導入主体のコミットメントがあることが望ましい。少なくともロードマップの策定主体が明確化されるべきであり、安全性に関する信頼性の高い学術的知見の活用や、ロードマッピングの過程における適切なステークホルダーの関与が必要である。

以上を技術・人材ロードマップの策定に対する意見ではなく、本ワーキンググループの構成員ならびに事務局への要望として提出する。当然のことながら私も一構成員として上記の実現に向けて努力する所存である。ご検討下さい。

<梶川委員提出資料>

添付資料

Lithography 5

**TECHNOLOGY REQUIREMENTS**

*Table 76a Lithography Technology Requirements—Near-term Years*

| Year of Production                                             | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 |

|----------------------------------------------------------------|------|------|------|------|------|------|------|------|------|

| DRAM $\frac{1}{2}$ pitch (nm) (contacted)                      | 80   | 70   | 65   | 57   | 50   | 45   | 40   | 36   | 32   |

| <i>DRAM and Flash</i>                                          |      |      |      |      |      |      |      |      |      |

| DRAM $\frac{1}{2}$ pitch (nm)                                  | 80   | 70   | 65   | 57   | 50   | 45   | 40   | 35   | 32   |

| Flash $\frac{1}{2}$ pitch (nm) (un-contacted poly)             | 76   | 64   | 57   | 51   | 45   | 40   | 36   | 32   | 28   |

| Contact in resist (nm)                                         | 94   | 79   | 70   | 63   | 56   | 50   | 44   | 39   | 35   |

| Contact after etch (nm)                                        | 85   | 72   | 64   | 57   | 51   | 45   | 40   | 36   | 32   |

| Overlay [A] (3 sigma) (nm)                                     | ◆15  | ◆13  | ◆11  | 10   | 9    | 8    | 7.1  | 6.4  | 5.7  |

| CD control (3 sigma) (nm) [B]                                  | 8.8  | 7.4  | 6.6  | 5.9  | 5.3  | 4.7  | 4.2  | 3.7  | 3.3  |

| <i>MPU</i>                                                     |      |      |      |      |      |      |      |      |      |

| MPU/ASIC Metal 1 (M1) $\frac{1}{2}$ pitch (nm)                 | 90   | 78   | 68   | 59   | 52   | 45   | 40   | 36   | 32   |

| MPU gate in resist (nm)                                        | 54   | 48   | 42   | 38   | 34   | 30   | 27   | 24   | 21   |

| MPU physical gate length (nm) *                                | 32   | 28   | 25   | 23   | 20   | 18   | 16   | 14   | 13   |

| Contact in resist (nm)                                         | 111  | 97   | 84   | 73   | 64   | 56   | 50   | 44   | 39   |

| Contact after etch (nm)                                        | 101  | 88   | 77   | 67   | 58   | 51   | 45   | 40   | 36   |

| Gate CD control (3 sigma) (nm) [B] **                          | ◆3.3 | ◆2.9 | 2.6  | 2.3  | 2.1  | 1.9  | 1.7  | 1.5  | 1.3  |

| MPU/ASIC Metal 1 (M1) $\frac{1}{2}$ pitch (nm)                 | 90   | 78   | 68   | 59   | 52   | 45   | 40   | 36   | 32   |

| Chip size (mm <sup>2</sup> )                                   |      |      |      |      |      |      |      |      |      |

| Maximum exposure field height (mm)                             | 26   | 26   | 26   | 26   | 26   | 26   | 26   | 26   | 26   |

| Maximum exposure field length (mm)                             | 33   | 33   | 33   | 33   | 33   | 33   | 33   | 33   | 33   |

| Maximum field area printed by exposure tool (mm <sup>2</sup> ) | 858  | 858  | 858  | 858  | 858  | 858  | 858  | 858  | 858  |

| Number of mask levels MPU                                      | 33   | 33   | 33   | 35   | 35   | 35   | 35   | 35   | 35   |

| Number of mask levels DRAM                                     | 24   | 24   | 24   | 24   | 24   | 26   | 26   | 26   | 26   |

| Wafer size (diameter mm)                                       | 300  | 300  | 300  | 300  | 300  | 300  | 300  | 450  | 450  |

\* MPU physical gate length numbers and colors are determined by several working groups and the ORTC.

\*\* Noted exception for R&D in next three years: Solution NOT known, but does not prevent production manufacturing.

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2006 UPDATE

<出典： The International Technology Roadmap for Semiconductors: 2006 Update, Lithography, p5>