半導体デバイス工場におけるOTセキュリティガイドライン

概要

1. 背景・経緯

サイバー攻撃はますます多様化・高度化しており、多くの制御装置等が攻撃され、工場における生産が停止する等の被害が発生しています。また、各種の開発機密(知的財産)がサイバー攻撃によって流出する危険も増しており、半導体産業の経済及び安全保障上の重要性や足下でのサイバー脅威・リスクの高まりを踏まえると、高度なサイバー攻撃への対応を含めたセキュリティ対策を進めていく必要があります。

国外では、国際的な半導体関連の業界団体であるSEMIにより、半導体製造装置に係るE187/E188規格が策定され、また、米国立標準技術研究所(NIST)においてもCybersecurity Framework 2.0(NIST CSF 2.0)について、半導体製造プロファイルの策定が進められています。

一方、我が国では、経済産業省が2022年に汎用的な組立型の工場を対象とした「工場システムにおけるサイバー・フィジカル・セキュリティ対策ガイドライン」を策定し公表していますが、一般的にプロセスオートメーション型の工場であり、工場の規模が大きく、汎用OSを用いた製造装置の台数が多い等の特徴を有する半導体工場には、当該ガイドラインがなじまないといった実態があります。

こうした課題意識の下、経済産業省では、2024年11月より産業サイバーセキュリティ研究会の下で半導体産業サブワーキンググループ(座長:東京大学 江崎教授)を開催し、半導体デバイスメーカーや半導体製造装置メーカーを含めた国内外の様々な企業・団体関係者を交えて、我が国の半導体デバイス工場における制御システム(OT)のセキュリティ対策のあり方について議論を進め、国際的な半導体産業における各種セキュリティ規格とも整合した、半導体デバイス工場向けの工場セキュリティ対策の指針である「半導体デバイス工場におけるOTセキュリティガイドライン(案)」日本語版・英語版の双方を取りまとめました。その後、当該ガイドライン案について、同年6月27日から8月26日に実施した意見公募で頂いた御意見を踏まえ必要な修正を行い、今般、成案化しました。

2.半導体デバイス工場におけるOTセキュリティガイドラインの概要

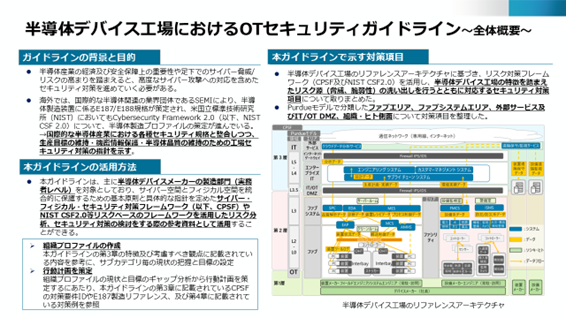

「半導体デバイス工場におけるOTセキュリティガイドライン」(以下「本ガイドライン」といいます。)は、主として半導体デバイスメーカーの製造部門(実務者レベル)向けに、「生産目標の維持」、「機密情報の保護」、「半導体品質の維持」を守るべき対象として、最も高度な攻撃者(国家の支援を受けたグループ(APT))を想定した対策レベルを実現するために必要な工場セキュリティ対策の指針を示すものです。当該セキュリティ対策指針は、上述したE187/E188やNIST CSF 2.0などの各種セキュリティ規格と整合しています。

本ガイドラインは、工場のセキュリティ対策を進めるための一般的なプロセスにおいて、リスクベースのサイバーセキュリティフレームワーク(サイバー・フィジカル・セキュリティ対策フレームワーク(CPSF)及びNIST CSF2.0)を活用したリスク分析や、具体的な対策を検討する際などに活用されることが想定されます。

本ガイドラインで示す対策項目としては、大きく以下の2点です。

- 半導体デバイス工場のリファレンスアーキテクチャに基づき、リスク対策フレームワーク(CPSF及びNIST CSF2.0)を活用して洗い出された、半導体デバイス工場の特徴を踏まえたリスク源(脅威、脆弱性)に対応するセキュリティ対策項目

- Purdueモデルで分類したファブエリア、ファブシステムエリア、外部サービス及びIT/OT DMZ、組織・ヒト側面についての対策項目

今後、経済産業省の投資促進関連施策の要件等に対する本ガイドラインで示すセキュリティ対策基準の紐付け等について検討していく予定です。

- 1. 本ガイドライン作成の背景と目的

- 1.1. 背景と目的

- 1.2. ガイドラインの対象者(想定読者)

- 1.3. 半導体製造においてサイバー攻撃から守るべき対象

- 1.4. 半導体製造工程における脅威とリスク

- 1.5. 想定する攻撃主体

- 1.6. 半導体デバイス工場におけるセキュリティ対策と本ガイドラインの利活用

- 1.7. ガイドラインの構成

- 2. 半導体デバイス工場におけるリファレンスアーキテクチャ

- 2.1. 半導体デバイス工場のリファレンスアーキテクチャ

- 2.2. Purdueモデルの活用

- 2.3. CPSF三層構造の活用

- 3. 半導体デバイス工場の特徴とリスク源及び関連フレームワークの対策項目の整理

- 3.1. リファレンスアーキテクチャを活用したセキュリティ対策項目への整理

- 3.2. 半導体デバイス工場の技術・物理的側面におけるOT領域各エリア別のリスク分析のための情報

- 3.2.1.OT領域ファブエリアのリスク分析のための情報

- 3.2.2.OT領域ファブシステムエリアのリスク分析のための情報

- 3.2.3.OT領域の外部サービス及びIT/OT DMZ分類制御のリスク分析のための情報

- 3.3. 半導体デバイス工場の組織・ヒト側面におけるリスク分析のための情報

- 4. 半導体デバイス工場における具体的対策例

- 4.1. 装置ツールの資産管理と脆弱性評価

- 4.1.1.資産(装置ツール)の洗い出し・構成管理の定め方

- 4.1.2.資産(装置ツール)の重要度の決め方

- 4.1.3.装置ツールの脆弱性の把握方法

- 4.1.4.装置ツールに対する脅威情報の収集方法

- 4.1.5.装置ツールに対する脆弱性評価と対策優先度の決め方

- 4.2. 装置ツールの被害の極小化と早期復旧を備えた追加防御対策

- 4.3. 運用(監視・対応・復旧・改善) - FSIRTによる運用

- 4.4. 物理アクセスの制限(入室・持込み・接続) - ファブエリアにおける物理的対策

Appendix A:NIST CSF2.0とCPSFの対応表

Appendix B:用語/略語

本ガイドラインの検討体制

関連資料

- 半導体デバイス工場におけるOTセキュリティガイドラインVer1.0

(PDF形式:8,381KB)

(PDF形式:8,381KB) - 「半導体デバイス工場におけるOTセキュリティガイドライン」概要資料

(PDF形式:3,368KB)

(PDF形式:3,368KB)

関連資料(英訳版)

- OT Security Guidelines for Semiconductor Device Factories

(PDF形式:5,023KB)

(PDF形式:5,023KB) - Summary of "OT Security Guidelines for Semiconductor Device Factories"

(PDF形式:3,070KB)

(PDF形式:3,070KB)

関連リンク

- 産業サイバーセキュリティ研究会 ワーキンググループ1 半導体産業サブワーキンググループhttps://www.meti.go.jp/shingikai/mono_info_service/sangyo_cyber/wg_seido/wg_semiconductor/index.html

- サイバー・フィジカル・セキュリティ対策フレームワーク(CPSF)とその展開

- https://www.meti.go.jp/policy/netsecurity/wg1/wg1.html

お問合せ先

電話:03-3501-1511(内線)3964

FAX:03-3580-6239